AI芯片哪家強(qiáng)?現(xiàn)在,有直接的對(duì)比與參考了。

英國(guó)一名資深芯片工程師James W. Hanlon,盤(pán)點(diǎn)了當(dāng)前十大AI訓(xùn)練芯片。

并給出了各個(gè)指標(biāo)的橫向?qū)Ρ龋彩悄壳皩?duì)AI訓(xùn)練芯片最新的討論與梳理。

其中,華為昇騰910是中國(guó)芯片廠商唯一入選的芯片,其性能如何,也在這一對(duì)比中有了展現(xiàn)。

Cerebras Wafer-Scale Engine

這一芯片于今年8月份正式面世,被稱為“史上最大AI芯片”,名為“晶圓級(jí)引擎”(Cerebras Wafer Scale Engine,簡(jiǎn)稱WSE)。

其最大的特征是將邏輯運(yùn)算、通訊和存儲(chǔ)器集成到單個(gè)硅片上,是一種專門(mén)用于深度學(xué)習(xí)的芯片。

一舉創(chuàng)下4項(xiàng)世界紀(jì)錄:

1、晶體管數(shù)量最多的運(yùn)算芯片:總共包含1.2萬(wàn)億個(gè)晶體管。雖然三星曾造出2萬(wàn)億個(gè)晶體管的芯片,卻是用于存儲(chǔ)的eUFS。

2、芯片面積最大:尺寸約20厘米×23厘米,總面積46225平方毫米。

3、片上緩存最大:包含18GB的片上SRAM存儲(chǔ)器。

4、運(yùn)算核心最多:包含410,592個(gè)處理核心

之所以能夠有如此亮眼的數(shù)據(jù),直接得益于其集成了84個(gè)高速互連的芯片,單個(gè)芯片在FP32上的峰值性能表現(xiàn)為40 Tera FLOPs,芯片功率達(dá)15千瓦,與AI集群相當(dāng)。

片上緩存也達(dá)到了18GB,是GPU緩存的3000倍;可提供每秒9PB的內(nèi)存帶寬, 比GPU快10,000倍。

晶片規(guī)模集成,并不是一個(gè)新的想法,但產(chǎn)量、功率傳輸和熱膨脹相關(guān)的問(wèn)題使其很難商業(yè)化。在這些方面,Cerebras都給出了相應(yīng)的解決辦法:

1、為了解決缺陷導(dǎo)致良率不高的問(wèn)題,Cerebras在設(shè)計(jì)的芯片時(shí)候考慮了1~1.5%的冗余,添加了額外的核心,當(dāng)某個(gè)核心出現(xiàn)問(wèn)題時(shí)將其屏蔽不用,因此有雜質(zhì)不會(huì)導(dǎo)致整個(gè)芯片報(bào)廢。

2、Cerebras與臺(tái)積電合作發(fā)明了新技術(shù),來(lái)處理具有萬(wàn)億加晶體管芯片的刻蝕和通訊問(wèn)題。

3、在芯片上方安裝了一塊“冷卻板”,使用多個(gè)垂直安裝的水管直接冷卻芯片。

Cerebras公司由Sean Lie(首席硬件架構(gòu)師)、Andrew Feldman(首席執(zhí)行官)等人于2016年創(chuàng)立。后者曾創(chuàng)建微型服務(wù)器公司SeaMicro,并以3.34億美元的價(jià)格出售給AMD。

該公司在加州有194名員工,其中包括173名工程師,迄今為止已經(jīng)從Benchmark等風(fēng)投機(jī)構(gòu)獲得了1.12億美元的投資。

Google TPU(v1、v2、v3)

Google TPU系列芯片正式發(fā)布于2016年,第一代芯片TPU v1只用于推理,而且只支持整數(shù)運(yùn)算。

通過(guò)在PCIe-3之間發(fā)送指令來(lái)執(zhí)行矩陣乘法和應(yīng)用激活函數(shù),從而為主機(jī)CPU提供加速,節(jié)省了大量的設(shè)計(jì)和驗(yàn)證時(shí)間。其主要數(shù)據(jù)為:

1、芯片面積331平方毫米,28nm制程

2、頻率為700 MHz,功耗28-40W

3、片上存儲(chǔ)為28 MB SRAM:24MB 用于激活,4MB 用于累加器

4、芯片面積比例:35%用于內(nèi)存,24%用于矩陣乘法單元,剩下的41%面積用于邏輯。

5、256x256x8b收縮矩陣乘法單元(64K MACs/cycle)

6、Int8和 INT16算法(峰值分別為92和23 TOPs/s)

IO數(shù)據(jù):

可以通過(guò)兩個(gè)接口訪問(wèn)8 GB DDR3-2133 DRAM,速度為34 GB/s

1、PCIe-3x16 (14 GBps)

2017年5月,Google TPU v2發(fā)布,改進(jìn)了TPU v1的浮點(diǎn)運(yùn)算能力,并增強(qiáng)了其內(nèi)存容量、帶寬以及HBM 集成內(nèi)存,不僅能夠用于推理,也能夠用于訓(xùn)練。其單個(gè)芯片的數(shù)據(jù)如下:

2、20nm制程,功耗在200-250W(推測(cè))

3、BFloat16上性能表現(xiàn)為45 TFLOPs,也支持 FP32

4、具有標(biāo)量和矩陣單元的雙核

5、集成4塊芯片后,峰值性能為180 TFLOPs

單核數(shù)據(jù):

1、128x128x32b收縮矩陣單元(MXU)

2、8GB專用HBM,接入帶寬300 GBps

3、BFloat16上的最大吞吐量為22.5 TFLOPs

IO數(shù)據(jù):

4、16Gb HBM集成內(nèi)存,600 GBps帶寬(推測(cè))

5、PCIe-3 x8 (8 GBps)

6、Google TPU v2發(fā)布一年之后,Google再度發(fā)布新版芯片——TPU v3。

但關(guān)于TPU v3的細(xì)節(jié)很少,很可能只是對(duì)TPU v2一個(gè)漸進(jìn)式改版,性能表現(xiàn)翻倍,增加了HBM2內(nèi)存使容量和帶寬翻倍。其單個(gè)芯片的數(shù)據(jù)如下:

1、16nm或12nm制程,功耗估計(jì)在200W

2、BFloat16的性能為105 TFLOPs,可能是MXUs的2倍到4倍

3、每個(gè)MXU都能訪問(wèn)8GB的專用內(nèi)存

4、集成4個(gè)芯片后,峰值性能420 TFLOPs

IO數(shù)據(jù):

32GB的HBM2集成內(nèi)存,帶寬為1200GBps (推測(cè))

PCIe-3 x8 (8 GBps)(推測(cè))

Graphcore IPU

Graphcore成立于成立于2016年,不僅備受資本和業(yè)界巨頭的青睞,還頗受業(yè)內(nèi)大佬的認(rèn)可。

2018年12月,宣布完成2億美元的D輪融資,估值17億美元。投資方有寶馬、微軟等業(yè)界巨頭,還有著名的風(fēng)投公司Sofina、Atomico等。

AI巨頭Hinton、DeepMind創(chuàng)始人哈薩比斯,都直接表達(dá)了贊美。

Graphcore IPU是這家公司的明星產(chǎn)品,其架構(gòu)與大量具有小內(nèi)存的簡(jiǎn)單處理器高度并行,通過(guò)一個(gè)高帶寬的“交換”互連連接在一起。

其架構(gòu)在一個(gè)大容量同步并行(BSP)模型下運(yùn)行,程序的執(zhí)行按照一系列計(jì)算和交換階段進(jìn)行。同步用于確保所有進(jìn)程準(zhǔn)備好開(kāi)始交換。

- BSP模型是一個(gè)強(qiáng)大的編程抽象,用于排除并發(fā)性風(fēng)險(xiǎn),并且BSP的執(zhí)行,允許計(jì)算和交換階段充分利用芯片的能源,從而更好地控制功耗。可以通過(guò)鏈接10個(gè)IPU間鏈路來(lái)建立更大的IPU芯片系統(tǒng)。其核心數(shù)據(jù)如下:

- 16nm制程,236億個(gè)晶體管,芯片面積大約為800平方毫米,功耗為150W,PCIe卡為300 W

- 1216個(gè)處理器,在FP32累加的情況下,F(xiàn)P16算法峰值達(dá)到125 TFLOPs

- 分布在處理器核心之間有300 MB的片上內(nèi)存,提供45 TBps的總訪問(wèn)帶寬

- 所有的模型狀態(tài)保存在芯片上,沒(méi)有直接連接DRAM

IO數(shù)據(jù):

- 2x PCIe-4的主機(jī)傳輸鏈接

- 10倍的卡間IPU鏈接

- 共384GBps的傳輸帶寬

單核數(shù)據(jù):

- 1、混合精度浮點(diǎn)隨機(jī)算法

- 2、最多運(yùn)行六個(gè)線程

Habana Labs Gaudi

Habana Labs同樣成立于2016年,是一家以色列AI芯片公司。

2018年11月,完成7500萬(wàn)美元的B輪募資,總募資約1.2億美元。

Gaudi芯片于今年6月亮相,直接對(duì)標(biāo)英偉達(dá)的V100。

其整體的設(shè)計(jì),與GPU也有相似之處,尤其是更多的SIMD并行性和HBM2內(nèi)存。

芯片集成了10個(gè)100G 以太網(wǎng)鏈路,支持遠(yuǎn)程直接內(nèi)存訪問(wèn)(RDMA)。與英偉達(dá)的NVLink或OpenCAPI相比,這種數(shù)據(jù)傳輸功能允許使用商用網(wǎng)絡(luò)設(shè)備構(gòu)建大型系統(tǒng)。其核心數(shù)據(jù)如下:

- TSMC 16 nm制程(CoWoS工藝),芯片尺寸大約為500平方毫米

- 異構(gòu)架構(gòu):GEMM操作引擎、8個(gè)張量處理核(TPCs)

- SRAM內(nèi)存共享

- PCIe卡功耗為200W,夾層卡為300W

- 片上內(nèi)存未知

TPC核心數(shù)據(jù):

- VLIW SIMD并行性和一個(gè)本地SRAM內(nèi)存

- 支持混合精度運(yùn)算:FP32、 BF16,以及整數(shù)格式運(yùn)算(INT32、INT16、INT8、UINT32、UINT8)

- 隨機(jī)數(shù)生成、超越函數(shù):Sigmoid、Tanh、GeLU

IO數(shù)據(jù):

- 4x 提供32 GB的HBM2-2000 DRAM 堆棧, 整體達(dá)1 TBps

- 芯片上集成10x 100GbE 接口,支持融合以太網(wǎng)上的 RDMA (RoCE v2)

- PCIe-4 x16主機(jī)接口

Huawei Ascend 910

華為昇騰910,同樣直接對(duì)標(biāo)英偉達(dá)V100,于今年8月份正式商用,號(hào)稱業(yè)內(nèi)算力最強(qiáng)的AI訓(xùn)練芯片。主打深度學(xué)習(xí)的訓(xùn)練場(chǎng)景,主要客戶面向AI數(shù)據(jù)科學(xué)家和工程師。

其核心數(shù)據(jù)為:

- 7nm+EUV工藝,456平方毫米

- 集成4個(gè)96平方毫米的 HBM2棧和 Nimbus IO處理器芯片

- 32個(gè)達(dá)芬奇內(nèi)核

- FP16性能峰值256TFLOPs (32x4096x2) ,是 INT8的兩倍

- 32 MB的片上 SRAM (L2緩存)

- 功耗350W

互聯(lián)和IO數(shù)據(jù):

- 內(nèi)核在6 x 4的2d網(wǎng)格封包交換網(wǎng)路中相互連接,每個(gè)內(nèi)核提供128 GBps 的雙向帶寬

- 4 TBps的L2緩存訪問(wèn)

- 1.2 TBps HBM2接入帶寬

- 3x30GBps 芯片內(nèi)部 IOs

- 2 x 25 GBps RoCE 網(wǎng)絡(luò)接口

單個(gè)達(dá)芬奇內(nèi)核數(shù)據(jù):

- 3D 16x16x16矩陣乘法單元,提供4,096個(gè) FP16 MACs 和8,192個(gè) INT8 MACs

- 針對(duì) FP32(x64)、 FP16(x128)和 INT8(x256)的2,048位 SIMD 向量運(yùn)算

- 支持標(biāo)量操作

- Intel NNP-T

這是Xeon Phi之后,英特爾再次進(jìn)軍AI訓(xùn)練芯片,歷時(shí)4年,壕購(gòu)4家創(chuàng)業(yè)公司,花費(fèi)超過(guò)5億美元,在今年8月份發(fā)布。

神經(jīng)網(wǎng)絡(luò)訓(xùn)練處理器NNP-T中的“T”指Train,也就是說(shuō)這款芯片用于AI推理,處理器代號(hào)為Spring Crest。

NNP-T將由英特爾的競(jìng)爭(zhēng)對(duì)手臺(tái)積電(TSMC)制造,采用16nm FF+工藝。

NNP-T有270億個(gè)16nm晶體管,硅片面積680平方毫米,60mmx60mm 2.5D封裝,包含24個(gè)張量處理器組成的網(wǎng)格。

核心頻率最高可達(dá)1.1GHz,60MB片上存儲(chǔ)器,4個(gè)8GB的HBM2-2000內(nèi)存,它使用x16 PCIe 4接口,TDP為150~250W。

每個(gè)張量處理單元都有一個(gè)微控制器,用于指導(dǎo)是數(shù)學(xué)協(xié)處理器的運(yùn)算,還可以通過(guò)定制的微控制器指令進(jìn)行擴(kuò)展。

NNP-T支持3大主流機(jī)器學(xué)習(xí)框架:TensorFlow、PyTorch、PaddlePaddle,還支持C++ 深度學(xué)習(xí)軟件庫(kù)、編譯器nGraph。

在算力方面,芯片最高可以達(dá)到每秒119萬(wàn)億次操作(119TOPS),但是英特爾并未透露是在INT8還是INT4上的算力。

作為對(duì)比,英偉達(dá)Tesla T4在INT8上算力為130TOPS,在INT4上為260TOPS。

英偉達(dá)Volta架構(gòu)芯片

英偉達(dá)Volta,2017年5月公布,從 Pascal 架構(gòu)中引入了張量核、 HBM2和 NVLink 2.0。

- 英偉達(dá)V100芯片就是基于此架構(gòu)的首款GPU芯片,其核心數(shù)據(jù)為:

- TSMC 12nm FFN工藝,211億個(gè)晶體管,面積為815平方毫米

- 功耗為300W,6 MB L2緩存

- 84個(gè)SM,每個(gè)包含:64個(gè) FP32 CUDA 核,32個(gè) FP64 CUDA 核和8個(gè)張量核(5376個(gè) FP32核,2688個(gè) FP64核,672個(gè) TCs)。

- 單個(gè)Tensor Core每時(shí)鐘執(zhí)行64個(gè)FMA操作(總共128 FLOPS),每個(gè)SM具有8個(gè)這樣的內(nèi)核,每個(gè)SM每個(gè)時(shí)鐘1024個(gè)FLOPS。

- 相比之下,即使采用純FP16操作,SM中的標(biāo)準(zhǔn)CUDA內(nèi)核只能在每個(gè)時(shí)鐘產(chǎn)生256個(gè)FLOPS。

- 每個(gè)SM,128 KB L1數(shù)據(jù)緩存 / 共享內(nèi)存和4個(gè)16K 32位寄存器。

IO數(shù)據(jù):

- 32 GB HBM2 DRAM,900 GBps帶寬

- 300 GBps的NVLink 2.0

英偉達(dá)Turing架構(gòu)芯片

Turing架構(gòu)是對(duì)Volta架構(gòu)的升級(jí),于2018年9月發(fā)布,但 CUDA 和張量核更少。

因此,它的尺寸更小,功率也更低。除了機(jī)器學(xué)習(xí)任務(wù),它還被設(shè)計(jì)用來(lái)執(zhí)行實(shí)時(shí)射線追蹤。其核心數(shù)據(jù)為:

- TSMC 12nm FFN工藝,面積為754平方毫米,186億個(gè)晶體管,功耗260W

- 72個(gè)SM,每個(gè)包含:64個(gè) FP32核,64個(gè) INT32核,8個(gè)張量核(4608個(gè) FP32核,4608個(gè) INT32核和576個(gè) TCs)

- 帶有boost時(shí)鐘的峰值性能:FP32上為16.3 TFLOPs、FP16上為130.5 TFLOPs、INT8上為261 TFLOPs、INT4上為522 TFLOPs

- 片上內(nèi)存為24.5 MB,在6MB的 L2緩存和256KB 的 SM 寄存器文件之間

- 基準(zhǔn)時(shí)鐘為1455 MHz

IO數(shù)據(jù):

- 12x32位 GDDR6存儲(chǔ)器,提供672 GBps 聚合帶寬

- 2x NVLink x8鏈接,每個(gè)鏈接提供多達(dá)26 GBps 的雙向速度

本文來(lái)自轉(zhuǎn)載自公眾號(hào)「QbitAI」和「量子位」,本文作為轉(zhuǎn)載分享。

-

Google

+關(guān)注

關(guān)注

5文章

1758瀏覽量

57418 -

gpu

+關(guān)注

關(guān)注

28文章

4703瀏覽量

128729 -

昇騰910

+關(guān)注

關(guān)注

0文章

14瀏覽量

6783

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

谷東科技民航維修智能決策大模型榮獲華為昇騰技術(shù)認(rèn)證

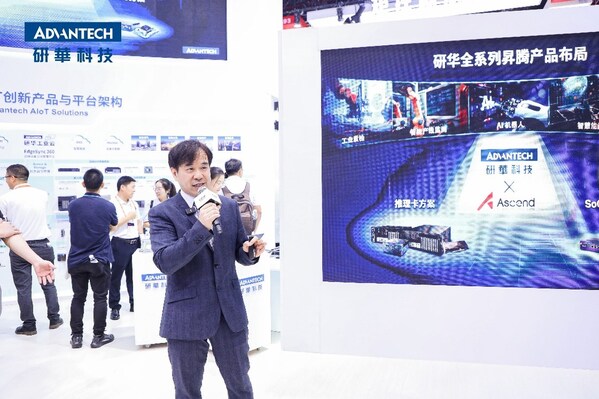

研華發(fā)布高性能工業(yè)邊緣 AI 算力方案 攜手昇騰引領(lǐng)邊緣 AI 革新

中軟國(guó)際榮膺華為昇騰萬(wàn)里伙伴計(jì)劃認(rèn)證級(jí)應(yīng)用軟件伙伴證書(shū)

昇騰與昇思原生,助力智譜打造自主創(chuàng)新大模型體系!

華為云昇騰AI云服務(wù)可適配100多個(gè)大模型

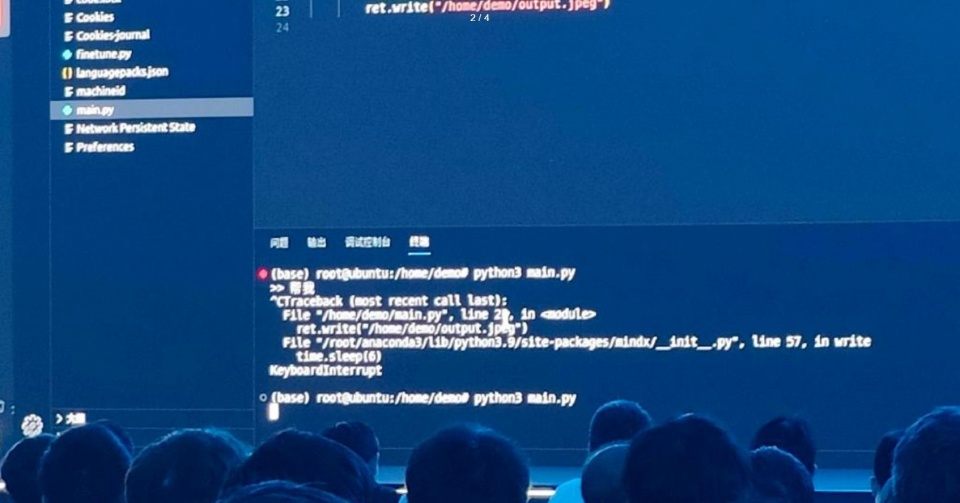

華為發(fā)布會(huì)大模型翻車(chē)?昇騰社區(qū)回應(yīng)!

潤(rùn)和軟件基于華為昇騰AI所打造的IntelliCore AI解決方案一體機(jī)

格靈深瞳受邀參加華為中國(guó)合作伙伴大會(huì),榮獲“昇騰突出貢獻(xiàn)獎(jiǎng)”

臺(tái)積電重回全球十大上市公司

中國(guó)科學(xué)十大進(jìn)展!華為云盤(pán)古氣象大模型入選!

潤(rùn)和軟件與華為昇騰AI完成兼容性測(cè)試認(rèn)證

軟通天璇MaaS平臺(tái)2.0與華為昇騰AI完成兼容性測(cè)試認(rèn)證

迅龍軟件加入華為昇騰APN,共同推動(dòng)人工智能行穩(wěn)致遠(yuǎn)

2023中國(guó)智能制造十大科技進(jìn)展發(fā)布,這項(xiàng)傳感技術(shù)入選

香橙派聯(lián)合華為發(fā)布基于昇騰的Orange Pi AIpro開(kāi)發(fā)板 業(yè)界首款基于昇騰AI開(kāi)發(fā)板

全球十大AI訓(xùn)練芯片大盤(pán)點(diǎn):華為昇騰910是中國(guó)唯一入選

全球十大AI訓(xùn)練芯片大盤(pán)點(diǎn):華為昇騰910是中國(guó)唯一入選

評(píng)論