一、摩爾定律是一種基于統計的推測

過往集成電路的發展是摩爾定律有效印證。摩爾定律在1965年被第一次提及,其基論點為在維持最低成本的前提下,以18-24個月為一個跨度,集成電路的集成度和性能將提升一倍。我們所熟知的10nm、7nm芯片其命名方式是根據工藝節點而定的。特征尺寸(critical dimension, CD)是衡量工藝水平的技術指標,根據國際半導體技術路線圖(ITRS)的規定,工藝節點通常以晶體管的半節距(half-pitch)或柵極長度(gate length)等特征尺寸來表示。按照摩爾定律的發展規律,集成電路芯片的集成度每18-24個月翻一倍,即工藝節點以1/√2的系數逐步縮減,工藝節點越小,制造工藝越先進。從過去數十年的數據來看,集成電路的制造成本、芯片功耗和芯片性能這三大指標都沿著摩爾定律一直向前發展,因而其有效性一直得以延續。

摩爾定律形成于統計結果,是技術發展的一種合理推測。與其他科學定律不同,摩爾定律更應當被理解為經濟學規律,是由集成電路產業和技術發展所得出來的結論。在定律被提出后的一段時間里,集成電路的發展動力較為強勁,約每18個月工藝就進行一次迭代。隨著工藝節點不斷縮小,工藝的迭代速度已經有所放緩。2015年發布的國際半導體技術線路圖(ITRS)顯示,隨著集成電路尺寸不斷減小,技術瓶頸在制約工藝的發展,從2015年以來產品換代速度已下降到24個月,這個速度預計將保持到2030年。

表1 ITRS2.0報告部分技術路線圖

資料來源:ITRS

二、三大因素制約摩爾定律發展

物理效應、功耗和經濟效益成集成電路工藝發展瓶頸。集成電路性能、功耗及制造成本是評判摩爾定律是否有效的重要的標準。目前主流芯片廠商的產品已經進入到10nm以內,遵循以往的技術路徑,即按比例不斷縮小器件尺寸已無法實現摩爾定律。

從物理角度來看,集成電路尺寸已進入到介觀尺寸范圍內,各種物理效應都會成為集成電路發展的阻力,如雜質漲落、量子隧穿等。介觀物理和基于量子化的處理方法是應對這些物理效應的有效手段,但目前這些前沿技術還無法應用到量產中。

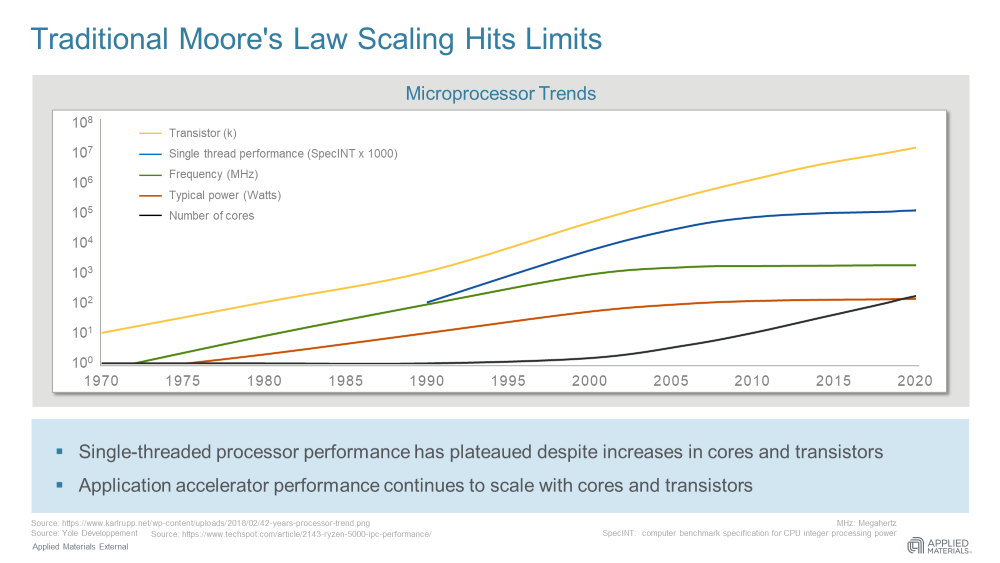

時鐘頻率是評估芯片性能的重要指標,頻率越高,芯片性能越強,但時鐘頻率提高意味著功耗隨之上升。目前每一工藝節點的演進會使芯片時間頻率有20%的提升,而功耗也以一定的幅度在增加。若保持功耗不變,即使將工藝節點不斷縮小,時鐘頻率也得不到提升,甚至在某一節點開始下降。散熱問題是功耗上升后所要面臨的一大難題,直接關系到芯片的可靠性和壽命,在工藝節點不斷縮小的情況下,探索功耗和性能的平衡點,保證芯片在合理的工作溫度運行,考驗著各大廠商。功耗成為另外一個制約集成電路發展的因素。

所有工藝和技術的最終落腳點都是利潤。從成本的角度來看,20nm成為加工成本的一個分水嶺。在20nm以前的技術節點,加工成本都有一定的下降。但從20nm開始,加工成本下降的趨勢被打破,開始顯著上升。成本的增加擠壓廠商的利潤,在一定程度上限制研發的投入,研發速度將有所放緩。

物理效應、功耗和經濟效益是現階段制約摩爾定律演進的關鍵因素,當前需要重新探索集成電路的發展規律和路徑。

三、另辟蹊徑再續摩爾定律

新理論和新技術推動產業步入后摩爾時代。目前業界認為集成電路產業發展已經進入到后摩爾時代。身處后摩爾時代,廠商必須突破原有的研發路徑,利用新理論和新技術來培育新的增長動力,性能與功耗的比值將成為評判技術和產品的重要指標。業界已提出后摩爾時代產業發展的四種路徑,即延續摩爾(More Moore)、擴展摩爾(More than Moore)、超越摩爾(Beyond Moore)和豐富摩爾(Much Moore)

(一)延續摩爾(More Moore)

結構優化和工藝微縮,共同助力延續摩爾。延續摩爾基本思路是從經典CMOS轉向非經典CMOS,半節距按比例減小,采用非經典器件結構等,從結構的設計及布局來實現產品的微縮,其本質是通過采用新的器件的結構和布局來實現芯片的設計和加工。系統芯片(SoC)是高度集成的芯片產品,是延續摩爾的一個重要應用。這類芯片是從設計的角度出發,是將系統各組件高度集成到一塊芯片上。組件的尺寸決定著相同面積上的芯片可以集成器件數量,工藝微縮表現為隨著工藝能力的提高,器件尺寸越小。因而,工藝微縮對于系統芯片影響較為顯著。設計端在使用更合理的結構的同時,更小尺寸的器件將會加大其可操作的空間。系統芯片與其他類型芯片相比,其集成度更高,速度更快。這優勢源于其從設計出發,實現從需求到產品的過程,因而更具有針對性。系統芯片是延續摩爾這一發展方向上較為突出的亮點,也是摩爾定律得以延續的一大佐證。

外企引領高水平,國產產品有望追趕。目前市場上利用延續摩爾思路發展的產品有CPU、內存、邏輯器件等,這些產品占整個市場份額的50%。從各大廠商所公布的數據來看,臺積電和三星兩家公司已具備7nm芯片量產的能力,這兩家公司在2018年晶圓代工全球市場份額分別為54.39%和14.40%。而國內龍頭中芯國際在今年早前宣布實現14nm工藝量產。目前國內工藝技術還有待提高,同時國外龍頭面臨產業瓶頸導致研發周期加長,也給國內廠商提供了追趕國際先進水平的窗口期。

(二)擴展摩爾(More than Moore)

技術優勢和市場決定擴展摩爾價值。與延續摩爾所采用的方式不同,擴展摩爾的本質是將不同功能的芯片和元件組裝拼接在一起封裝。其創新點在于封裝技術,在滿足需求的情況下,可快速和有效的實現芯片功能,具有設計難度低、制造便捷和成本低等優勢。這一發展方向使得芯片發展從一味追求功耗下降及性能轉向更加務實的滿足市場需求。這方面的產品包括了模擬/RF器件、無源器件、電源管理器件等,占集成電路市場約50%份額。

系統級封裝(SiP)優勢凸顯。系統級封裝在擴展摩爾的思路上技術較為成熟且具備量產條件。系統級封裝可以將一個系統或子系統集成在一個封裝內,應用此技術可突破PCB自身不足帶來系統性能的瓶頸,能最大限度實現各子芯片之間互聯互通,充分發揮各芯片和器件的作用。引線鍵合封裝工藝和倒裝焊工藝是實現封裝兩種可互相替代的關鍵性工藝,現被各大廠商廣泛應用,其對于系統級封裝起到至關重要的作用。

3D封裝成系統級封裝亮點。3D封裝技術是把不同功能的芯片或結構,通過堆疊技術或過孔互連等微機械加工技術,使其在Z軸方向上形成立體集成和信號連通的技術。從系統級封裝的傳統意義上來講,因為在Z軸上有了功能和信號的延伸,所以凡是有芯片堆疊的都可以稱之為3D。3D封裝運用到的技術有封裝堆疊(PoP)、芯片堆疊(SDP)、硅通孔技術(TSV)及硅基板技術。其中硅通孔技術是3D封裝技術的關鍵,也是當前技術先進性最高的封裝互連技術之一。3D封裝具有四大優勢:可縮短尺寸、減輕重量達40-50倍;在能耗不增加的情況下,運轉的速度更快;寄生性電容和電感得以降低;更有效的利用硅片的有效區域,與2D相比3D效率超過100%。3D封裝雖然優點突出,但其有一個弱點是各大廠商都需要攻克的難題,即功率密度隨電路密度提升而提升,解決散熱問題是3D封裝技術的關鍵。

技術決定市場份額,臺積電、英特爾將獨占鰲頭。SoIC是臺積電推出的一種創新的多芯片堆疊技術,是一種晶圓對晶圓的鍵合技術,本質是一種3DIC制程技術。SoIC是基于臺積電的CoWoS(Chip 》)與多晶圓堆疊(WoW)封裝技術開發的新一代創新封裝技術。SoIC解決方案將不同尺寸、制程技術及材料的裸晶堆疊在一起。相較于傳統使用微凸塊的三維積體電路解決方案,臺積電的SoIC的凸塊密度與速度高出數倍,同時大幅減少功耗。英特爾則推出Foveros有源內插器技術,其3D封裝將內插器作為設計的一部分,這種設計是超越自身EMIB設計的一步,適用于小型實現或具有極高內存帶寬要求的實現。內插器包含將電源和數據傳送到頂部芯片所需的通硅孔和走線,但它也承載平臺的PCH或IO。實際上,它是一個完全工作的PCH,但是有通孔,允許芯片連接在頂部。通過為每種情況下的工作選擇最佳晶體管,在正確的封裝下組合在一起,從而獲得最佳的優化效果。

(三)超越摩爾(Beyond Moore)

自組裝器件是超越摩爾領域取得突破的關鍵。在集成電路目前的架構中,信息的傳遞和處理都是以電子作為基本單元。從信息傳遞的角度來看,單個電子是不能傳遞信息的,多電子組合才能攜帶信息。與此同時,信號在傳遞過程中還會存在能量消耗并產生熱量。若尋找到其他基本單元自身可以攜帶信息或者信息傳遞過程中不會消耗能量,將會降低功耗并提升性能,打破現在所面臨的發展瓶頸問題,這類研究則屬于超越摩爾。目前越越摩爾方向主要處在研究階段,量子器件、自旋器件、磁通量器件、碳納米管或納米線器件等能夠實現自組裝的器件是超越摩爾方向研究的熱點。

(四)豐富摩爾(Much Moore)

在微納電子學、物理學、數學、化學、生物學、計算機技術等領域高度交叉和融合的背景下,集成電路理論和技術加速創新突破。在這些理論和技術的指導下,對集成電路的理解可能進入到另外一個維度,在制作工藝和產品上實現質的飛躍。這一方面的發展需要相關學科理論的突破才能傳導到集成電路行業,因而現階段在豐富摩爾發展方向上還未能取得有效的進展。

四、總結

摩爾定律是基于集成電路產業發展現實所得出來的合理推測。隨著器件尺寸不斷減小,技術瓶頸開展顯著制約工藝發展,當前產品迭代速度已下降,因此,需要重新探討集成電路產業和技術的發展方向。目前,業界已開始沿著延續摩爾(More Moore)、擴展摩爾(More than Moore)、超越摩爾(Beyond Moore)和豐富摩爾(Much Moore)四個思路開始探索。

從技術的角度看,超越摩爾和豐富摩爾這兩大方向突破尚需時日,從研究突破到實現量產,還有很長的路要走,并且,這兩大方向目前尚未出現確定趨勢。然而,以小尺寸SoC為代表的延續摩爾和以SIP技術為代表的擴展摩爾,在技術研發和量產工藝方面則更接近商用量產,將會是未來一段時間集成電路產業的發展趨勢。

責任編輯:zl

-

集成電路

+關注

關注

5381文章

11382瀏覽量

360851 -

摩爾定律

+關注

關注

4文章

632瀏覽量

78931

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

“自我實現的預言”摩爾定律,如何繼續引領創新

介紹MCUboot支持的四種升級模式(2)

四種電源防接反電路

封裝技術會成為摩爾定律的未來嗎?

如何理解IGBT的四種SOA?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

探索后摩爾定律的四種路徑

探索后摩爾定律的四種路徑

評論