長江存儲打破全球3D NAND技術壟斷,作為國家重點打造的存儲器大項目,經歷多年的研發,終于走向市場正式向存儲巨頭們挑戰。

集微網消息,在存儲芯片領域常年被國際幾大巨頭壟斷的背景下,我國從過去完全缺席存儲芯片市場的困境,經歷多年努力研發,陸續在3D NAND 和 DRAM 上打破國際壟斷,而長江存儲作為國內的領頭企業,率先實現3D NAND的突破創新。

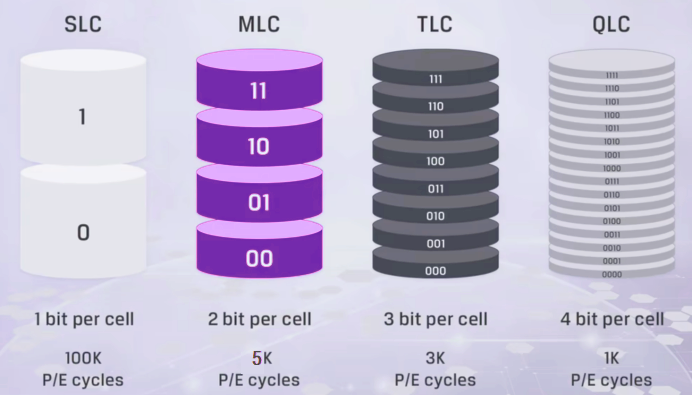

隨著半導體產業的發展,產業界對存儲器密度的要求越來越高,與此同時,三維存儲器中疊層結構的數量也在不斷提高,該結構中溝道通孔(CH)的深寬比也越來越高。然而這種存儲器結構卻也帶來一些弊端與問題,由于溝道通孔寬度較小部分的存儲單元相較于溝道通孔寬度較大部分的存儲單元編程/擦除速度較快,因此導致了溝道通孔寬度較小的存儲單元讀干擾嚴重、擦除耦合效應差,各個存儲單元的特性不一致、閾值電壓分布寬等問題,從而影響了三維存儲器的性能。

為解決以上現有技術的缺點,長江存儲于2019年6月28日提出了一項名為“用于三維存儲器的疊層結構、三維存儲器及其制備方法”的發明專利(申請號:201910571659.5),申請人長江存儲科技有限責任公司。

長江存儲的這項專利提供了一種用于三維存儲器的疊層結構、三維存儲器及其制備方法,包括上下交替疊置的犧牲層及柵間介質層,其中疊層結構內包含貫穿疊層結構的溝道通孔,且溝道通孔各部分的寬度隨著疊層結構的厚度變化而變化,提高了存儲單元的性能與穩定性。

圖1 三維存儲器的疊層結構

圖1是三維存儲器的一種疊形結構示意圖,從圖中可以看出,此疊形結構包括上下交替疊置的犧牲層111以及柵間介質層112,溝道通孔14。其中溝道通孔沿著疊層結構的厚度方向貫穿整個疊形結構,而各處的通孔寬度也不盡相同。犧牲層111的厚度與溝道通孔的寬度成正比,而柵間介質層112的厚度與溝道通孔的寬度成反比。因此在圖1所示疊層結構中,當沿著疊層結構11的厚度方向由上而下時,溝道通孔的寬度和犧牲層的厚度逐層遞減,柵間介質層的厚度逐層遞增 。

基于此專利提出這種三維存儲器疊層結構,所有存儲單元編程/擦除速度一致,擦除態耦合效應較好,所有存儲單元的性能具有較好的均一性,三維存儲器的閾值電壓較窄,具有較好的性能與穩定性。同時,該結構可以降低對形成溝道通孔時的刻蝕工藝要求,提高了工藝的有效性與穩定性。

圖2 三維存儲器的制備方法

圖2是此專利提出的一種關于三維存儲器的制備方法,首先要提供半導體襯底,如硅襯底、鍺襯底、單晶硅晶圓等,之后在此半導體襯底上采用刻蝕工藝形成圖1所示三維存儲器疊層結構,進而于溝道通孔底部形成外延層,并在溝道通孔的側壁形成功能側壁,同時在功能側壁表面及外延層的上表面形成溝道層。之后在疊層結構內形成柵極間隙,去除犧牲層,形成犧牲間隙,并在犧牲間隙內形成柵極層。

圖3 溝道通孔側壁生成示意圖

圖3展示了圖2中步驟4的細節,在溝道通孔14的側壁形成功能側壁16,并功能側壁16的表面及外延層15的上表面形成溝道層17。首先采用原子層沉積工藝在溝道通孔14的側壁表面形成所述阻擋層161,并利用同樣的方法生成電荷捕獲層162以及隧穿層163。

集成電路產業是當今信息技術產業的核心組成部分,雖位于整個產業的底層卻不容忽視,在被諸多國外廠商壟斷的背景下,我國長江存儲等芯片企業率先打破了國外對存儲產業的壟斷,這也標志著我國在存儲領域的一大進步與發展。

-

存儲芯片

+關注

關注

11文章

886瀏覽量

43088 -

長江存儲

+關注

關注

5文章

323瀏覽量

37831

發布評論請先 登錄

相關推薦

中興通訊攜手中國移動推出AI裸眼3D創新產品

長江存儲正加速轉向國產半導體設備

長江存儲使用國產設備制造出3D NAND閃存芯片

Samsung 和Cadence在3D-IC熱管理方面展開突破性合作

NAND Flash(貼片式TF卡)存儲新突破,基礎示例

三維掃描與3D打印在法醫頭骨重建中的突破性應用

長江存儲QLC閃存壽命實現重大突破

長江存儲向存儲巨頭們發起挑戰,3D NAND實現突破性的創新

長江存儲向存儲巨頭們發起挑戰,3D NAND實現突破性的創新

評論