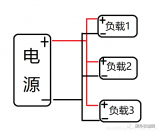

從電路來說,總是存在驅動的源和被驅動的負載。如果負載電容比較大,驅動電路要把電容充電、放電,才能完成信號的跳變,在上升沿比較陡峭的時候,電流比較大,這樣驅動的電流就會吸收很大的電源電流,由于電路中的電感,電阻(特別是芯片管腳上的電感,會產生反彈),這種電流相對于正常情況來說實際上就是一種噪聲,會影響前級的正常工作。這就是耦合。

去藕電容就是起到一個電池的作用,滿足驅動電路電流的變化,避免相互間的耦合干擾。

旁路電容實際也是去藕合的,只是旁路電容一般是指高頻旁路,也就是給高頻的開關噪聲提高一條低阻抗泄防途徑。高頻旁路電容一般比較小,根據諧振頻率一般是0.1u,0.01u等,而去耦合電容一般比較大,是10u或者更大,依據電路中分布參數,以及驅動電流的變化大小來確定。

去耦和旁路都可以看作濾波。去耦電容相當于電池,避免由于電流的突變而使電壓下降,相當于濾紋波。具體容值可以根據電流的大小、期望的紋波大小、作用時間的大小來計算。去耦電容一般都很大,對更高頻率的噪聲,基本無效。旁路電容就是針對高頻來的,也就是利用了電容的頻率阻抗特性。電容一般都可以看成一個RLC串聯模型。在某個頻率,會發生諧振,此時電容的阻抗就等于其ESR。如果看電容的頻率阻抗曲線圖,就會發現一般都是一個V形的曲線。具體曲線與電容的介質有關,所以選擇旁路電容還要考慮電容的介質,一個比較保險的方法就是多并幾個電容。

去耦電容在集成電路電源和地之間的有兩個作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。數字電路中典型的去耦電容值是0.1μF。這個電容的分布電感的典型值是5μH。0.1μF的去耦電容有5μH的分布電感,它的并行共振頻率大約在7MHz左右,也就是說,對于10MHz以下的噪聲有較好的去耦效果,對40MHz以上的噪聲幾乎不起作用。1μF、10μF的電容,并行共振頻率在20MHz以上,去除高頻噪聲的效果要好一些。每10片左右集成電路要加一片充放電電容,或1個蓄能電容,可選10μF左右。最好不用電解電容,電解電容是兩層薄膜卷起來的,這種卷起來的結構在高頻時表現為電感。要使用鉭電容或聚碳酸酯電容。去耦電容的選用并不嚴格,可按C=1/F,即10MHz取0.1μF,100MHz取0.01μF。

退耦原理:(去耦即退耦)

高手和前輩們總是告訴我們這樣的經驗法則:“在電路板的電源接入端放置一個1~10μF的電容,濾除低頻噪聲;在電路板上每個器件的電源與地線之間放置一個0.01~0.1μF的電容,濾除高頻噪聲。”在書店里能夠得到的大多數的高速PCB設計、高速數字電路設計的經典教程中也不厭其煩的引用該首選法則(老外俗稱Rule of Thumb)。但是為什么要這樣使用呢?

首先就我的理解介紹兩個常用的簡單概念

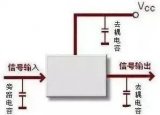

什么是旁路?旁路(Bypass),是指給信號中的某些有害部分提供一條低阻抗的通路。電源中高頻干擾是典型的無用成分,需要將其在進入目標芯片之前提前干掉,一般我們采用電容到達該目的。用于該目的的電容就是所謂的旁路電容(Bypass Capacitor),它利用了電容的頻率阻抗特性(理想電容的頻率特性隨頻率的升高,阻抗降低,這個地球人都知道),可以看出旁路電容主要針對高頻干擾(高是相對的,一般認為20MHz以上為高頻干擾,20MHz以下為低頻紋波)。

什么是退耦?退耦(Decouple)

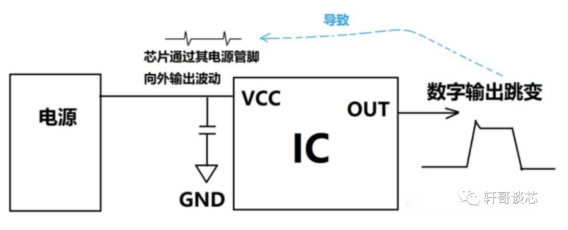

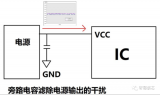

最早用于多級電路中,為保證前后級間傳遞信號而不互相影響各級靜態工作點的而采取的措施。在電源中退耦表示,當芯片內部進行開關動作或輸出發生變化時,需 要瞬時從電源在線抽取較大電流,該瞬時的大電流可能導致電源在線電壓的降低,從而引起對自身和其他器件的干擾。為了減少這種干擾,需要在芯片附近設置一個 儲電的“小水池”以提供這種瞬時的大電流能力。

在電源電路中,旁路和退耦都是為了減少電源噪聲。旁路主要是為了減少電源上的噪聲對器件本身的干擾(自我保護);退耦是為了減少器件產生的噪聲對電源的干擾(家丑不外揚)。有人說退耦是針對低頻、旁路是針對高頻,我認為這樣說是不準確的,高速芯片內部開關操作可能高達上GHz,由此引起對電源線的干擾明顯已經不屬于低頻的范圍,為此目的的退耦電容同樣需要有很好的高頻特性。本文以下討論中并不刻意區分退耦和旁路,認為都是為了濾除噪聲,而不管該噪聲的來源。

簡單說明了旁路和退耦之后,我們來看看芯片工作時是怎樣在電源線上產生干擾的。我們建立一個簡單的IO Buffer模型,輸出采用圖騰柱IO驅動電路,由兩個互補MOS管組成的輸出級驅動一個帶有串聯源端匹配電阻的傳輸線(傳輸線阻抗為Z0)。

設電源引腳和地引腳的封裝電感和引線電感之和分別為:Lv和Lg。

兩個互補的MOS管(接地的NMOS和接電源的PMOS)簡單作為開關使用。假設初始時刻傳輸在線各點的電壓和電流均為零,在某一時刻器件將驅動傳輸線為高電平,這時候器件就需要從電源管腳吸收電流。在時間T1,使PMOS管導通,電流從PCB板上的VCC流入,流經封裝電感Lv,跨越PMOS管,串聯終端電阻,然后流入傳輸線,輸出電流幅度為VCC/(2×Z0)。電流在傳輸線網絡上持續一個完整的返回(Round-Trip)時間,在時間T2結束。之后整個傳輸線處于電荷充滿狀態,不需要額外流入電流來維持。當電流瞬間涌過封裝電感Lv時,將在芯片內部的電源提供點產生電壓被拉低的擾動。該擾動在電源中被稱之為同步開關噪聲(SSN,Simultaneous Switching Noise;SSO,Simultaneous Switching Output Noise)或Delta I噪聲。

在時間T3,關閉PMOS管,這一動作不會導致脈沖噪聲的產生,因為在此之前PMOS管一直處于打開狀態且沒有電流流過的。同時打開NMOS管,這時傳輸線、地平面、封裝電感Lg以及NMOS管形成一回路,有瞬間電流流過開關B,這樣在芯片內部的地結點處產生參考電平點被抬高的擾動。該擾動在電源系統中被稱之為地彈噪聲(Ground Bounce,我個人讀著地tan)。

實際電源系統中存在芯片引腳、PCB走線、電源層、底層等任何互聯機都存在一定電感值,因此上面就IC級分析的SSN和地彈噪聲在進行Board Level分析時,以同樣的方式存在,而不僅僅局限于芯片內部。就整個電源分布系統來說(Power Distribute System)來說,這就是所謂的電源電壓塌陷噪聲。因為芯片輸出的開關操作以及芯片內部的操作,需要瞬時的從電源抽取較大的電流,而電源特性來說不能快速響應該電流變化,高速開關電源開關頻率也僅有MHz量級。為了保證芯片附近電源在線的電壓不至于因為SSN和地彈噪聲降低超過器件手冊規定的容限,這就需要在芯片附近為高速電流需求提供一個儲能電容,這就是我們所要的退耦電容。

所以電容重要分布參數的有三個:等效串聯電阻ESR 等效串聯電感ESL 、等效并聯電阻EPR Rp 。其中最重要的是ESR、 ESL,實際在分析電容模型的時候一般只用RLC簡化模型,即分析電容的C、ESR、ESL。因為寄生參數的影響,尤其是ESL的影響,實際電容的頻率特性表現出阻抗和頻率成“V”字形的曲線,低頻時隨頻率的升高,電容阻抗降低;當到最低點時,電容阻抗等于ESR;之后隨頻率的升高,阻抗增加,表現出電感特性(歸功于ESL)。因此對電容的選擇需要考慮的不僅僅是容值,還需要綜合考慮其他因素。

所有考慮的出發點都是為了降低電源地之間的感抗(滿足電源最大容抗的條件下),在有瞬時大電流流過電源系統時,不至于產生大的噪聲干擾芯片的電源地引腳。

電容的頻率特性

當頻率很高時,電容不再被當做集總參數看待,寄生參數的影響不可忽略。寄生參數包括Rs,等效串聯電阻(ESR)和Ls等效串聯電感(ESL)。電容器實際等效電路如圖1所示,其中C為靜電容,1Rp為泄漏電阻,也稱為絕緣電阻,值越大(通常在GΩ級以上),漏電越小,性能也就越可靠。因為Pp通常很大(GΩ級以上),所以在實際應用中可以忽略,Cda和Rda分別為介質吸收電容和介質吸收電阻。介質吸收是一種有滯后性質的內部電荷分布,它使快速放電后處于開路狀態的電容器恢復一部分電荷。

ESR和ESL對電容的高頻特性影響最大,所以常用如圖1(b)所示的串聯RLC簡化模型,可以計算出諧振頻率和等效阻抗:

電容器串聯RLC模型的頻域阻抗圖如圖2所示,電容器在諧振頻率以下表現為容性;在諧振頻率以上時表現為感性,此時的電容器的去耦作用逐漸減弱。同時還發現,電容器的等效阻抗隨著頻率的增大先減小后增大,等效阻抗最小值為發生在串聯諧振頻率處的ESR。

圖2 電容器串聯RLC模型的頻域阻抗圖

由諧振頻率式(4-8)可得出,容值大小和ESL值的變化都會影響電容器的諧振頻率,如圖3所示。由于電容在諧振點的阻抗最低,所以設計時盡量選用fR和實際工作頻率相近的電容。在工作頻率變化范圍很大的環境中,可以同時考慮一些fR較小的大電容與fR較大的小電容混合使用。

發布評論請先 登錄

相關推薦

去耦電容的擺放位置和作用

什么是去耦電容 有什么作用

關于濾波電容、去耦電容、旁路電容作用及其原理

關于濾波電容、去耦電容、旁路電容作用及其原理

評論