福建晉華目前只專注于DRAM 的制造,雖然相對于國外半導體存儲三巨頭而言,技術在某些方面會有不足,但是從16年成立至今,短短三年內,就已經達到DRAM技術的較高水平,其實力仍不容小覷。

集微網消息,現如今全球范圍內的半導體存儲行業已經形成了三星、SK海力士和鎂光三足鼎立之勢,而放眼國內,福建晉華、兆易創新、紫光集團等企業也逐漸開始抗起我國半導體存儲行業的大旗。

隨著各種電子產品朝小型化發展的趨勢,動態隨機存取存儲器(dynamic randomaccess memory ,DRAM)單元的設計也必須符合高集成度及高密度的要求。對于具備凹入式柵極結構的DRAM單元而言,由于它可以在相同的半導體基底內獲得更長的載流子通道長度,進而減少電容結構的漏電情形產生,因此在目前主流發展趨勢下,具備凹入式柵極結構的DRAM單元已逐漸取代僅具備平面柵極結構的DRAM單元。

然而,受限于制作工藝技術之故,現有具備凹入式柵極結構的DRAM單元仍存在有許多缺陷,還待進一步改良并有效提升相關存儲器元件的效能及可靠度。

為了解決這一問題,早在2016年福建晉華就申請了一項名為“動態隨機存取存儲器元件的形成方法”的發明專利(申請號:201611198384 .8),申請人為福建省晉華集成電路有限公司。

該專利提供了一種隨機動態處理存儲器元件的形成方法,主要是利用單一制作工藝在其位線內形成密度高且厚度較小的阻障層,所以,該方法可以在制作工藝簡化的前提下降低阻障層的阻值。

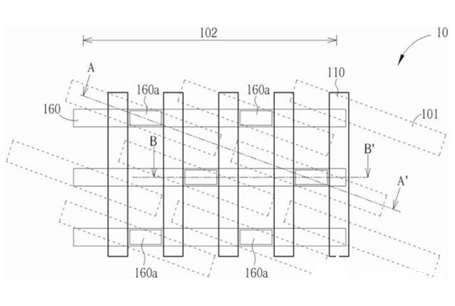

圖1

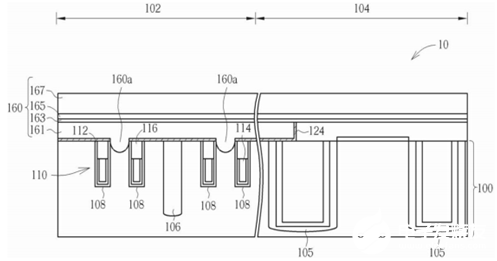

圖2

上圖1是該專利中提出的動態隨機存取存儲器元件10,圖2是圖1中沿著切線B-B’的剖面示意圖。由上面兩圖我們可以看到,該專利提出的動態隨機存取存儲器元件10主要包括:基底100、存儲區(記憶體區) 102、周邊區104、字線(字符線)110以及位線160。

一般來說,基底100由硅基底、含硅基底(如SiC、SiGe)或硅覆絕緣(silicon-on-insulator ,SOI)基底等構成。除了存儲區102和周邊區104均置在了基底100上面之外,基底100上還形成有多個主動區(active area ,AA)101,相互平行地沿著第一方向延伸。另外其內部還形成有多個埋藏式柵極114,埋藏式柵極114是相互平行地沿著第二方向延伸,并橫跨第一方向。

此外,基底100上還有多個位線160,其主要在埋藏式柵極114上產生,且它們相互平行地沿著第三方向延伸,并同時橫跨主動區101與字線110,如圖1所示。位線160與字線110之間通過位線接觸插塞(bit line contact ,BLC)160a來電連接至各該晶體管元件的源極/漏極區,并且位線接觸插塞160a位于兩字線110之間。

在該專利提出的方法是利用射頻物理氣相沉積制作工藝來形成位線160的阻障層163,使其具有雙層結構,這樣就降低了阻礙層的厚度,使位線160具有較低的阻值與較小的整體厚度。另一方面,阻障層163雖然具有雙層結構,但其整體厚度僅介于40埃至50埃之間,因而可以很好地改善位線160的高度并且簡化了制作工藝。

福建晉華目前只專注于DRAM 的制造,雖然相對于國外半導體存儲三巨頭而言,技術在某些方面會有不足,但是從16年成立至今,短短三年內,就已經達到DRAM技術的較高水平,其實力仍不容小覷。

-

DRAM

+關注

關注

40文章

2303瀏覽量

183319 -

福建晉華

+關注

關注

1文章

17瀏覽量

16714

發布評論請先 登錄

相關推薦

中興、晉華接連中招 下一個遭禁售的會是誰?

禍不單行!聯電單方面宣布暫停與晉華合作

美國對福建晉華有限公司實施禁售令,福建晉華將成為第二個中興

福建晉華成了第二個中興,福建晉華與美光恩怨未了

聯電為何突然宣布暫停協助福建晉華

美國為何要對晉華下手呢?

如何辨別SRAM是否屬于動態隨機存儲器

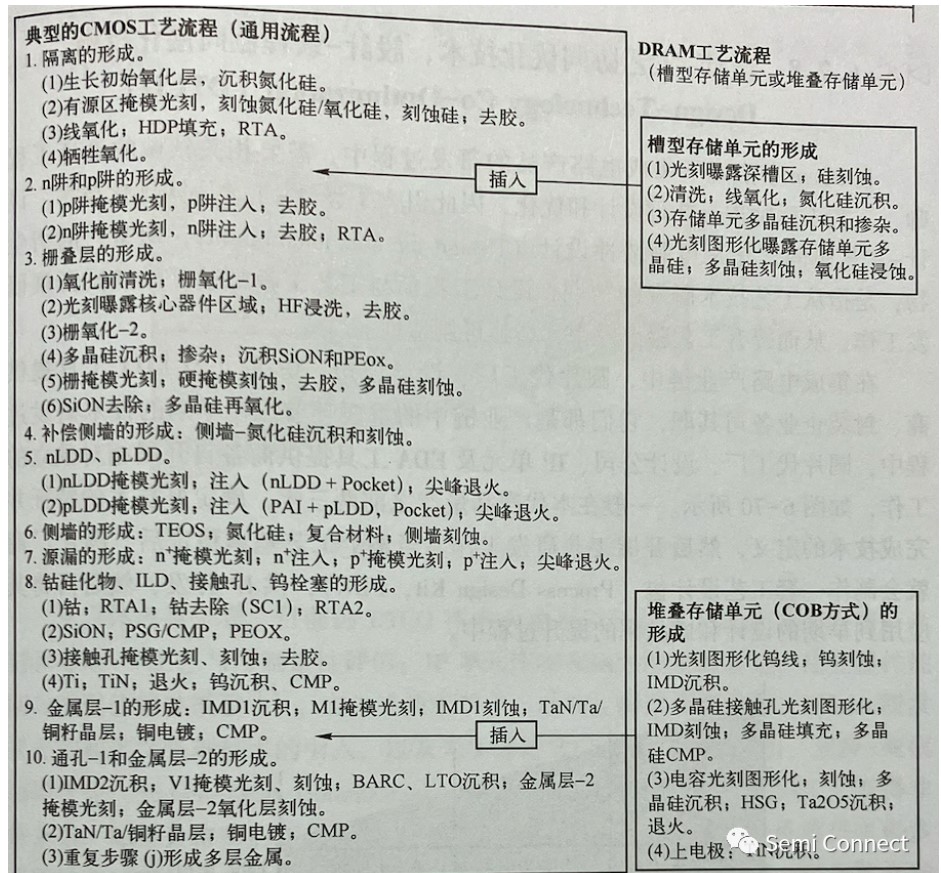

動態隨機存儲器集成工藝(DRAM)詳解

淺析動態隨機存儲器DRAM集成工藝

福建晉華隨機動態處理存儲器元件的形成方法專利

福建晉華隨機動態處理存儲器元件的形成方法專利

評論