引言

隨著半導體工藝技術步入納米階段,在單一芯片中集成上億晶體管已經成為現實,據ITRS(International Technology Roadmap for Semiconductors,國際半導體技術路線圖)預測(見表1),到2010年,單個芯片上的晶體管數目將達到22億個。如何有效地利用數目眾多的晶體管是芯片體系結構必須回答的新問題。倘若因循單核的發展思路,芯片設計將面臨互連延遲、存儲帶寬、功耗極限等性能提升的瓶頸問題。因此,業內普遍認識到,有必要研究新型的芯片體系架構以適應性能增長和功耗下降同時發生這樣看似矛盾的需求。多核技術是一條可行之路。多核能夠用多個低頻率核單元產生超過高頻率單核的處理效能,獲得較佳的性價比。圍繞著多核的一系列技術問題業已成為近期芯片業研究的重點和未來的主要發展方向。

表1 ITRS預測表

按照不同的片上互連方式,多核SoC可分為兩大類:傳統的基于總線的互連和基于網絡的互連。前者是現有SoC的擴展,通過多總線及層次化總線等技術使得片上集成更多的處理器核,從而實現高復雜度和高性能;而后者是近些年提出的嶄新的概念,即多處理器核之間采用分組路由的方式進行片內通信,從而克服了由總線互連所帶來的各種瓶頸問題,這種片內通信方式稱為片上網絡(Network on a Chip,NoC)。

NoC概述

基本概念

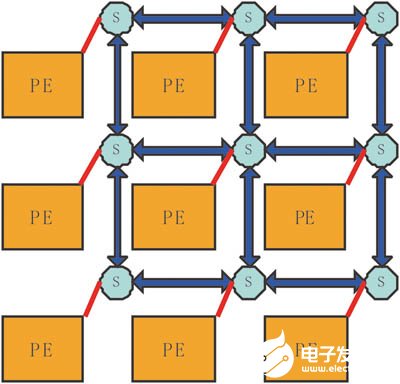

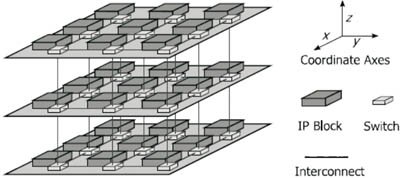

NoC是指在單芯片上集成大量的計算資源以及連接這些資源的片上通信網絡,如圖1所示。NoC包括計算和通信兩個子系統,計算子系統(圖中由PE,Processing Element構成的子系統)完成廣義的“計算”任務,PE既可以是現有意義上的CPU、SoC,也可以是各種專用功能的IP核或存儲器陣列、可重構硬件等;通信子系統(圖中由Switch組成的子系統)負責連接PE,實現計算資源之間的高速通信。通信節點及其間的互連線所構成的網絡被稱為片上通信網絡(On-Chip Network, OCN)[1-3],它借鑒了分布式計算系統的通信方式,用路由和分組交換技術替代傳統的片上總線來完成通信任務。

圖1 典型的NoC結構示意圖

NoC技術優勢分析

基于分組路由方式進行片上通信的NoC在片上通信方式、功耗、基于重用的設計方法學、解決單一時鐘全局同步等方面都具有優越性。

·有利于提高通訊帶寬

總線結構是現有芯片架構的通信脈絡,隨著電路規模越來越大,總線結構將成為芯片設計的瓶頸:雖然總線可以有效地連接多個通信方,但總線地址資源并不能隨著計算單元的增加而無限擴展;雖然總線可由多用戶共享,但一條總線無法支持一對以上的用戶同時通信,即串行訪問機制導致了通信的瓶頸。此外,片上通信是功耗的主要來源,龐大的時鐘網絡與總線的功耗將占據芯片總功耗的絕大部分。

NoC的網絡拓撲結構提供了良好的可擴展性;NoC連線網絡提供了良好的并行通信能力,從而使得通信帶寬增加幾個數量級;此外,NoC將長的互連線變成交換開關之間互相連接的短連線,這對功耗控制變得極為有利;另一方面,NoC借鑒了通訊協議中的分層思想,這就為從物理級到應用級的全面功耗控制提供了可能。

·有利于提升重用設計

總線架構可擴展性和可重用性差,為此在芯片計算能力演變時,必須跟隨著處理能力的需求而變更設計(如更高的內存寬度、更高的頻率、更靈活的同步或異步設計等等),每一代芯片的推出都伴隨著程度不等的設計變更,這對于開發人員而言是相當大的負擔。若是將通信架構獨立設計,并且運用更具彈性的技術,對于縮短設計周期、減少開發成本都有不小的幫助。

由于NoC所使用的通信協議層本身屬于獨立的資源,因此提供了支持高效率可重用設計方法學的體系結構:現有規模的SoC可以基于片上通信協議作為計算節點“即插即用”于NoC的網絡節點;給定的互連拓撲結構使得芯片集成可以采用基于片上通信的設計方法(Communication-based Design,CBD)來完成。通信和計算完全分離的技術(也就是通信與計算的正交設計)將重用范圍從計算單元可重用擴展到計算與通信單元皆可重用的層次,從而大大提升了重用設計的水平。

·有利于解決全局同步的難題

納米工藝所帶來的各種物理效應使得片上全局同步越來越困難。當采用50nm工藝,時鐘頻率為10GHz時,全局線延遲將達6~10個時鐘周期,時鐘偏斜(Skew)變得難以控制,而時鐘樹又是影響芯片功耗和成本的一個主要因素。這些問題,隨著集成器件尺寸越來越小,時鐘頻率越來越高,將變得越來越突出。

NoC的片內網絡通信方式,資源之間的短線互連和天然的全局異步局部同步(GALS)時鐘策略等特性是解決這些問題有效途徑。

總而言之,研究NoC設計方法和設計技術是滿足納米工藝條件下高集成度芯片發展的必然需求。

NoC設計空間

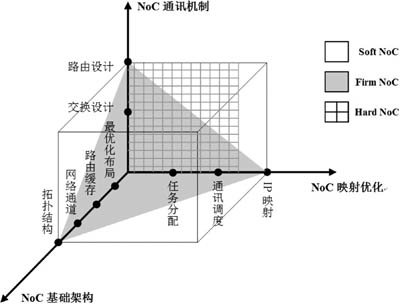

完整的NoC設計方法學包括很多方面的問題,它們對NoC的發展都是至關重要的,且已經引起了學術界的廣泛研究。Carnegie Mellon大學的U.Y. Ogras等人在文獻[4]中提出了NoC設計空間的概念并將NoC研究歸納為三大類關鍵問題:基礎架構、通訊機制和映射優化,如圖2所示。

圖2 NoC設計空間示意圖

圖中,“Hard NoC”(網格部分)指基本架構確定,各PE節點的內容也固定的一類NoC結構,其設計空間只是圖中一矩形部分,設計余度最小;“Firm NoC”(灰色陰影空間)指其基本架構已確定,網絡通道寬度與通訊節點緩存大小不確定,其他維度對設計者完全自由的一類NoC結構,設計者可以根據確定的應用實現最優的布圖規劃、通訊調度與任務分配算法、IP映射算法和路由交換解決方案,設計空間比較靈活;“Soft NoC”(白色立方體部分)指設計者需要根據應用來優化NoC設計空間的所有問題,設計靈活性最高,但設計難度和工作量也相應最大。

設計者根據給定的具體應用,依據應用特征圖(Application Characterization Graph,APCG),在時間、成本、技術儲備等約束條件下,首先按應用選擇基于哪類NoC開展設計;其次在該類NoC的設計空間范圍內解決相應關鍵問題,以探索最優的NoC實現方案。

NoC關鍵技術難點

NoC關鍵技術主要包括系統建模、拓撲結構、路由方法、交換方法、緩存策略、服務質量和映射優化等,近年來都不同程度地取得研究進展,而阻礙NoC走向大規模應用的瓶頸在于以下幾方面:

存儲結構問題

Memory是NoC中十分重要的組件,在現有的片上多處理器系統中,存儲器占到70%的芯片面積,并且在不久的將來會上升到90%[5];而從能耗的角度來看,存儲器所引入的功耗也可達系統功耗的90%[6],這對芯片的散熱、封裝和可靠性等都帶來了嚴重的問題;NoC系統需要大量的存儲元件,并被組織成復雜的存儲子系統(memory subsystem),這個存儲子系統將支持NoC的并行數據存儲、傳輸及交換。NoC中大量的存儲資源必將占用多個路由節點,且由于處理單元與存儲資源之間的數據交換非常頻繁,若在數據包傳輸路徑上路由節點數目過多,會帶來很大的通信延時。如何有效縮短源節點到目的節點間的距離對提高整個NoC系統性能十分關鍵。

再者,從通信帶寬的角度,隨著工藝的進步,計算訪存比進一步增大,意味著基于該結構獲得接近峰值性能的應用算法越少。這就引入了一系列問題,如何讓眾多處理器核有足夠的數據可算?如何更充分地利用片上有限存儲空間實現核間共享,以避免片外訪存?如何充分利用有限訪存帶寬,盡量讓訪存通道優先滿足處于關鍵路徑處理器核的訪問請求?最近美國Sandia國家實驗室提出在多核處理器芯片上堆疊存儲芯片,來解決帶寬增長不足的問題,這或許是一種可行的方案。

總而言之,片上存儲結構已經成為影響NoC性能的關鍵因素之一。

軟件并行化問題

未來的基于多核的高性能處理芯片可能會遇到很多傳統的串行程序自動并行化方法較難實施的應用。如果不能有效地利用NoC片上并行處理資源,則并行計算的實際性能將會很低,因此如何通過有效的方法和模型,充分地利用NoC的眾多處理單元,并極大地降低應用的開發難度,便成為迫切需要解決的問題。

與并行計算機發展過程中遇到的問題相類似,NoC并行處理體系結構所面臨的主要問題是如何將應用中蘊含的不同層次、不同粒度的并行性有效地提取出來并映射到多核的并行硬件結構上去。這一問題的解決涉及包括程序設計模型、程序設計語言、編譯系統及硬件支撐等在內的多個方面。

總體來說,開發并行程序可以有三種途徑,一是串行程序自動并行化。這條路目前尚未走通,更為實際的目標應為人機交互的自動并行化;二是設計全新的并行程序設計語言。這種方法的缺點是需要全部改寫原有程序,對用戶來說成本和風險也很高,且效率不能保證。但是,隨著多核的出現,若面向大眾推廣并行計算環境,就必須有一種新的容易被接受的程序設計語言。目前國際上正在研究的新興并行程序設計語言如IBM的X10、UPC(統一并行 C語言,C語言的擴展)和Titanmin(Java的擴展)等;第三條途徑就是串行語言加并行庫或偽注釋制導語句的擴展,也即增加一個庫或一些新的制導語句來幫助進行消息傳遞和并行。這正是MPI和OpenMP所采取的途徑,也是目前比較容易被接受且性能較高的途徑。但其程序開發效率很低,難度也比較大。

功耗管理問題

雖然NoC有助于提高芯片的能效(Energy-Efficiency),但不能忽視,由于多核系統片上集成規模的大幅度增加,功耗問題依然突出。如何在NoC設計中提高能效,對眾多計算資源進行調度管理以最大限度降低功耗依然是NoC設計所面臨的重要問題之一。

從體系結構角度看,NoC主要包括處理器核、核間互連以及片上存儲三個主要部分。NoC的低功耗研究可以圍繞功耗評估,處理器核功耗優化,片上網絡功耗優化以及片上存儲功耗優化這四個方面對各部分展開,其中功耗評估是NoC低功耗設計的基礎。

功耗是導致包括NoC在內的多核技術出現的重要誘因,也是片上多處理器設計的重要制約因素。對于NoC的不同設計模塊和設計層次,都存在行之有效的降低功耗的方法,而這些方法又可能是互相牽制,互相影響的。因此需要貫穿NoC體系結構到電路工藝的各方面的豐富知識,才能在設計早期做出正確的多核架構的選擇。一般而言,從越高的設計抽象層次入手考慮低功耗設計問題,則可獲得的降低功耗的效率就越大。

NoC發展趨勢

技術發展趨勢

·向層次化眾核方向發展

微軟公司2007年6月在美國西雅圖召開了第一個以ManyCore(眾核)為主題的研討會(Workshop),標志著眾核設計已經成為技術發展的趨勢和學術研究的熱點。

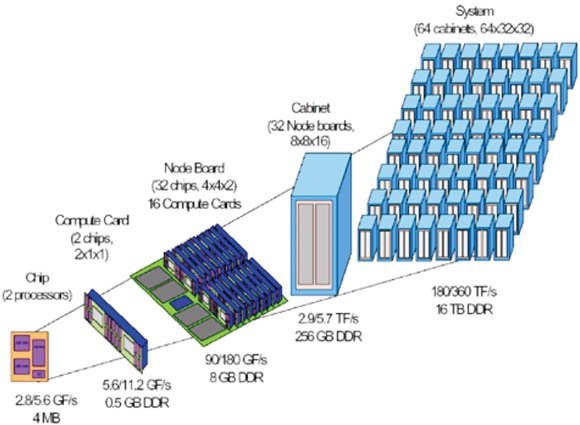

集成電路設計總是想方設法把現有的各種電子電路乃至計算系統集成到單一芯片上,因此計算機體系結構歷來是集成電路片上系統架構的參考體系。超級計算機是最強大的計算機,充分參考超級計算機的體系結構是設計多核處理器的基本思路。超級計算機體系架構的基本特征就是小核大陣列和層次化管理。無論是世界排名第一的Roadrunner(122400個核),還是排名第二的BlueGene/L(212992個核),如圖3所示,都是采用高性能、層次化、可擴展的巨大陣列,連接數目眾多的普通微處理器(小核)來保障最優的性能。超級計算機告訴我們,小核大陣列和層次化管理必將成為眾核處理器的主流技術發展方向。

圖3 BlueGene/L的層次化陣列結構

·向三維NoC方向發展

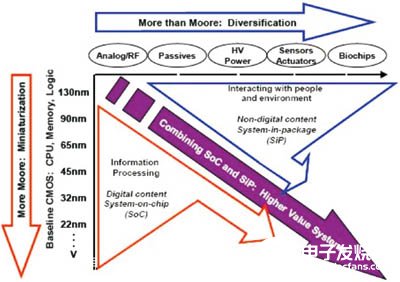

ITRS 2007年版闡述了More Moore(延伸摩爾定律)和More than Moore(超越摩爾定律)兩個概念,如圖4所示,其中延伸摩爾定律是按照等比例縮小繼續走微細化的道路,而超越摩爾定律追求的是功能多樣化,并指出下一代SoC(NoC)與SiP技術融合的發展趨勢。

圖4 ITRS 2007年版摩爾定律詮釋圖

正如ITRS所預測,在工藝技術發展和設計技術需求的雙重驅動下,三維集成(又稱為系統級封裝,SiP)技術愈來愈受到學術界和工業界的關注和重視。NoC雖然克服了全局延遲過長帶來的信號完整性及全局同步等一系列問題,但并沒有在根本上解決縮短物理連線,減小信號時延的問題。由于二維 NoC布局條件的限制,難以保證關鍵部件相鄰以縮短關鍵路徑長度,而三維集成技術可把不同的器件層堆疊起來,不僅在真正意義上縮短了連線的長度,并克服這種布局的限制。因此把NoC和三維集成這兩種設計技術融合起來的三維 NoC就顯得自然且引人。

三維NoC是在單個芯片上將資源節點(Resource)分布在不同的物理層上,并用三維立體架構實現資源間的互連,以構建高帶寬、低延時、低功耗的NoC系統。典型的三維Mesh結構NoC如圖5所示。三維 NoC是一個嶄新的研究話題,近兩年才在國際上被提出(最早一篇相關研究論文于2005年公開發表[9])。目前從事該領域研究的學術機構包括美國斯坦福大學、加州理工大學、賓州州立大學、華盛頓州立大學,瑞典皇家工學院、日本的Keio University,加拿大的不列顛哥倫比亞大學,以及Intel、Toshiba等大公司的研究中心。可見,三維NoC已經引起了國際上學術界和產業界的注意,很可能在未來幾年內發展成為一個重要的研究領域,并得到廣泛的關注。

圖5 三維NoC示意圖

產業發展趨勢

多核技術在產業界已有廣泛應用。從Intel、AMD、SUN、CISCO等國際老牌企業,到PicoChip(2000年成立)、Ambric(2003年成立)、Tilera(2004年成立)等新興公司,多核產品層出不窮;從超級計算機到PC機,從路由器等寬帶應用到多媒體等嵌入式市場,多核產品逐漸廣為人知。

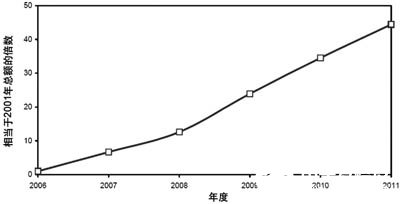

圖6 多核技術市場容量圖(來自VDC Research)

VDC Research于2007年發表了《多核計算的嵌入式應用:全球市場機會與需求分析》。報告分析了多核技術從2006年到2011年的市場需求走勢,如圖6所示。圖中的縱軸是以2006年總值為單位1,其他年份與2006年相比多核產品市場總額的倍數關系。研究表明,多核技術到2011年,嵌入式應用領域的市場總額將超過2007年的6倍,超過2006的44倍。如此快速的增長速度決定了我國不應該介入太晚,否則就只能再次走“產品跟蹤”的老路。

結語

包括NoC在內的多核技術是通用處理器技術升級的大方向已成為業內共識。多核技術是當代集成電路設計的戰略性技術,它以很低的功率消耗、較強的并行處理以及優異的計算性能,征服了人們對集成電路性能的追求,“成為業界的重要里程碑”(Intel總裁語)。

先進的NoC結構可以通過集成現有的百兆頻率核形成高性能多核處理器,大大降低了技術門檻,為中等設計公司帶來了機會,目前已有一批中等公司和新興公司在多核領域嶄露頭角,“國際寡頭”壟斷高性能處理器的格局正在發生變化。對我國現有設計能力而言,即使不能“一步登天”,但完全可以做到“所想即所得”,這亦為我國發展自主產權的高性能處理器產業提供了寶貴的契機。

責任編輯:gt

-

半導體

+關注

關注

334文章

27014瀏覽量

216291 -

soc

+關注

關注

38文章

4122瀏覽量

217936 -

晶體管

+關注

關注

77文章

9634瀏覽量

137848

發布評論請先 登錄

相關推薦

3G終端的關鍵技術和發展趨勢

廣電業務發展趨勢與業務捆綁技術

遠端射頻模塊關鍵技術創新及發展趨勢介紹

軟件無線電的功能結構、關鍵技術和難點以及應用和發展前景討論

傳感器將會有哪些發展趨勢?

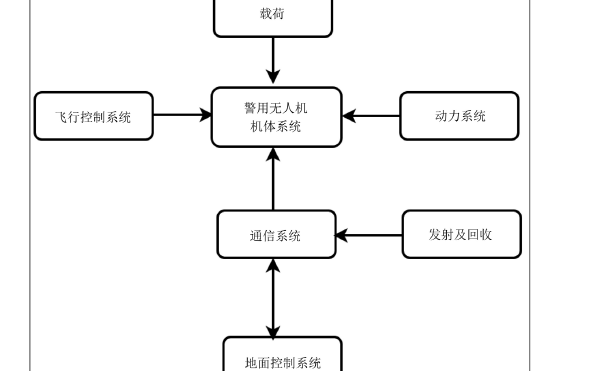

警用無人機關鍵技術及發展趨勢

NoC技術的應用優勢、關鍵技術難點及發展趨勢分析

NoC技術的應用優勢、關鍵技術難點及發展趨勢分析

評論