Ⅰ、概述

對于系統(tǒng)時(shí)鐘應(yīng)該都知道它的作用,就是驅(qū)動(dòng)整個(gè)芯片工作的心臟,如果沒有了它,就等于人沒有了心跳。

對于使用開發(fā)板學(xué)習(xí)的朋友來說,RCC系統(tǒng)時(shí)鐘這一塊知識估計(jì)沒怎么去配置過,原因在于開發(fā)板提供的晶振基本都是官方標(biāo)準(zhǔn)的時(shí)鐘頻率,使用官方的標(biāo)準(zhǔn)庫,這樣系統(tǒng)時(shí)鐘就是默認(rèn)的配置,也就是默認(rèn)的頻率。但對于自己設(shè)計(jì)開發(fā)板,或者想要改變系統(tǒng)時(shí)鐘頻率(如:降低功耗就需要降頻)的朋友來說,配置系統(tǒng)時(shí)鐘就有必要了。

關(guān)于時(shí)鐘這一塊對定時(shí)器(TIM、RTC、WDG等)相關(guān)的外設(shè)也比較重要,因?yàn)橐缶珳?zhǔn),就需要時(shí)鐘頻率精準(zhǔn)。

Ⅱ、關(guān)于時(shí)鐘

1.時(shí)鐘分類

STM32芯片(所有型號)的時(shí)鐘包含4類:

HSE(High Speed External)高速外部時(shí)鐘

HSI(High Speed Internal)高速內(nèi)部時(shí)鐘

LSE(Low Speed External)低速外部時(shí)鐘

LSI(Low Speed Internal)低速內(nèi)部時(shí)鐘

2.時(shí)鐘源

STM32芯片(所有型號)驅(qū)動(dòng)系統(tǒng)時(shí)鐘的時(shí)鐘源:

HSI內(nèi)部高速時(shí)鐘

HSE外部高速時(shí)鐘

PLLCLK倍頻時(shí)鐘

STM32具有以下兩個(gè)次級時(shí)鐘源:

32 kHz 低速內(nèi)部 RC (LSI RC),該 RC 用于驅(qū)動(dòng)獨(dú)立看門狗,也可選擇提供給 RTC 用于停機(jī)/待機(jī)模式下的自動(dòng)喚醒。

32.768 kHz 低速外部晶振( LSE 晶振),用于驅(qū)動(dòng) RTC 時(shí)鐘 (RTCCLK)。對于每個(gè)時(shí)鐘源來說,在未使用時(shí)都可單獨(dú)打開或者關(guān)閉,以降低功耗。

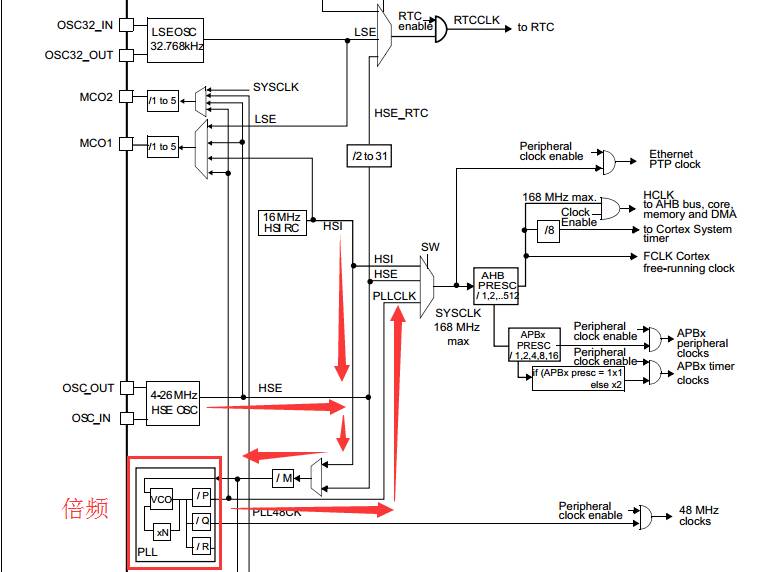

3.時(shí)鐘樹(框圖)

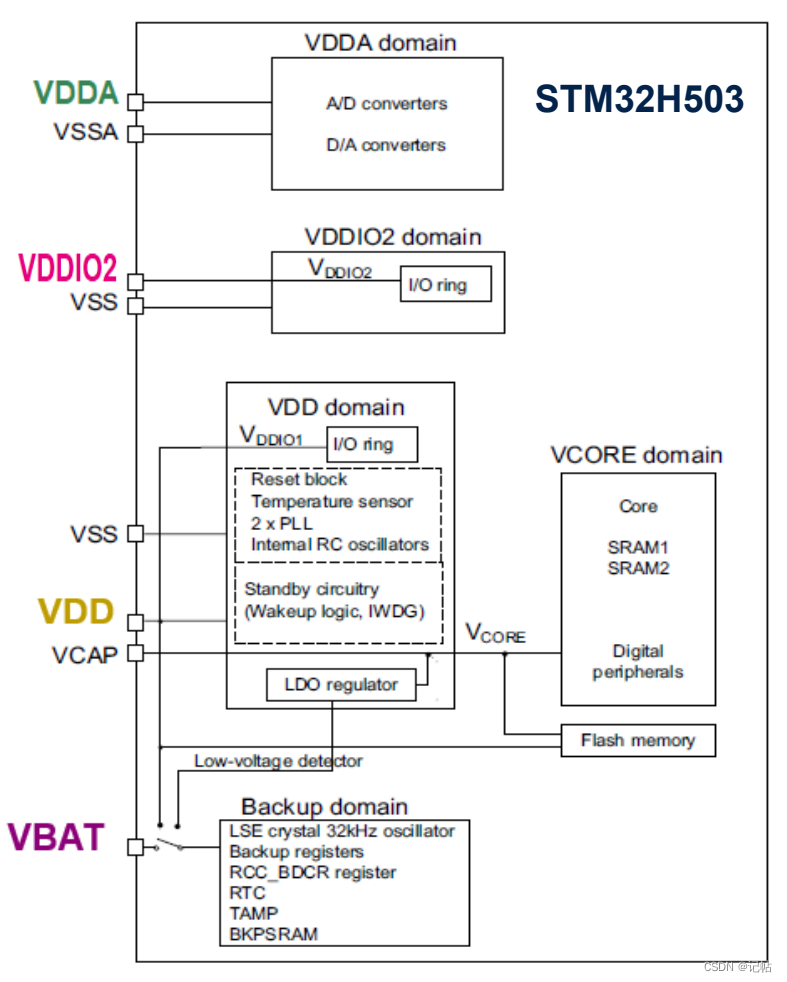

關(guān)于STM32的時(shí)鐘樹針對不同系列芯片可能存在差異。F0、F1和F3系列芯片(主流芯片,頻率相對較低)有很多相似的地方,F(xiàn)2和F4(高性能芯片)系列芯片有很多相似的地方。但是,F(xiàn)3芯片和F4芯片的時(shí)鐘樹之間卻存在很大差異,具體請看參考手冊RCC相關(guān)章節(jié)。

STM32時(shí)鐘控制器為應(yīng)用帶來了高度的靈活性,用戶在運(yùn)行內(nèi)核和外設(shè)時(shí)可選擇使用外部晶振或者使用振蕩器,既可采用最高的頻率,也可為以太網(wǎng)、 USB OTG FS 以及 HS、 I2S 和 SDIO等需要特定時(shí)鐘的外設(shè)保證合適的頻率。

以F417芯片為例:可通過多個(gè)預(yù)分頻器配置 AHB 頻率、高速 APB (APB2) 和低速 APB (APB1)。 AHB 域的最大頻率為 168 MHz。高速 APB2 域的最大允許頻率為 84 MHz。低速 APB1 域的最大允許頻率為 42 MHz。實(shí)際上輸出的最大時(shí)鐘可以適當(dāng)提高一點(diǎn),但為了保證在多種環(huán)境下,最好還是不要超過標(biāo)準(zhǔn)的最大值。

STM32F4xx 器件具有兩個(gè) PLL:

主 PLL (PLL) 由 HSE 或 HSI 振蕩器提供時(shí)鐘信號,并具有兩個(gè)不同的輸出時(shí)鐘:

第一個(gè)輸出用于生成高速系統(tǒng)時(shí)鐘(最高達(dá) 168 MHz)

第二個(gè)輸出用于生成 USB OTG FS 的時(shí)鐘 (48 MHz)、隨機(jī)數(shù)發(fā)生器的時(shí)鐘

專用 PLL (PLLI2S) 用于生成精確時(shí)鐘,從而在 I2S 接口實(shí)現(xiàn)高品質(zhì)音頻性能。

由于在 PLL 使能后主 PLL 配置參數(shù)便不可更改,所以建議先對 PLL 進(jìn)行配置,然后再使能(選擇 HSI 或 HSE 振蕩器作為 PLL 時(shí)鐘源,并配置分頻系數(shù) M、 N、 P 和 Q)。

PLLI2S 使用與 PLL 相同的輸入時(shí)鐘( PLLM[5:0] 和 PLLSRC 位為兩個(gè) PLL 所共用)。但是, PLLI2S 具有專門的使能/禁止和分頻系數(shù)( N 和 R)配置位。在 PLLI2S 使能后,配置參數(shù)便不能更改。

Ⅲ、代碼分析

以STM32F4x5、x7系列芯片為例來分析一下系統(tǒng)時(shí)鐘的配置。

參考軟件工程:

https://yunpan.cn/cRepWDShSK4yc訪問密碼 65b1

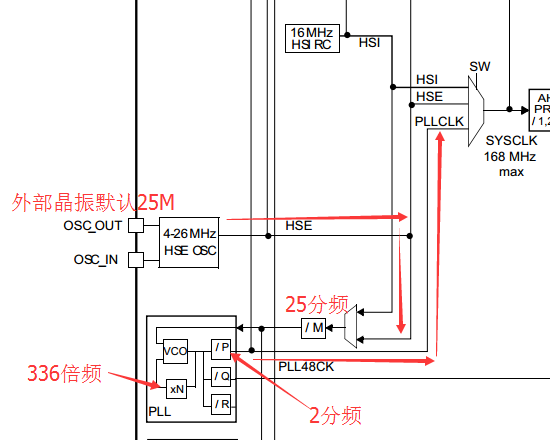

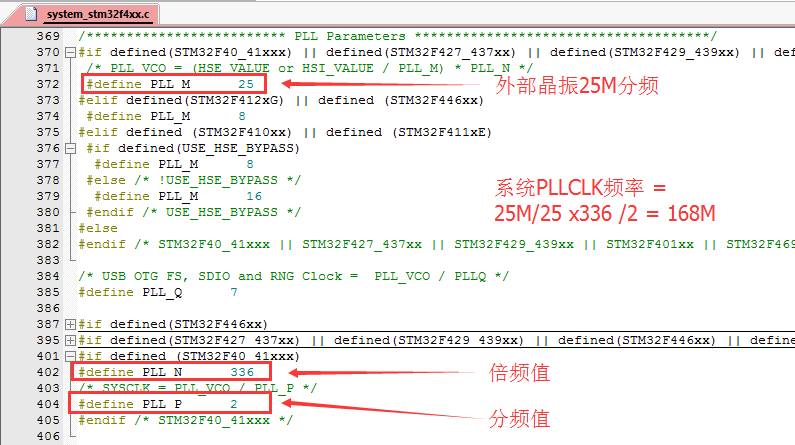

1.倍頻參數(shù)

結(jié)合上面時(shí)鐘樹和源代碼可以看得出來,系統(tǒng)時(shí)鐘PLLCLK的計(jì)算主要是配置PLL_M、PLL_N、PLL_P這三個(gè)參數(shù),最后168M是通過分頻、倍頻得出來的。

2.驗(yàn)證時(shí)鐘頻率

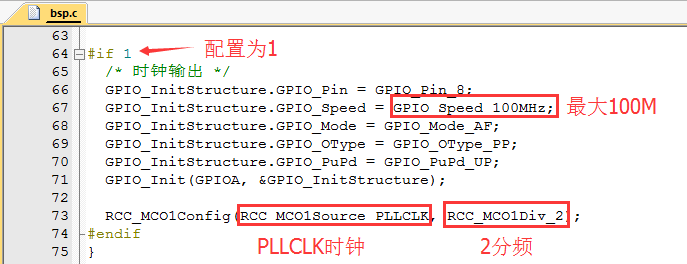

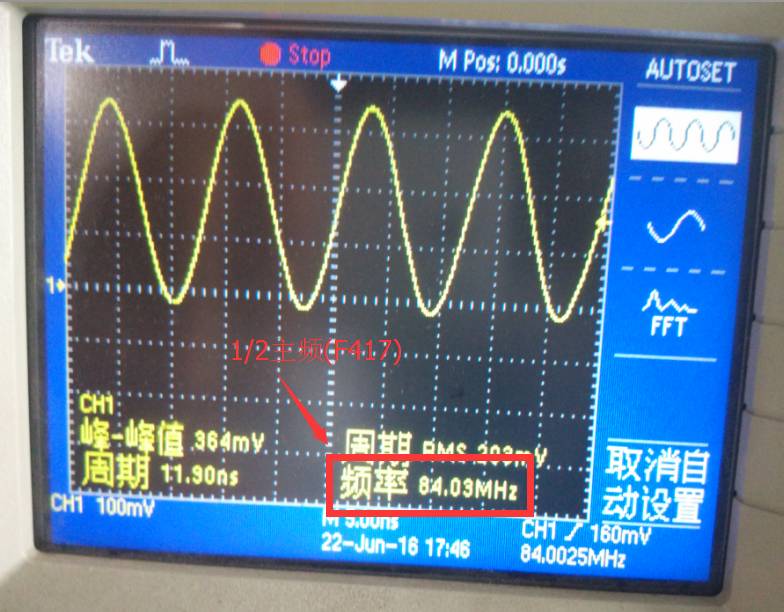

對于STM32芯片來說,驗(yàn)證系統(tǒng)時(shí)鐘最終運(yùn)行多大的速度,最準(zhǔn)確的驗(yàn)證方法的用示波器測試它的系統(tǒng)時(shí)鐘。

這里描述一下怎樣用示波器來測試系統(tǒng)時(shí)鐘。其實(shí)很簡單,就是在軟件代碼里面配置時(shí)鐘輸出(這里可以輸出多種類型的時(shí)鐘HSE、HSI、PLLCLK等),根據(jù)代碼配置不同,相應(yīng)輸出的時(shí)鐘就不同。請看源代碼:

我提供的代碼里面就有這一選項(xiàng),將定義配置為1,就打開了這個(gè)功能。時(shí)鐘輸出的參數(shù)有兩個(gè),時(shí)鐘源,分頻值。注意:這里的最大輸出時(shí)鐘是100M,所以PLLCLK時(shí)鐘分頻之后才能輸出,不然你用示波器檢測不到波形(我測試過了)。

最后輸出的波形如圖:

Ⅳ、說明

關(guān)于STM32的開發(fā),軟件兼容性是很好的,不要覺得你的芯片和我總結(jié)的實(shí)例有差異就不看了,其實(shí)是錯(cuò)誤的認(rèn)識,特別是同一個(gè)系列的芯片基本上程序都兼容,也就是可以互相使用。

-

RCC

+關(guān)注

關(guān)注

0文章

93瀏覽量

26895 -

Tim

+關(guān)注

關(guān)注

0文章

81瀏覽量

17873 -

STM32F4

+關(guān)注

關(guān)注

3文章

194瀏覽量

27991

發(fā)布評論請先 登錄

相關(guān)推薦

STM32F103×8/STM32F103×B MCU手冊

STM32項(xiàng)目實(shí)戰(zhàn):基于STM32F4的智能燈光控制系統(tǒng)(LVGL),附項(xiàng)目教程/源碼

CKS32F107xx系列時(shí)鐘系統(tǒng)具體配置方法講解

stm32f303VET6外部晶振Cubemax配置spi2導(dǎo)致時(shí)鐘系統(tǒng)故障怎么解決?

STM32F030F4的PA1引腳自閃爍是什么原因?qū)е碌模?/a>

STM32F070選擇內(nèi)部時(shí)鐘后外部上電復(fù)位有時(shí)點(diǎn)亮不了燈怎么解決?

關(guān)于STM32F103內(nèi)外部時(shí)鐘切換問題求解

求助,關(guān)于STM32F3系列啟動(dòng)時(shí)SWD的配置問題求解

RCC_ADCCLKConfig函數(shù)的ADC時(shí)鐘是默認(rèn)的嗎?

stm32f100用庫3.5如何讓配置系統(tǒng)時(shí)鐘,8MHz晶振輸入,如何配置為24MHz系統(tǒng)時(shí)鐘?

STM32F030時(shí)鐘沒有APB2, 為什么庫函數(shù)會有RCC_APB2PeriphClockCmd ?

stm32F0在hal庫時(shí)鐘初始化這里把HSI關(guān)掉了,為什么還可以擦寫Flash?

stm32cubemx無法配置32.768外部時(shí)鐘是為什么?

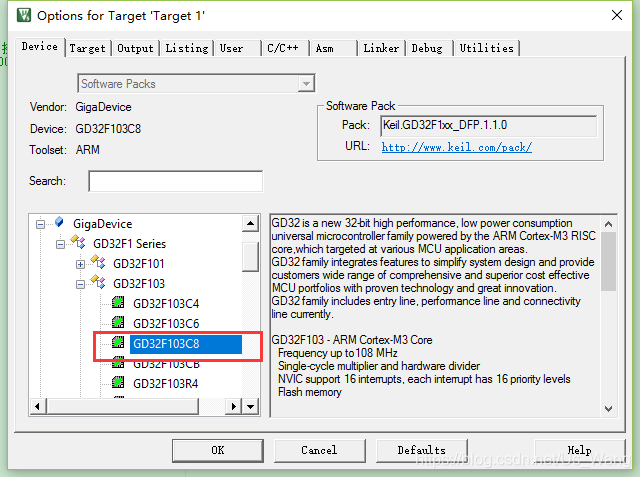

在GD32F103移植STM32F103代碼

STM32F4_ RCC系統(tǒng)時(shí)鐘配置及描述

STM32F4_ RCC系統(tǒng)時(shí)鐘配置及描述

評論