隨著云計算,大數據和人工智能技術應用,單靠CPU已經無法滿足各行各業的算力需求。海量數據分析、機器學習和邊緣計算等場景需要計算架構多樣化,需要不同的處理器架構和GPU,NPU和FPGA等異構計算技術協同,滿足特定領域的算法和專用計算需求。今天,筆者帶大家詳細了解下FPGA技術。

FPGA是英文Field Programmable Gate Array簡稱,即現場可編程門陣列。它是在PLA、PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

1、 FPGA簡介

FPGA普遍用于實現數字電路模塊,用戶可對FPGA內部的邏輯模塊和I/O模塊重新配置,以實現用戶的需求。它還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。可以毫不夸張的講,FPGA能完成任何數字器件的功能,下至簡單的74電路,上至高性能CPU,都可以用FPGA來實現。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法,或是硬件描述語言自由的設計一個數字系統。

2、FPGA發展史

FPGA的發展歷史如下圖所示。相對于PROM、PAL/GAL、CPLD而言,FPGA規模更大性能更高。

圖1 FPGA發展史

FPGA芯片主流生產廠家包括Xilinx、Altera、Lattice、Microsemi,其中前兩家的市場份額合計達到88%。目前FPGA主流廠商全部為美國廠商。國產FPGA由于研發起步較美國晚至少20年,目前還處于成長期,僅限于低端,在通信市場還沒有成熟應用。

2015年12月,Intel公司斥資167億美元收購了Altera公司。Altera被收購后不久即制定了英特爾處理器與FPGA集成的產品路線圖。這兩種產品集成的好處是可以提供創新的異構多核架構,適應例如人工智能等新市場的需求,同時能大幅縮減功耗。

圖2 FPGA在電信領域的應用歷史

FPGA在航天、軍工、電信領域有非常成熟和廣泛的應用。以電信領域為例,在電信設備一體機階段,FPGA由于其編程的靈活性以及高性能被應用網絡協議解析以及接口轉換。

在NFV(NetworkFunction Virtualization階段,FPGA基于通用服務器和Hypervisor實現網元數據面5倍的性能提升,同時能夠被通用Openstack框架管理編排。

在云時代,FPGA已經被作為基本IaaS資源在公有云提供開發服務和加速服務,AWS、華為、BAT均有類似通用服務提供。

截至目前,Intel的Stratix 10器件已被成功應用于微軟實時人工智能云平臺Brainwave項目。

3、兩家主流FPGA公司發展近況

Xilinx聚焦芯片領先和豐富的加速解決方案,通過開放策略獲得主流云平臺支持,確立了其在數據中心的領先地位。其UltraScale+系列FPGA領先友商1年多,使其在云平臺競爭中占領先機,其VU9P器件被大量應用于包括AWS、Baidu、Ali、Tencent及華為在內的多家公司的云計算平臺。

為滿足加速器領域對FPGA芯片日益遞增的性能需求,Xilinx已發布面向數據中心的下一代ACAP芯片架構、推出7nm Everest器件。此器件已不屬于傳統的FPGA,它集成了ARM、DSP、Math Engine處理器陣列等內核,將于2019年量產。相較于VU9P,Everest支持的AI處理性能將能提升20倍。

Intel則提供從硬件到平臺到應用的全棧解決方案,不開放硬件和平臺設計以避免生態碎片化,投入巨大但進展緩慢。

圖3 Xilinx產品系列圖

圖4 Intel(以Stratix系列為例)產品工藝年代

FPGA在數據中心服務器市場的實際應用中存在一定技術難點,具體包括如下幾方面:

1、編程門檻較高:硬件描述語言不同于軟件開發語言,需要開發者對底層硬件有著較深刻的認識;因此人才也就成為限制FPGA應用的一個重要因素。據了解,目前國內從事FPGA開發的人員初步估計大約兩萬多人。

2、集成難度較大:FPGA開發與應用需要軟硬件的協同,包括使用高級語言的系統建模、硬件代碼(電路)設計、硬件代碼仿真、底層驅動軟件與硬件邏輯的聯調等等。

3、開發周期相對軟件要長:硬件開發比軟件開發過程復雜,調試周期也被拉長。

4、很難獲取獨立邏輯IP。

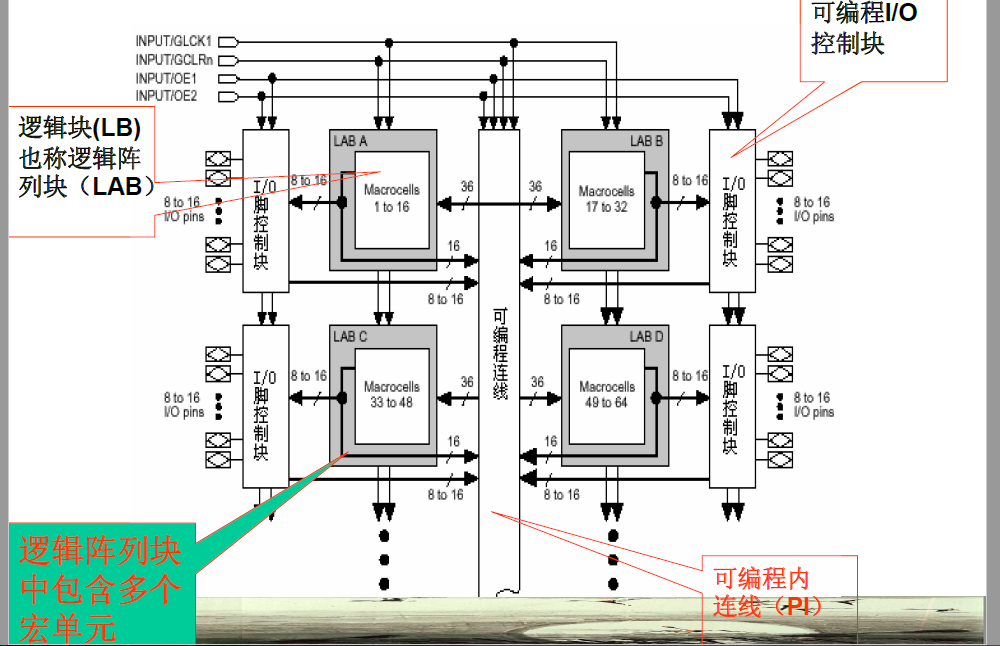

4、FPGA整體結構

FPGA架構主要包括可配置邏輯塊CLB(Configurable Logic Block)、輸入輸出塊IOB(Input Output Block)、內部連線(Interconnect)和其它內嵌單元四個部分。

CLB是FPGA的基本邏輯單元。實際數量和特性會依器件的不同而改變,但是每個CLB都包含一個由4或6個輸入、若干選擇電路(多路復用器等)和觸發器組成的可配置開關矩陣。開關矩陣具有高度的靈活性,經配置可以處理組合型邏輯、移位寄存器或 RAM。

FPGA可支持許多種I/O標準,因而可以為系統設計提供理想的接口橋接。FPGA 內的I/O按bank分組,每個bank能獨立支持不同的I/O標準。目前最先進的FPGA提供了十多個I/O bank,能夠提供靈活的I/O支持。

CLB 提供了邏輯性能,靈活的互連布線則負責在CLB和I/O之間傳遞信號。布線有幾種類型,從設計用于專門實現 CLB 互連(短線資源)、到器件內的高速水平和垂直長線(長線資源)、再到時鐘與其它全局信號的全局低skew布線(全局性專用布線資源)。一般,各廠家設計軟件會將互連布線任務隱藏起來,用戶根本看不到,從而大幅降低了設計復雜性。

內嵌硬核單元包括RAM、DSP、DCM(數字時鐘管理模塊)及其它特定接口硬核等,FPGA器件內部結構如下示意圖。

圖5 FPGA器件內部結構圖

一般來說,器件型號數字越大,表示器件能提供的邏輯資源規模越大。在FPGA器件選型時,用戶需要對照此表格,根據業務對邏輯資源(CLB)、內部BlockRAM、接口(高速Serdes對數)、數字信號處理(DSP硬核數)以及今后擴展等多方面的需求,綜合考慮項目最合適的邏輯器件。

5、FPGA開發流程

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如下圖所示,包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

1、功能定義/器件選型:在FPGA設計項目開始之前,必須有系統功能的定義和模塊的劃分,另外就是要根據任務要求,如系統的功能和復雜度,對工作速度和器件本身的資源、成本、以及連線的可布性等方面進行權衡,選擇合適的設計方案和合適的器件類型。

2、 設計輸入:設計輸入指使用硬件描述語言將所設計的系統或電路用代碼表述出來。最常用的硬件描述語言是Verilog HDL。

3、 功能仿真:功能仿真指在邏輯綜合之前對用戶所設計的電路進行邏輯功能驗證。仿真前,需要搭建好測試平臺并準備好測試激勵,仿真結果將會生成報告文件和輸出信號波形,從中便可以觀察各個節點信號的變化。如果發現錯誤,則返回設計修改邏輯設計。常用仿真工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS等軟件。

4、 邏輯綜合:所謂綜合就是將較高級抽象層次的描述轉化成較低層次的描述。綜合優化根據目標與要求優化所生成的邏輯連接,使層次設計平面化,供FPGA布局布線軟件進行實現。就目前的層次來看,綜合優化是指將設計輸入編譯成由與門、或門、非門、RAM、觸發器等基本邏輯單元組成的邏輯連接網表,而并非真實的門級電路。

真實具體的門級電路需要利用FPGA制造商的布局布線功能,根據綜合后生成的標準門級結構網表來產生。為了能轉換成標準的門級結構網表,HDL程序的編寫必須符合特定綜合器所要求的風格。常用的綜合工具有Synplicity公司的Synplify/Synplify Pro軟件以及各個FPGA廠家自己推出的綜合開發工具。

5、布局布線與實現:布局布線可理解為利用實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能鏈接的布線通道進行連線,并產生相應文件(如配置文件與相關報告);實現是將綜合生成的邏輯網表配置到具體的FPGA芯片上。由于只有FPGA芯片生產商對芯片結構最為了解,所以布局布線必須選擇芯片開發商提供的工具。

6、編程調試:設計的最后一步就是編程調試。芯片編程是指產生使用的數據文件(位數據流文件,Bitstream Generaon),將編程數據加載到FPGA芯片中;之后便可進行上板測試。最后將FPGA文件(如.bit文件)從電腦下載到單板上的FPGA芯片中。

6、如何使用FPGA

FPGA開發完畢,最終得到驗證好的加載文件。輸出加載文件后,即可開始正常業務處理和驗證(以軟件加載方式為例,描述整個過程)

1、邏輯加載;

2、單板軟件加載邏輯后,需要復位邏輯;

3、復位完成后,軟件需等待等待一段時間至邏輯鎖相環工作穩定;

4、軟件啟動對邏輯的外部RAM、內部Block RAM、DDRC等的自檢操作;

5、軟件完成自檢以后,對邏輯所有可寫RAM空間及寄存器進行初始化操作;

6、初始化完畢,軟件參考邏輯芯片手冊配置表項及寄存器;

7、邏輯準備好,可以開始處理業務。

7、FPGA適用場景

FPGA適合非規則性多并發、密集計算及協議解析處理場景,例如人工智能、基因測序、視頻編碼、數據壓縮、圖片處理、網絡處理等各領域的加速。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601902 -

云計算

+關注

關注

39文章

7744瀏覽量

137208 -

人工智能

+關注

關注

1791文章

46872瀏覽量

237600

發布評論請先 登錄

相關推薦

FPGA教程之CPLD與FPGA的基礎知識說明

嵌入式系統基礎知識講解

Oracle數據庫基礎知識講解

FPGA基礎知識----FPGA 簡介

FPGA的簡介發展歷和使用等基礎知識講解

FPGA的簡介發展歷和使用等基礎知識講解

評論