據IC Insights發布的最新2020 McClean報告顯示,半導體行業研發的投入將在2024年出現明顯成效——包括轉向EUV光刻,低于3納米制程技術,3D芯片堆疊技術和先進封裝在內的技術挑戰有望提升研發增長率。

半導體業務的定義是快速的技術變化以及需要在新材料的研發方面保持高水平的投資,用于日益復雜的芯片設計的創新制造工藝以及先進的IC封裝技術。

根據新版提供的數據,盡管半導體行業的整合在過去五年中降低了研發支出的增長率,但長期趨勢是自1980年代以來研發支出的年度增長放緩。于2020年1月IC Insights發布的《 McClean報告—集成電路產業的全面分析和預測》的內容。然而,技術挑戰包括3D芯堆疊技術,先進工藝中的極紫外光刻技術的發展以及增長產品的復雜性預計將在2019-2024年期間將R&D預算提高一點點(圖1)。

數據顯示,研發支出趨勢涵蓋了集成設備制造商(IDM),無晶圓廠芯片供應商和純晶圓代工廠的支出,并且不包括涉及半導體相關技術的其他公司和組織,例如生產設備和材料供應商,包裝和制造商。測試服務提供商,大學,政府資助的實驗室和行業合作社,例如比利時的IMEC,法國的CAE-Leti研究所,***的工業技術研究院(ITRI)和美國的Sematech財團, 2015年合并為紐約州立大學(SUNY)理工學院。

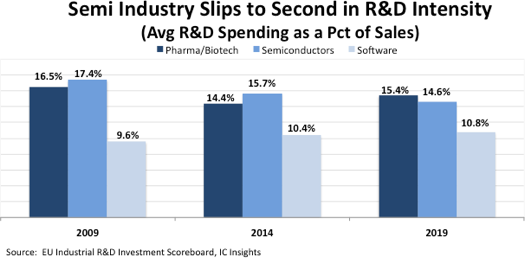

根據IC Insights收集的數據,自1990年代以來,半導體行業在研發強度方面一直領先于所有其他主要工業領域,每年在研發上的支出平均約占總銷售額的15%。然而,在過去的三年中,半導體行業的研發銷售額占總銷售額的比例在2017年下滑至13.5%,在2018年下滑至13.0%,這主要是由于內存IC的收入增長非常快。該行業的研發/銷售比例在2019年反彈至14.6%,當時內存IC收入下降了33%,整個半導體市場下降了12%。根據歐盟工業研發投資記分卡報告中的一項全球調查,制藥和生物技術領域的研發/銷售比率為15.4%,在2019年排名中名列第一(圖2)。

在過去的41年中(1978-2019),R&D支出平均占半導體銷售額的14.6%。自2000年以來,半導體研發支出占全球半導體銷售額的百分比超過了四年(2000年,2010年,2017年和2018年)的歷史平均水平。在這四年中,較低的研發與銷售比率與收入增長的優勢更多地聯系在一起,而不是研發支出的劣勢。

-

半導體

+關注

關注

334文章

27019瀏覽量

216347 -

3D芯片

+關注

關注

0文章

52瀏覽量

18414 -

EUV

+關注

關注

8文章

604瀏覽量

85968

發布評論請先 登錄

相關推薦

HyperLith軟件 EUV光刻交流

日本與英特爾合建半導體研發中心,將配備EUV光刻機

日本大學研發出新極紫外(EUV)光刻技術

SK海力士5層堆疊3D DRAM制造良率已達56.1%

SK海力士五層堆疊的3D DRAM生產良率達到56.1%

三星將推出GDDR7產品及280層堆疊的3D QLC NAND技術

SOLIDWORKS 3D CAD 2024的10大新增功能

機構發布2024年全球半導體市場八大預測:增長率可達20%

什么是摩爾定律,“摩爾定律2.0”從2D微型化到3D堆疊

到2024年,半導體研發將促EUV光刻、3納米、3D芯片堆疊技術增長

到2024年,半導體研發將促EUV光刻、3納米、3D芯片堆疊技術增長

評論