E-ELT是歐洲南方天文臺(European Southern Observatory,ESO)倡議建設(shè)的一個直徑42米的望遠(yuǎn)鏡,用于為天文學(xué)領(lǐng)域的最新研究探索提供支持。該主反射鏡由984個鏡面組成。如圖1所示,每個鏡面,可以通過三個位置執(zhí)行器實(shí)時移動,用于對支撐結(jié)構(gòu)因重力、溫度、風(fēng)動等因素所導(dǎo)致的變形進(jìn)行補(bǔ)償。西班牙航空系統(tǒng)公司(Compa?ía Espa?ola de Sistemas Aeronauticos,CESA)負(fù)責(zé)對三個位置執(zhí)行器原型的機(jī)械結(jié)構(gòu)進(jìn)行設(shè)計和開發(fā),而加納利天體物理學(xué)研究所(Instituto de Astrofísica de Canarias,IAC)則負(fù)責(zé)對系統(tǒng)中的電子裝置、軟件和伺服控制進(jìn)行開發(fā)。

執(zhí)行器開發(fā)中最具挑戰(zhàn)性的要求包括:達(dá)到15mm的行程、支撐90kg的重物、追蹤緩坡信號時實(shí)現(xiàn)170納米以下的均方根誤差 (root mean square error,RMSE)、1 kHz外部位置控制指令更新率,以及確保極低的延遲和抖動(如圖1)。

執(zhí)行器機(jī)械設(shè)計方案分為兩個階段。在粗調(diào)階段:使用無刷電機(jī),實(shí)現(xiàn)一個大的調(diào)整行程和較粗的分辨率;在微調(diào)階段:使用一個音圈電機(jī),實(shí)現(xiàn)高分辨率、高帶寬和小調(diào)整行程。每個調(diào)整階段都將使用獨(dú)立的電源設(shè)備、反饋傳感器和伺服控制器。粗調(diào)和微調(diào)控制器協(xié)調(diào)工作,最終實(shí)現(xiàn)執(zhí)行器的位置調(diào)整。

電子裝置和軟件是位于PXI機(jī)箱中,用于實(shí)現(xiàn)整體協(xié)調(diào)、外部命令管理、功能調(diào)試和伺服控制,運(yùn)行有實(shí)時操作系統(tǒng)的控制器,可以實(shí)現(xiàn)極大的靈活性和計算能力。其中,快速微調(diào)伺服控制器通過NI PXI - 7842R現(xiàn)場可編程門陣列(FPGA)模塊實(shí)現(xiàn);而緩慢的粗調(diào)控制器則是通過NI PXIe - 8130控制器實(shí)現(xiàn)。此外,該軟件設(shè)計分為兩個部分:執(zhí)行器的嵌入式控制軟件和一個望遠(yuǎn)鏡模擬器,后者可以作為輔助工具,用于模擬望遠(yuǎn)鏡計算機(jī)與執(zhí)行器之間的交互。

執(zhí)行器軟件

執(zhí)行器控制軟件是由位于NI PXIe- 8130實(shí)時控制器中的程序模塊和位于PXI-7842R FPGA智能數(shù)據(jù)采集卡中的程序模塊組成。實(shí)時控制器中的程序模塊中含有每個驅(qū)動器的具體功能,包括:初始狀態(tài)檢查、狀態(tài)機(jī)、狀態(tài)字、錯誤寄存器以及配置參數(shù)管理。同時也包含其它任務(wù),包括:通過串行外設(shè)接口(serial peripheral interface,SPI)收發(fā)外部命令來檢查FPGA卡的輸入;通過CAN或CANopen總線控制無刷電機(jī)驅(qū)動器,來實(shí)現(xiàn)粗調(diào)伺服控制;管理用于調(diào)試的循環(huán)緩沖器并同步接收來自FPGA FIFO的數(shù)據(jù),通過UDP/ IP讀取傳感器的反饋。FPGA卡則實(shí)現(xiàn)了SPI從屬端的功能,負(fù)責(zé)微調(diào)伺服控制、模擬信號寫入和讀取,并且通過FIFO將數(shù)據(jù)傳遞至實(shí)時控制器來實(shí)現(xiàn)同步。

望遠(yuǎn)鏡模擬器

為根據(jù)要求對位置執(zhí)行器進(jìn)行測試,我們開發(fā)了另外一個軟件,用來模擬望遠(yuǎn)鏡計算機(jī)(通過SPI接口與位置執(zhí)行器通信)。這一計算機(jī)扮演著SPI主控器的角色,而執(zhí)行器則位于SPI從屬端。此模擬程序以1 kHz的速率發(fā)送數(shù)百萬個的位置命令,并以1KHz的速率通過SPI總線讀取從屬端的反應(yīng)。此外,它還以5kHz的速率從一個安裝于機(jī)械測試臺上的附加外部位置傳感器讀取數(shù)據(jù),用于對位置執(zhí)行器的內(nèi)部傳感器進(jìn)行交叉檢查。這三個循環(huán)都需要以優(yōu)于200us的精度進(jìn)行同步,對數(shù)據(jù)進(jìn)行二進(jìn)制格式的存儲以用于離線分析。在長為一小時的測試中,所存儲的文件將大于100 MB。圖2中的圖形用戶界面顯示了命令管理、以及附加外部位置傳感器數(shù)據(jù)的時域和頻域同步顯示。

我們所采用的解決方案使用一個帶有數(shù)字I/O的NI PCI -7811R FPGA卡,安裝在基于Windows XP的電腦上(如圖2所示)。

兼具實(shí)時性和靈活性

執(zhí)行器的電子控制裝置和軟件包含多種接口(如圖3所示),而且其中大部分接口都可以在開發(fā)的初始階段進(jìn)行更改,包括:

* 帶有4MHz時鐘的SPI接口,能夠每ms接受一個外部命令

* CAN總線接口,對粗調(diào)電機(jī)進(jìn)行控制,并使用CANopen作為應(yīng)用層協(xié)議,提供諸如行程限位和硬件報警等信息

* 模擬輸出接口,控制微調(diào)音圈電機(jī)

* 模擬輸入接口,監(jiān)視微調(diào)音圈電機(jī)的當(dāng)前狀態(tài)

* 基于以太網(wǎng)的UDP/IP協(xié)議接口,讀取外部位置傳感器的電子裝置中的數(shù)據(jù)

* 基于以太網(wǎng)的TCP/IP協(xié)議接口,下載并調(diào)試輔助的離線數(shù)據(jù)

* 數(shù)字輸入接口,用于讀取原點(diǎn)位置傳感器的數(shù)據(jù)

使用這些接口需要極大的靈活性。

如下功能則需要實(shí)時特性:

* 使用SPI從屬設(shè)備以80MHz的速率讀取數(shù)字輸入,在幾微秒的時間內(nèi)對一個新的外部命令作出響應(yīng)

* 執(zhí)行快速微調(diào)伺服控制,包括基于若干個2kHz到10kHz濾波器的PID(比例微分積分 - proportional integral derivative)控制,并且在開發(fā)的最后階段可調(diào)

* 同步并存儲二進(jìn)制數(shù)據(jù)文件,用于SPI外部命令(1kHz)、音圈電機(jī)當(dāng)前模擬輸入(2kHz)、基于以太網(wǎng)的位置傳感器數(shù)據(jù)采集(2–10 kHz)和伺服控制器內(nèi)部變量(2–10 kHz)等數(shù)據(jù)的離線分析

使用商業(yè)現(xiàn)成可用的(commercial off-the-shelf,COTS)的平臺滿足這些要求,需要在靈活性和實(shí)時性之間作出折衷。然而,通過使用NI硬件,并通過LabVIEW Real-Time 和 LabVIEW FPGA模塊進(jìn)行編程,我們所獲得的實(shí)時特性超出了上述要求,而且各種接口均可調(diào)整,無需犧牲靈活性(圖3)。

結(jié)論

NI PXI平臺幫助我們在保持系統(tǒng)靈活性和實(shí)時性的同時顯著減少了開發(fā)時間,而且能夠滿足電子裝置/軟件方面的設(shè)計要求。使用LabVIEW,可以在同一個軟件環(huán)境中對實(shí)時控制器和FPGA模塊進(jìn)行編程,幫助我們快速集成系統(tǒng),并確保系統(tǒng)獨(dú)立、可靠。此外。此外,NI工程師為我們提供了快速且有效的幫助,讓我們更快完成開發(fā)。

責(zé)任編輯:gt

-

PXI

+關(guān)注

關(guān)注

17文章

276瀏覽量

87838 -

執(zhí)行器

+關(guān)注

關(guān)注

5文章

375瀏覽量

19326

發(fā)布評論請先 登錄

相關(guān)推薦

牛頓反射式望遠(yuǎn)鏡DIY過程全解

操作天文望遠(yuǎn)鏡哪這些必須注意

我想請教大神指導(dǎo)關(guān)于望遠(yuǎn)鏡圖像如何提取

[原創(chuàng)]第一次從望遠(yuǎn)鏡里看到土星的環(huán)(手機(jī)+望遠(yuǎn)鏡拍攝)

望遠(yuǎn)鏡測距儀的原理是什么?

利用MatLab對天文望遠(yuǎn)鏡系統(tǒng)進(jìn)行仿真設(shè)計研究

基于STM32的虛擬天文望遠(yuǎn)鏡

基于OptiStruct的望遠(yuǎn)鏡主框架拓?fù)鋬?yōu)化設(shè)計

望遠(yuǎn)鏡棱鏡內(nèi)部結(jié)構(gòu)及原理圖

望遠(yuǎn)鏡的原理

使用LabVIEW控制探索頻道望遠(yuǎn)鏡

分塊式空間望遠(yuǎn)鏡波前探測與控制

羅曼太空望遠(yuǎn)鏡將替代哈勃望遠(yuǎn)鏡

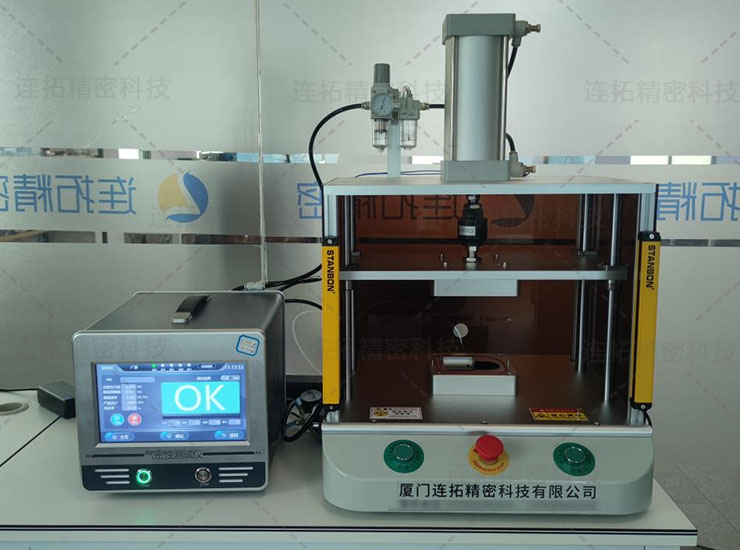

望遠(yuǎn)鏡氣密性檢測案例實(shí)拍

使用LabVIEW和PXI硬件對望遠(yuǎn)鏡的機(jī)械結(jié)構(gòu)進(jìn)行設(shè)計和開發(fā)

使用LabVIEW和PXI硬件對望遠(yuǎn)鏡的機(jī)械結(jié)構(gòu)進(jìn)行設(shè)計和開發(fā)

評論