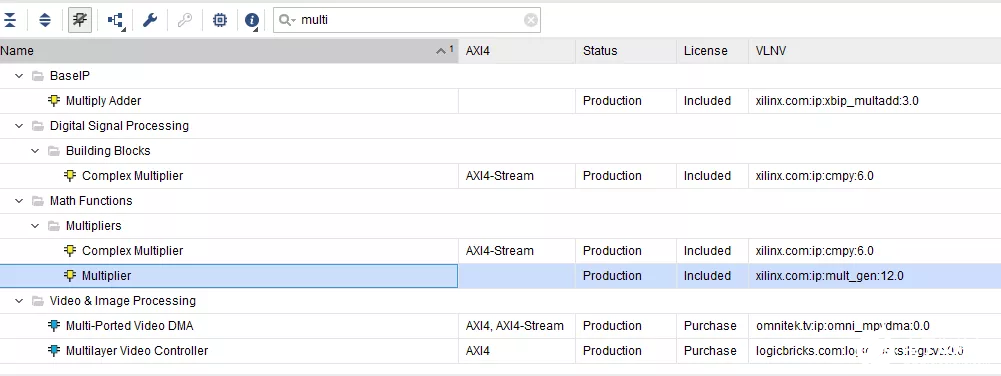

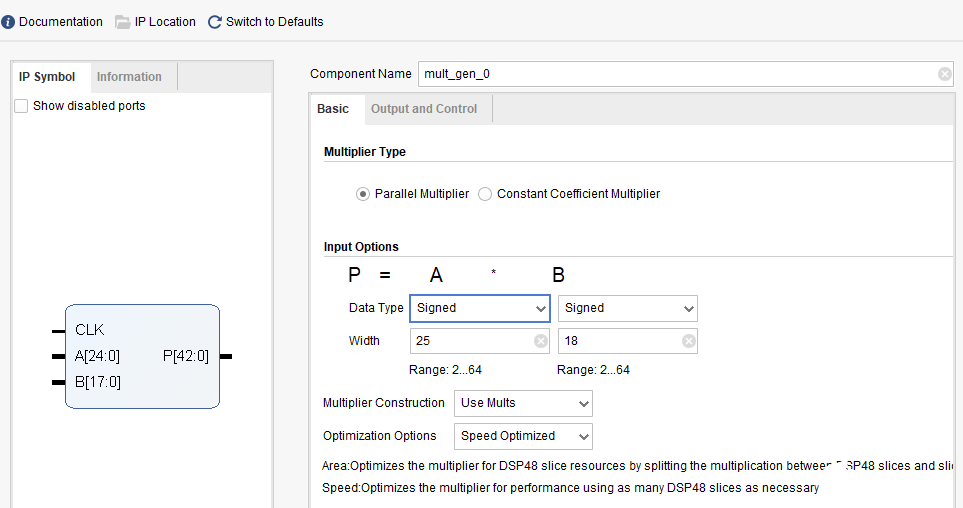

FPGA中乘法器是很稀缺的資源,但也是我們做算法必不可少的資源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我們可以通過調IP Core的方式或者原語的方式來進行乘法操作。在里面可以設置有符號還是無符號數乘法。

當然,我們也可以直接使用*符合來進行乘法,對于無符號的乘法

reg [7:0] ubyte_a; reg [7:0] ubyte_b; (* use_dsp48="yes" *) output reg[15:0] u_res; always @ ( posedge clk ) begin if(rst) u_res <= 'b0; else u_res <= ubyte_a * ubyte_b; end

有符號乘法可以在Verilog中使用signed來標注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* use_dsp48="yes" *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res <= 'b0;

else

res <= byte_a * byte_b;

end

當然我們也要理解有符號數乘法的原理,其實就是擴位乘法,把高位都補充為符號位。

有符號數乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* use_dsp48="yes" *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul <= 'b0;

else

res_manul <= {{8{byte_a[7]}},ubyte_a} * {{8{ubyte_b[7]}},ubyte_b};

end

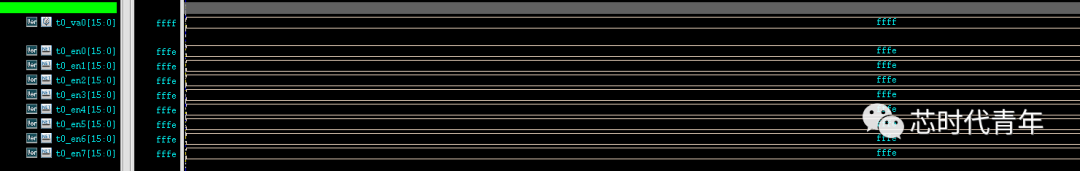

關于乘法輸出的位寬,我們知道,兩個8bits的無符號數乘法,結果的位寬是16bits,但對于兩個8bits有符號數的乘法,只要兩個數不同時為-128,即二進制0b1000_0000,那么輸出結果的高兩位都是符號位,我們只需要取低15bits即可。因此,如果我們可以保證兩個輸入的乘數不會同時為有符號數所能表示的負數最小值,那么乘法結果的高兩位都是符號位,只取其中一位即可。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

552文章

7962瀏覽量

348311 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602045

發布評論請先 登錄

相關推薦

采用Xilinx FPGA的AFE79xx SPI啟動指南

電子發燒友網站提供《采用Xilinx FPGA的AFE79xx SPI啟動指南.pdf》資料免費下載

發表于 11-15 15:28

?0次下載

FPGA Verilog HDL有什么奇技巧?

今天給大俠帶來在FPAG技術交流群里平時討論的問題答疑合集(九),以后還會多推出本系列,話不多說,上貨。

交流問題(一)

Q:Verilog 有什么奇技淫巧?

A:在 Verilog 中,以下這些

發表于 09-12 19:10

EasyGo 實時仿真 NetBox 操作指南

▍基于FPGA自定義模型的控制與仿真 02 操作指南 ? ? 首先,找到NetBox的電源接口,接入電源。 短按「開關」

LM70 SPI/MICROWIRE 10位帶符號數字溫度傳感器數據表

電子發燒友網站提供《LM70 SPI/MICROWIRE 10位帶符號數字溫度傳感器數據表.pdf》資料免費下載

發表于 08-14 09:28

?0次下載

LM12454/LM12458/LM12H458 12位符號數據采集系統數據表

電子發燒友網站提供《LM12454/LM12458/LM12H458 12位符號數據采集系統數據表.pdf》資料免費下載

發表于 07-22 09:25

?0次下載

matlab與FPGA數字信號處理系列 Verilog 實現并行 FIR 濾波器

能涉及到對有符號數的處理問題

https://zhuanlan.zhihu.com/p/342108822 作者:FPGA探索者,

發表于 05-24 07:48

常用的電氣元件符號有哪些?

以上是一些常見的電氣元件符號,它們在電路圖和設計中起著至關重要的作用。通過使用標準化的電氣元件符號,可以確保電路圖的準確性和可靠性,從而提高工程設計的效率和質量。

verilog中數據的符號屬性(有符號數和無符號數)探究根源

為了省流,還是先甩結論。有符號數和無符號數的最本質區別就是:符號位的識別和高位拓展。除此之外,另一個區別就是從人的角度如何如何讀這個數,或者說$display(%d)打印時打印的值是什

FPGA有符號數乘法操作指南

FPGA有符號數乘法操作指南

評論