邊界掃描測試(Boundary scan)是為了解決印制電路板(PCB)上芯片與芯片之間的互連測試而提出的一種解決方案。它與內部掃描有明顯的區別,前者是在電路的輸入/輸出端口增加掃描單元,并將這些掃描單元連成掃描通路,后者是將電路中普通的時序單元替換成為具有掃描能力的時序單元,再將它們連成掃描通路。

一、邊界掃描測試原理

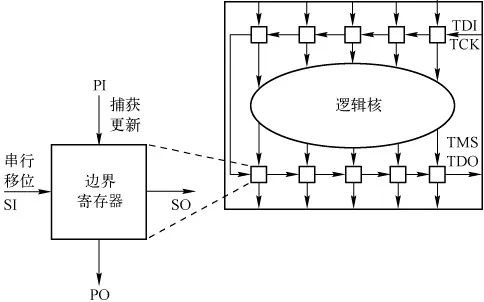

邊界掃描的原理是在核心邏輯電路的輸入和輸出端口都增加一個寄存器,通過將這些I/O上的寄存器連接起來,可以將數據串行輸入被測單元,并且從相應端口串行讀出。在這個過程中,它可以實現3方面的測試。

首先是芯片級測試,即可以對芯片本身進行測試和調試,使芯片工作在正常功能模式,通過輸入端輸入測試矢量,并通過觀察串行移位的輸出響應進行調試。

其次是板級測試,檢測集成電路和PCB之間的互連。實現原理是將一塊PCB上所有具有邊界掃描的IC中的掃描寄存器連接在一起,通過一定的測試矢量,可以發現元件是否丟失或者擺放錯誤,同時可以檢測引腳的開路和短路故障。

最后是系統級測試,在板級集成后,可以通過對板上CPLD或者Flash的在線編程,實現系統級測試。

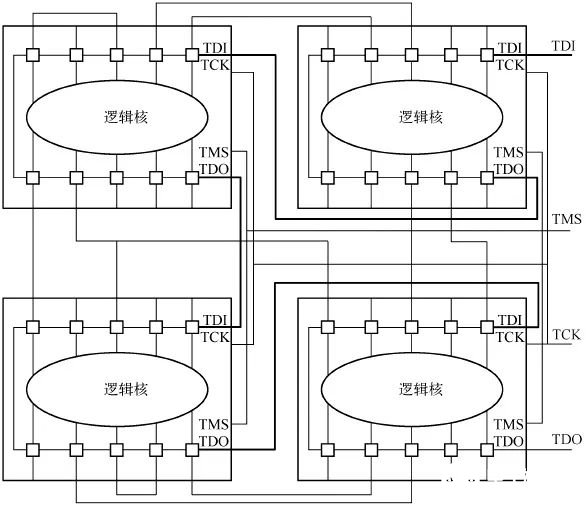

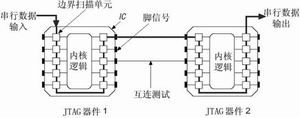

其中,最主要的功能是進行板級芯片的互連測試,如圖1所示。

圖1 基于邊界掃描的板級互連測試

二、IEEE 1149.1標準

邊界掃描是歐美一些大公司聯合成立的一個組織——聯合測試行動小組(JTAG),為了解決印制電路板(PCB)上芯片與芯片之間互連測試而提出的一種解決方案。由于該方案的合理性,它于1990年被IEEE采納而成為一個標準,即IEEE 1149.1。該標準規定了邊界掃描的測試端口、測試結構和操作指令。

1.IEEE 1149.1結構

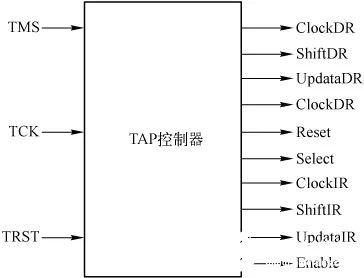

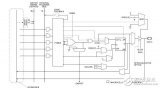

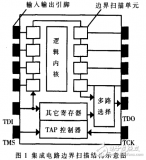

IEEE 1149.1結構如圖2所示,其主要包括TAP控制器和寄存器組。其中,TAP控制器如圖3所示;寄存器組包括邊界掃描寄存器、旁路寄存器、標志寄存器和指令寄存器,主要端口為TCK、TMS、TDI、TDO,另外還有一個用戶可選擇的端口TRST。

圖2 IEEE 1149.1結構

圖3 TAP控制器

2.端口定義如下

(1)TCK(Test Clock)

邊界掃描設計中的測試時鐘是獨立的,因此與原來IC或PCB上的時鐘是無關的,也可以復用原來的時鐘。

(2)TMS(Test Mode Select)

由于在測試過程中,需要有數據捕獲、移位、暫停等不同的工作模式,因此需要有一個信號來控制。在IEEE 1149.1中,僅有這樣一根控制信號,通過特定的輸入序列來確定工作模式,采用有限狀態機來實現。該信號在測試時鐘TCK的上升沿采樣。

(3)TDI(Test Data In)

以串行方式輸入的數據TDI有兩種。一種是指令信號,送入指令寄存器;另一種是測試數據(激勵、輸出響應和其他信號),它輸入到相應的邊界掃描寄存器中去。

(4)TDO(Test Data Out)

以串行輸出的數據也有兩種,一種是從指令寄存器移位出來的指令,另一種是從邊界掃描寄存器移位出來的數據。

除此之外,還有一個可選端口TRST,為測試系統復位信號,作用是強制復位。

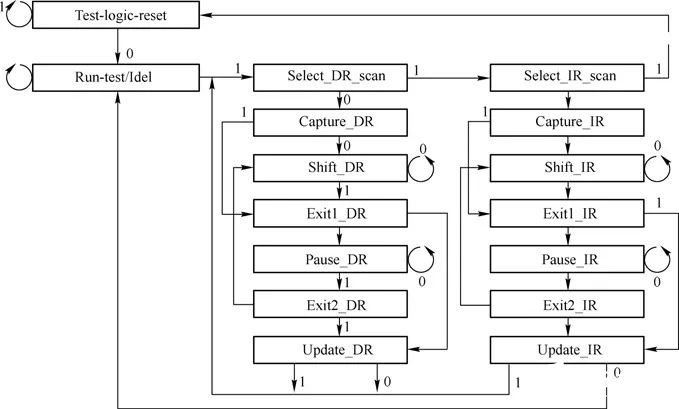

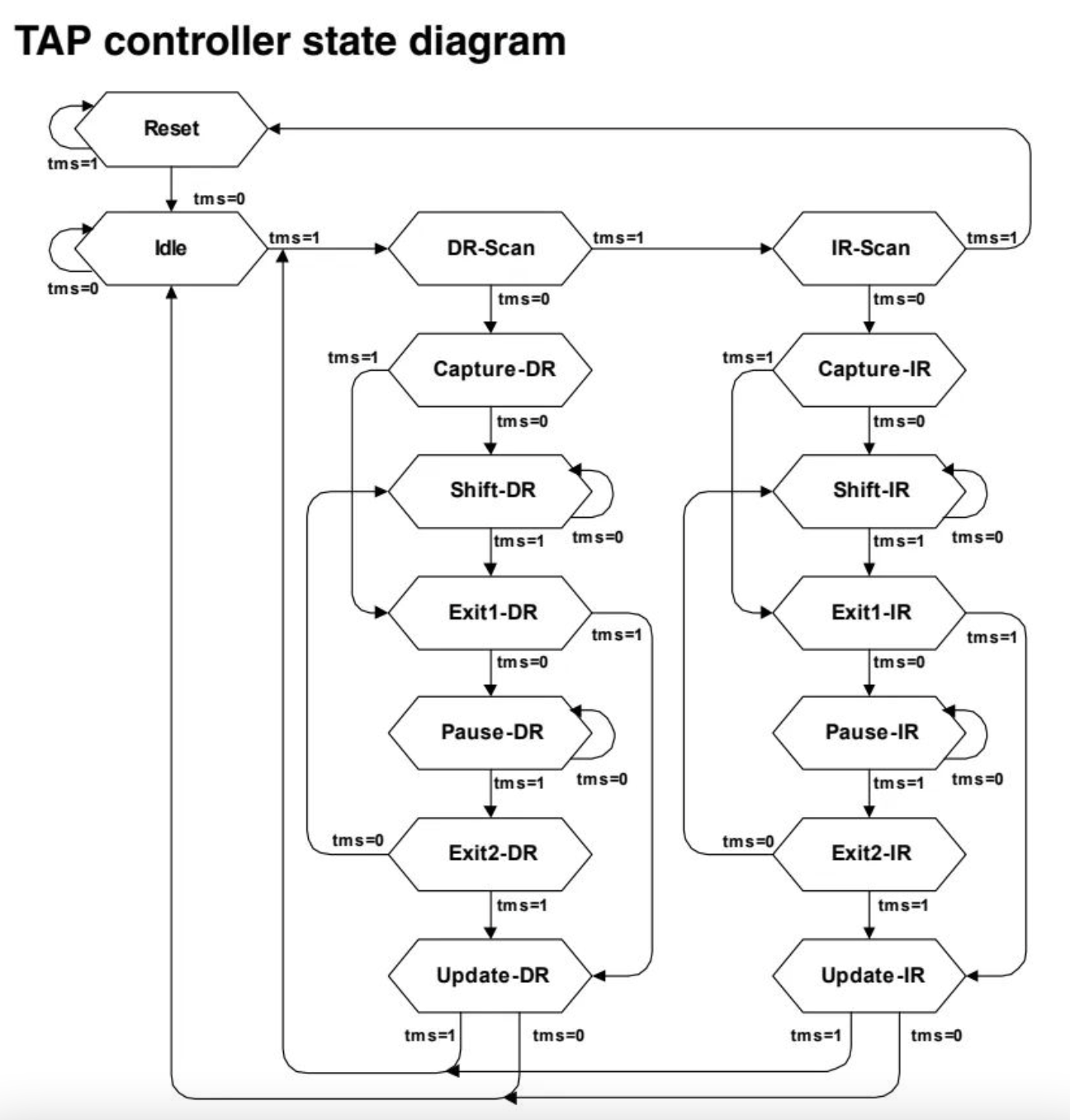

3.TAP控制器

TAP控制器的作用是將串行輸入的TMS信號進行譯碼,使邊界掃描系統進入相應的測試模式,并且產生該模式下所需的各個控制信號。IEEE 1149.1的TAP控制器由有限狀態機來實現,圖4所示為狀態轉移圖。DR表示數據寄存器,IR表示指令寄存器。

圖4 TAP控制器的狀態轉移圖

4.寄存器組

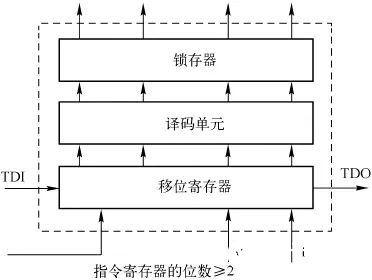

(1)指令寄存器(IR,Instruction Register)

如圖5所示,指令寄存器由移位寄存器和鎖存器組成,長度等于指令的長度。IR可以連接在TDI和TDO的兩端,經TDI串行輸入指令,并且送入鎖存器,保存當前指令。在這兩部分中有個譯碼單元,負責識別當前指令。由于JTAG有3個強制指令,所以該寄存器的寬度至少為2位。

圖5 指令寄存器

(2)旁路寄存器(BR,Bypass Register)

旁路寄存器也可以直接連接在TDI和TDO兩端,只有1位組成。若一塊PCB上有多個具有邊界掃描設計的IC,可將每個IC中的邊界掃描鏈串接起來。如果此時需要對其中的某幾個IC進行測試,就可以通過BYPASS指令來旁路無須測試的IC。如圖6所示,如果需要測試Chip2和Chip3,則在TDI輸入110000就可以配置旁路寄存器,此時Chip1的旁路寄存器被置位,表示該芯片在測試過程中被旁路。

圖6 旁路寄存器使用舉例

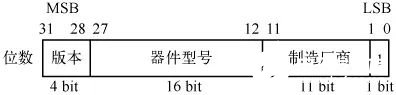

(3)標志寄存器(IDR,Identification Register)

如圖7所示,在一般的邊界掃描設計中,都包含一個固化有該器件標志的寄存器,它是一個32位的標準寄存器,其內容有關于該器件的版本號、器件型號、制造廠商等信息,用途是在PCB生產線上,可以檢查IC的型號和版本,以便檢修和替換。

在器件標志寄存器的標準格式中,最低位(第0位)為1,用于識別標志寄存器和旁路寄存器的標志位。第1~11位為制造廠商的標識位。根據國際聯合電子器件工程委員會所提出的方案,這11位共允許有2032個生產廠家的標識。第12~27位表示器件的型號,總計可以表示216=65536種不同的型號。余下的4位表示同一型號器件的不同版本。

圖7 標志寄存器

(4)邊界掃描寄存器

邊界掃描寄存器是邊界掃描中最重要的結構單元,它完成測試數據的輸入、輸出鎖存和移位過程中必要的數據操作。其工作在多種模式,首先是滿足掃描鏈上的串行移位模式,其次是正常模式下電路的數據捕獲和更新,如圖8所示。

圖8 邊界掃描寄存器

利用邊界掃描寄存器可提供如下的主要測試功能:

? 對被測IC的外部電路進行測試,如可測IC之間的互連,此時可以使用外部測試指令EXTEST;

? 使用INTEST進行被測電路的內部自測;

? 對輸入、輸出信號進行采樣和更新,此時可以完全不影響核心邏輯電路的工作狀態。

5.相關指令

JTAG規定了3個強制指令:EXTEST、BYPASS、SAMPLE/PRELOAD。

(1)EXTEST:外測試指令

外測試指令主要用于測試IC和PCB之間的連線或邊界掃描設計以外的邏輯電路。執行該指令的主要操作為,將測試矢量串行移位至邊界掃描寄存器,以激勵被測的連線或外部邏輯電路,同時該寄存器又捕獲響應數據,并串行移出測試結果,以便檢查。

(2)BYPASS:旁路指令

這是一條由1組成的全1指令串,它的功能是選擇該IC中的旁路寄存器BR,決定該IC是否被測試。

(3)SAMPLE/PRELOAD:采樣/預裝指令

采樣指令用于不影響核心邏輯正常工作的條件下,將邊界掃描設計中的并行輸入端的信號捕獲至邊界掃描寄存器中,在測試時,通過采樣指令捕獲所測試邏輯電路的響應。預裝指令功能與采樣基本相同,只是此時裝入邊界掃描寄存器的數據是編程者已知或確定的。除了上述必須的指令外,JTAG還定義了部分可選擇的指令:INTEST、IDCODE、RUNBIST、CLAMP、HIGHZ。

? INTEST為內測試指令,用于測試核心邏輯電路。執行過程與外測試指令基本相似,只是由于被測對象的位置恰好相反,它的激勵端和響應測試端正好相反。

? IDCODE指令用于從標志寄存器中取出標志代碼。

? RUNBIST為運行自測試指令,用來執行被測邏輯的自測試功能,需要保證電路本身具有

? 自測結構。

? CLAMP是組件指令,有兩個功能,一是使旁路寄存器為0,另一個是使邊界掃描寄存器BSR的輸出為一組給定的固定電平。

? HIGHZ是輸出高阻指令,可以使IC的所有輸出端都呈高阻狀態,即無效狀態。

三、邊界掃描測試策略和相關工具

1.板級測試策略

利用邊界掃描IEEE 1149.1進行板級測試的策略分以下3步。

① 根據IEEE 1149.1標準建立邊界掃描的測試結構。

② 利用邊界掃描測試結構,對被測部分之間的連接進行矢量輸入和響應分析。這是板級測試的主要環節,也是邊界掃描結構的主要應用。可以用來檢測由于電氣、機械和溫度導致的板級集成故障。

③ 對單個核心邏輯進行測試,可以初始化該邏輯并且利用其本身的測試結構。

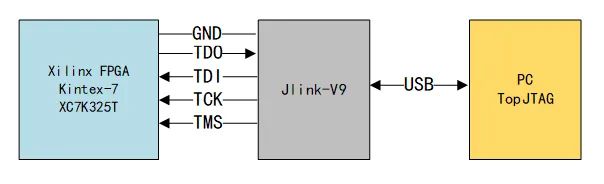

2.相關EDA工具

工業界主要采用的邊界掃描工具為Mentor的BSDArchitect和Synopsys的BSD Compiler。以后者為例,其主要設計流程如圖9所示。該流程會生成BSDL文件,該文件是邊界掃描測試描述文件,該文件內容包括引腳定義和邊界掃描鏈的組成結構。一般的ATE可以識別該文件,并自動生成相應的測試程序,完成芯片在板上的漏電流等參數的測試。

圖9 邊界掃描設計流程

責任編輯:gt

-

pcb

+關注

關注

4292文章

22764瀏覽量

393150 -

測試

+關注

關注

8文章

4921瀏覽量

125930 -

電路板

+關注

關注

140文章

4808瀏覽量

96070

發布評論請先 登錄

相關推薦

基于邊界掃描的電路板快速測試系統設計

基于廣義特征分析與邊界掃描技術的混合信號測試系統

VLSI邊界掃描測試故障診斷

基于邊界掃描技術的板級測試分析

邊界掃描測試解決方案的原理及應用分析

邊界掃描測試解決方案的原理及應用分析

評論