2020年開(kāi)篇伊始,全球半導(dǎo)體先進(jìn)制程之戰(zhàn)新的交鋒已然火花四射。

從華為、蘋(píng)果打響7nm旗艦手機(jī)芯片第一槍開(kāi)始,7nm芯片產(chǎn)品已成百花齊放之勢(shì),而5nm芯片也將在今年下半年正式首秀。

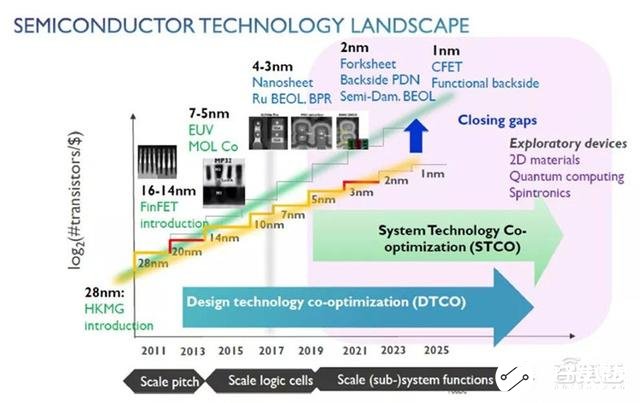

10nm、7nm、5nm、3nm……這些逐漸縮小的芯片制程數(shù)字,正是全球電子產(chǎn)品整體性能不斷進(jìn)化的核心驅(qū)動(dòng)力。

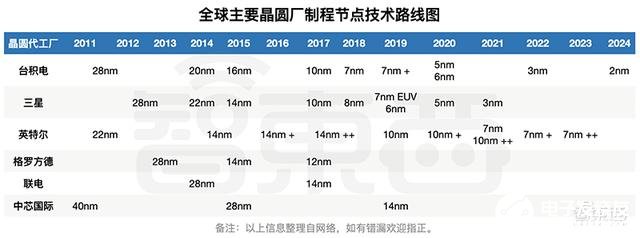

通往更先進(jìn)制程的道路猶如攀登高峰,飆高的技術(shù)難度和研發(fā)成本將大多數(shù)芯片代工廠攔在半山腰,全球唯有臺(tái)積電、三星、英特爾還在向峰頂沖刺。

就在剛剛過(guò)去4個(gè)月,三星、臺(tái)積電和英特爾接連密集釋放關(guān)于更先進(jìn)制程的新訊息。

三星首款3nm芯片研發(fā)成功,臺(tái)積電3nm芯片晶體管密度達(dá)2.5億/mm,英特爾官宣制程回歸兩年更新周期。

▲全球主要晶圓廠制程節(jié)點(diǎn)技術(shù)路線圖

與此同時(shí),作為過(guò)去十年芯片制程演進(jìn)的關(guān)鍵功臣,F(xiàn)inFET之父、美國(guó)加州大學(xué)伯克利分校教授胡正明被授予國(guó)際電氣與電子工程學(xué)會(huì)授予2020年IEEE榮譽(yù)勛章。

在全球備戰(zhàn)3nm及更先進(jìn)制程的關(guān)鍵節(jié)點(diǎn),本文圍繞晶體管結(jié)構(gòu)、光刻、沉積與刻蝕、檢測(cè)、封裝等五大關(guān)鍵環(huán)節(jié),探討全球先進(jìn)制程沖刺戰(zhàn)中更高階的核心技術(shù)及玩家格局。

▲邁向1nm節(jié)點(diǎn)的技術(shù)路線圖(圖源:Imec)

一、世界上最燒錢(qián)長(zhǎng)跑:芯片制程進(jìn)階之路

什么是芯片制程?制程用來(lái)描述芯片晶體管柵極寬度的大小,納米數(shù)字越小,說(shuō)明晶體管密度越大,芯片性能就越高。

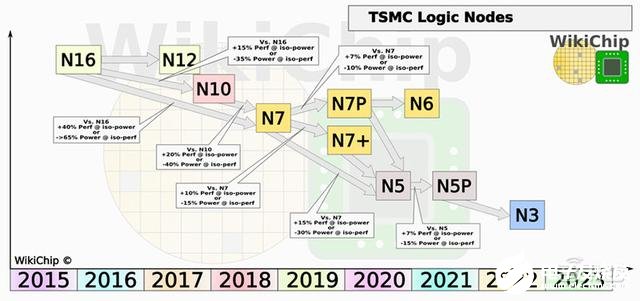

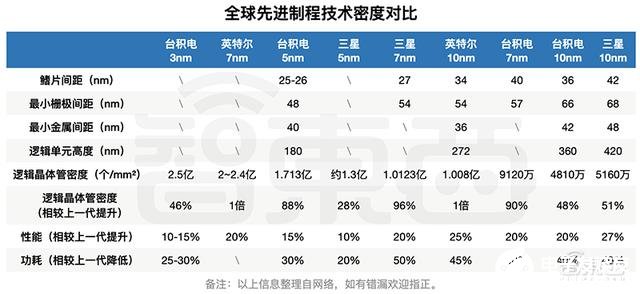

例如,臺(tái)積電7nm芯片的典型代表蘋(píng)果A13、高通驍龍865和華為麒麟990,每平方毫米約有1億個(gè)晶體管。隨后臺(tái)積電5nm、3nm芯片進(jìn)一步將每平方毫米的晶體管數(shù)量進(jìn)一步提升至1.713億個(gè)、2.5億個(gè)。

▲臺(tái)積電制程工藝節(jié)點(diǎn)路線圖(圖源:WikiChip)

伴隨著制程的進(jìn)化,5nm比7nm芯片性能提升15%,功耗降低30%;3nm又比5nm芯片性能提升10-15%,功耗降低25-30%。

由于各家對(duì)制程工藝的命名法則不同,相同納米制程下,并不能對(duì)各廠商的制程技術(shù)進(jìn)展做直觀比較。比如英特爾10nm的晶體管密度與臺(tái)積電7nm、三星7nm的晶體管密度相當(dāng)。

▲全球先進(jìn)制程技術(shù)對(duì)比

從制程最新進(jìn)展來(lái)看,一邊是臺(tái)積電三星在5nm/3nm等先進(jìn)制程上你追我趕,另一邊英特爾則韜光養(yǎng)晦循序漸進(jìn)地走向7nm。

5nm方面,臺(tái)積電已經(jīng)拿到蘋(píng)果和華為的旗艦手機(jī)芯片訂單,下半年開(kāi)啟量產(chǎn),有望在其2020年?duì)I收占比達(dá)10%。

三星在5nm制程則相對(duì)落后,目前正加速韓國(guó)華城5nm生產(chǎn)工廠V1的建設(shè),預(yù)計(jì)6月底前完成生產(chǎn)線建設(shè),今年年底前實(shí)現(xiàn)量產(chǎn)。

據(jù)外媒報(bào)道,三星與谷歌正合作開(kāi)發(fā)采用三星5nm LPE工藝的定制Exynos芯片組,將搭載于谷歌的Pixel智能手機(jī)、Chrome OS設(shè)備甚至數(shù)據(jù)中心服務(wù)器中。

3nm方面,臺(tái)積電3nm制程預(yù)計(jì)2021年開(kāi)始試生產(chǎn),并于2022年下半年開(kāi)始量產(chǎn)。三星原計(jì)劃2021年大規(guī)模量產(chǎn)3nm工藝,但受當(dāng)前疫情影響,不確定量產(chǎn)時(shí)間是否會(huì)推遲。

為什么挺進(jìn)先進(jìn)制程的玩家屈指可數(shù)呢?主要源于兩大門(mén)檻:資本和技術(shù)。

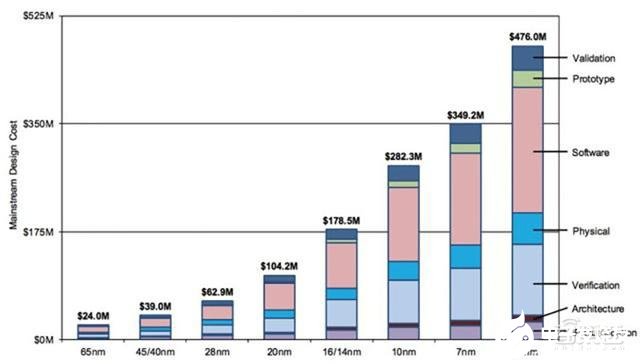

制程工藝的研發(fā)和生產(chǎn)成本逐代上漲。根據(jù)市場(chǎng)研究機(jī)構(gòu)International Business Strategies(IBS)的數(shù)據(jù),3nm芯片的設(shè)計(jì)費(fèi)用約達(dá)5-15億美元,興建一條3nm產(chǎn)線的成本約為150-200億美元。

兩年前臺(tái)積電為3nm工藝計(jì)劃投資6000億新臺(tái)幣,折合近200億美元。單是從資金數(shù)目來(lái)看,很多中小型晶圓廠就玩不起。

▲不同工藝下的典型芯片流片成本圖,28nm后成本開(kāi)始迅速上升

更高的研發(fā)和生產(chǎn)成本,對(duì)應(yīng)的是更難的技術(shù)挑戰(zhàn)。

每當(dāng)制程工藝逼近物理極限,晶體管結(jié)構(gòu)、光刻、沉積、刻蝕、檢測(cè)、封裝等技術(shù)的創(chuàng)新與協(xié)同配合,對(duì)芯片性能天花板的突破起到?jīng)Q定性作用。

二、摩爾定律的續(xù)命關(guān)鍵:晶體管結(jié)構(gòu)從FinFET走向GAA

晶體管在芯片中起到“開(kāi)關(guān)”作用,能通過(guò)影響相互的狀態(tài)傳遞信息。晶體管的柵極控制著電流能否從源極流向漏極,電子流過(guò)晶體管相當(dāng)于“開(kāi)”,電子不流過(guò)晶體管相當(dāng)于“關(guān)”。

隨著晶體管尺寸縮小,源極和柵極間的溝道不斷縮小,當(dāng)溝道縮短到一定程度時(shí),即便不加電壓,源極和漏極也因間距過(guò)小而互通,即產(chǎn)生“漏電”現(xiàn)象,晶體管則失去“開(kāi)關(guān)”的功能,無(wú)法實(shí)現(xiàn)邏輯電路。

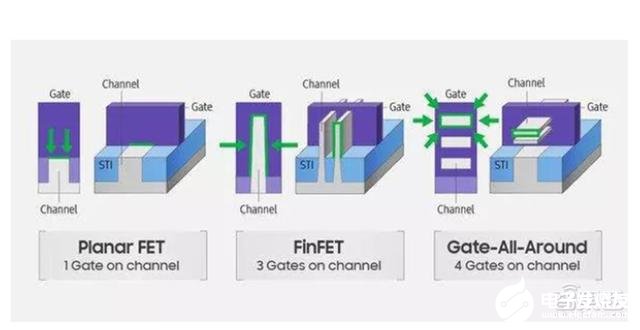

▲晶體管結(jié)構(gòu)進(jìn)化路線圖

1、從平面晶體管到FinFET

幾十年來(lái),基于平面(Planar)晶體管的芯片一直是市場(chǎng)上最先進(jìn)的設(shè)備。然而制程技術(shù)發(fā)展到22nm以下節(jié)點(diǎn)后,平面晶體管開(kāi)始遇到源極漏極間距過(guò)近的瓶頸。

此時(shí),華裔科學(xué)家胡正明教授于1999年發(fā)明的3D鰭式場(chǎng)效晶體管(FinFET),成為延續(xù)摩爾定律的革命性技術(shù),在過(guò)去十年間,為基于邏輯的工藝技術(shù)創(chuàng)新做出了核心貢獻(xiàn)。

英特爾在2011年轉(zhuǎn)向22nm FinFET。FinFET的立體構(gòu)造將漏極和源極由水平改為垂直,溝道被柵極三面環(huán)繞,不僅增厚絕緣層,而且增加接觸面積,避免漏電現(xiàn)象的發(fā)生。

相比平面晶體管,F(xiàn)inFET在工藝節(jié)點(diǎn)減小時(shí),能做到更好的性能和電壓縮放,切換速度和電流密度均顯著提升。

▲從平面晶體管到FinFET再到GAAFET的演變

FinFET已經(jīng)歷16nm/14nm和10nm/7nm兩個(gè)工藝世代,今年采用臺(tái)積電5nm FinFET晶體管工藝的芯片預(yù)計(jì)將在下半年問(wèn)世。

在衡量技術(shù)成熟度、性能和成本等因素后,臺(tái)積電的3nm首發(fā)沿用FinFET晶體管方案。

2、GAAFET:走向3nm及更先進(jìn)工藝

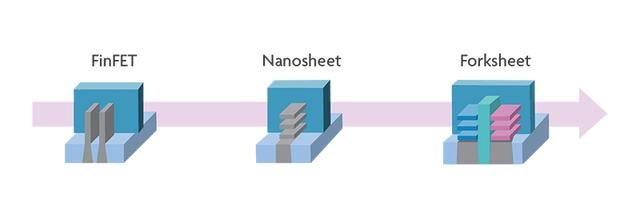

隨著深寬比不斷拉高,F(xiàn)inFET逼近物理極限,為了制造出密度更高的芯片,環(huán)繞式柵極晶體管(GAAFET,Gate-All-Ground FET)成為新的技術(shù)選擇。

三星、臺(tái)積電、英特爾均引入GAA技術(shù)的研究,其中三星已經(jīng)先一步將GAA用于3nm芯片。

不同于FinFET,GAAFET的溝道被柵極四面包圍,溝道電流比三面包裹的FinFET更加順暢,能進(jìn)一步改善對(duì)電流的控制,從而優(yōu)化柵極長(zhǎng)度的微縮。

三星3nm采用的GAA技術(shù)名為多橋通道FET(MBCFET,Multi-Bridge Channel FET)。這是一種納米片F(xiàn)ET(nanosheet FET),可通過(guò)用納米片替換納米線周?chē)臇艠O,實(shí)現(xiàn)每堆更大的電流。

不過(guò)納米片F(xiàn)ET當(dāng)下還面臨一些挑戰(zhàn),包括n/p不平衡、底部板的有效性、內(nèi)部間隔、柵極長(zhǎng)度控制和器件覆蓋。

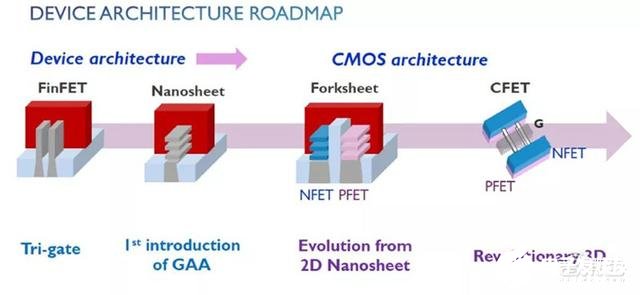

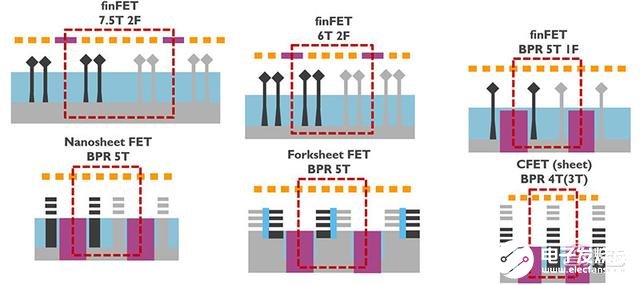

▲從FinFET到Nanosheet再到Forksheet的演變

微電子研究中心(Imec)正在開(kāi)發(fā)面向2nm的forksheet FET。

與nFET和pFET使用不同器件的現(xiàn)有GAAFET不一樣的是,在forksheet FET中,nFET和pFET都集成在同一結(jié)構(gòu)中,間距更小并減少密集縮放。

Imec的2nm forksheet具有42nm的接觸柵極間距(CPP)和16nm的金屬間距,均低于Nanosheet 45nm的接觸柵極間距和30nm的金屬間距。

Complementary FET(CFET)是另一種類(lèi)型的GAA器件,由兩個(gè)單獨(dú)的納米線FET(p型和n型)組成。一般pFET堆疊在nFET的頂部,消除了n-p分離的瓶頸,減少了電池有效面積。

去年11月,英特爾首席執(zhí)行官Bob Swan曾提到,英特爾的3nm也將采用CFET。

但CFET及相關(guān)的晶體管也存在散熱等挑戰(zhàn),還需要更多時(shí)間來(lái)開(kāi)發(fā),在各環(huán)節(jié)需要新的技術(shù)和設(shè)備。

▲從FinFET到nanosheet再到forksheet和CFET

三、更精細(xì)的芯片“刻刀”:高數(shù)值孔徑EUV

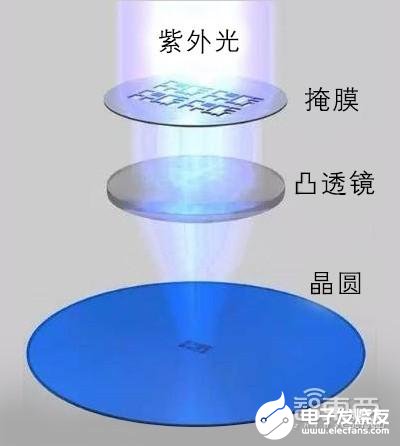

負(fù)責(zé)“雕刻”電路圖案的核心制造設(shè)備是光刻機(jī),它是芯片制造階段最核心的設(shè)備之一,光刻機(jī)的精度決定了制程的精度。

光刻機(jī)的運(yùn)作原理是:先把設(shè)計(jì)好的芯片圖案印在掩膜上,接著用激光光束穿過(guò)印著圖案的掩膜和光學(xué)鏡片,將芯片圖案曝光在帶有光刻膠涂層的硅片上。

此時(shí),涂層被光照到之處發(fā)生反應(yīng)溶解,沒(méi)有被照到之處保持不變,掩膜上的圖案就被轉(zhuǎn)移到芯片光刻膠涂層上。

▲光刻原理簡(jiǎn)示

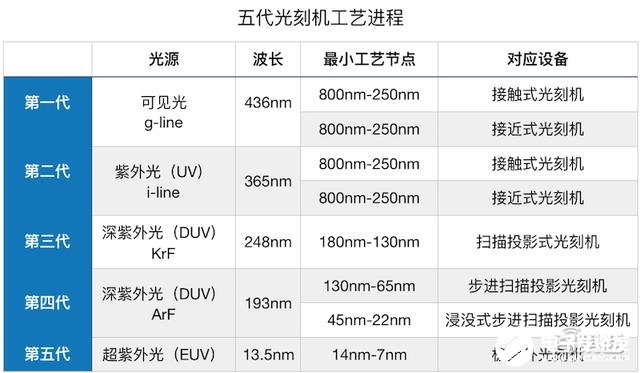

目前193nm浸沒(méi)式光刻是應(yīng)用最廣且最成熟的技術(shù),在22/16/14/10nm節(jié)點(diǎn),主要芯片制造商均使用基于193nm浸沒(méi)式光刻系統(tǒng)的雙重成像(double patterning)技術(shù)。

到7nm及更先進(jìn)的技術(shù)節(jié)點(diǎn)時(shí),則需要波長(zhǎng)更短的極紫外(EUV)光刻技術(shù)來(lái)實(shí)現(xiàn)更小的制程。而荷蘭ASML是全球唯一有能力制造EUV光刻機(jī)的廠商。

面向3nm及更先進(jìn)的工藝,芯片制造商或?qū)⑿枰环N稱為高數(shù)值孔徑EUV(high-NA EUV)的EUV光刻新技術(shù)。

Imec和ASML成立了聯(lián)合研究實(shí)驗(yàn)室,專(zhuān)注于后3nm節(jié)點(diǎn)的納米級(jí)元件制造藍(lán)圖,具體分為兩個(gè)階段:

第一階段開(kāi)發(fā)并加速EUV技術(shù)導(dǎo)入量產(chǎn),第二階段共同探索下一代high-NA EUV技術(shù)潛力,以制造出更小型的納米級(jí)元件,推動(dòng)3nm以后的半導(dǎo)體微縮制程。

根據(jù)ASML年報(bào),他們正在研發(fā)的下一代極紫外光刻機(jī)將采用high-NA技術(shù),有更高的數(shù)值孔徑、分辨率和覆蓋能力,較當(dāng)前的EUV光刻機(jī)將提高70%。

值得一提的是,英特爾的3nm節(jié)點(diǎn)與ASML的High-NA EUV光刻機(jī)設(shè)備的量產(chǎn)時(shí)間相吻合,大約在2024年前后。

▲ASML 預(yù)測(cè)半導(dǎo)體制程升級(jí)規(guī)劃

針對(duì)后3nm工藝,Imec重點(diǎn)投入的研發(fā)領(lǐng)域包括光阻技術(shù)、光罩的防塵薄膜技術(shù)、工藝優(yōu)化。

一方面,更高的光阻劑往往會(huì)增加缺陷率,光阻技術(shù)還需進(jìn)一步改進(jìn)以降低缺陷率。

另一方面,透明度等方面的挑戰(zhàn)致使EUV的光罩防塵薄膜發(fā)展相對(duì)緩慢。

幸運(yùn)的是,現(xiàn)有的EUV掩模工具足以用于3nm及更高的工藝。

四、兼顧有機(jī)與無(wú)機(jī)材料:沉積和刻蝕從原子層到分子層

為了將微電子器件造的更小,芯片制造商必須把越來(lái)越多的電路塞進(jìn)更小的薄膜和3D結(jié)構(gòu)中,這對(duì)與半導(dǎo)體工藝兼容的沉積和刻蝕技術(shù)提出了更高的要求。

薄膜沉積是指在硅片襯底上生成特定功能薄膜層的工藝,所沉積的薄膜可以是導(dǎo)體、絕緣材料或半導(dǎo)體材料。

刻蝕機(jī)通過(guò)干刻蝕(用等離子體進(jìn)行薄膜刻蝕)及濕蝕刻(液體腐蝕)的方法,根據(jù)印上去的圖案刻蝕掉有圖案(或沒(méi)有圖案)的部分,留下剩余的部分,芯片圖案又從光刻膠涂層轉(zhuǎn)移到了硅片上。

▲刻蝕原理簡(jiǎn)示

當(dāng)今的芯片使用各種原子級(jí)加工工具生產(chǎn)。

原子層沉積(ALD)技術(shù)可將材料以單原子膜形式一層一層的鍍?cè)谝r底表面,一次只能沉積一層。原子層刻蝕(ALE)技術(shù)是一種用于精密去除目標(biāo)材料層的工藝。ALD和ALE均用于邏輯和存儲(chǔ)器。

業(yè)界正在為3nm及更先進(jìn)節(jié)點(diǎn)開(kāi)發(fā)ALD和ALE的高級(jí)版本。

區(qū)域選擇性沉積是一種先進(jìn)的自對(duì)準(zhǔn)圖案化技術(shù),將新穎的化學(xué)方法與ALD或分子層沉積(MLD)工具結(jié)合在一起,涉及在精確位置沉積材料和膜的過(guò)程,可減少流程中的光刻和刻蝕步驟。

從理論上講,選擇性沉積可用于在金屬上沉積金屬,在器件上的電介質(zhì)上沉積電介質(zhì)。不過(guò)目前區(qū)域選擇性沉積仍存在一系列挑戰(zhàn),還在持續(xù)研發(fā)中。

▲ALD區(qū)域選擇性沉積Al2O3原理圖

對(duì)于在低納米節(jié)點(diǎn)上開(kāi)發(fā)的芯片,主要問(wèn)題有器件的選擇性增長(zhǎng)、去除特定材料等。

因此,可以通過(guò)某種刻蝕去除出現(xiàn)在芯片中的異常現(xiàn)象,但晶圓上殘留的任何材料都可能引起其他問(wèn)題,例如掩膜堵塞。

業(yè)界一直在將嵌段共聚物視為生產(chǎn)這些緊密圖案化表面的一種方式。嵌段共聚物將多種性質(zhì)不同的聚合物鏈段連在一起,制備成一種特殊的線型聚合物,得到性能更為優(yōu)越的功能聚合物材料。

過(guò)去,大部分商業(yè)努力都集中在無(wú)機(jī)材料上,無(wú)機(jī)材料比有機(jī)材料更致密、更薄。但隨著越來(lái)越多的有機(jī)材料進(jìn)入制造過(guò)程,僅適用于無(wú)機(jī)薄膜的ALD和ALE技術(shù)就不夠用了。

分子層沉積(MLD)、分子層刻蝕(MLE)和ALD、ALE的方法類(lèi)似,但和ALD和ALE不同的是,MLD和MLE也能用于產(chǎn)生和去除有機(jī)薄膜。

這種刻蝕技術(shù)可以選擇性去除MLD層,而不會(huì)影響到附近的ALD層,為精確控制納米級(jí)材料的幾何形狀打開(kāi)了一扇新的大門(mén)。

▲先進(jìn)制程設(shè)備布局

五、拒絕芯片瑕疵!卡住質(zhì)量防線的檢測(cè)

在芯片進(jìn)入量產(chǎn)前,還需使用各種系統(tǒng)來(lái)查找芯片中的缺陷,也就是對(duì)芯片進(jìn)行檢測(cè)。

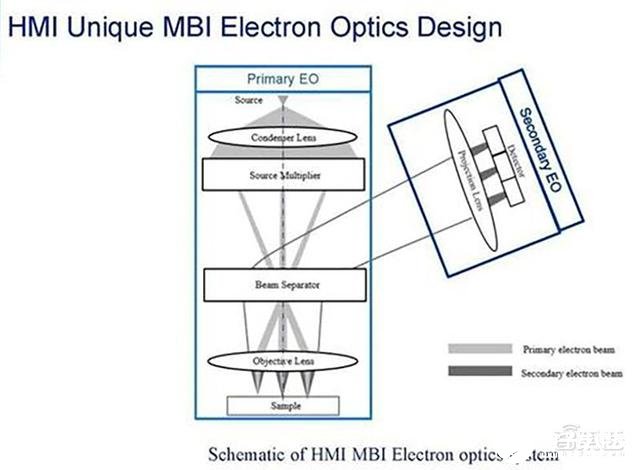

晶圓檢測(cè)分為兩類(lèi):光學(xué)和電子束。光學(xué)檢查工具速度快,但分辨率受限;電子束檢測(cè)工具分辨率更好,但速度偏慢。

因此,Applied Materials、KLA、ASML等公司均在開(kāi)發(fā)多光束電子束檢測(cè)系統(tǒng),理論上來(lái)說(shuō),它能以較高的速度發(fā)現(xiàn)最困難的缺陷。ASML即開(kāi)發(fā)了一種具有9條光束的電子束檢測(cè)工具。

▲ASML多光束晶圓檢測(cè)方法

不過(guò)芯片制造商希望使用具有更多光束的工具來(lái)加快檢測(cè)過(guò)程。這項(xiàng)技術(shù)目前尚且面臨不少挑戰(zhàn)。

芯片制造商還使用各種量測(cè)系統(tǒng)來(lái)測(cè)量芯片內(nèi)的結(jié)構(gòu)。其中微距量測(cè)掃描式電子顯微鏡(CD-SEM)進(jìn)行自上而下的量測(cè),光學(xué)CD系統(tǒng)使用偏振光來(lái)表征結(jié)構(gòu)。

十年前,許多人認(rèn)為CD-SEM和OCD會(huì)走到盡頭,因此加快了幾種新型量測(cè)技術(shù)的開(kāi)發(fā),包括稱為臨界尺寸小角X射線散射(CD-SAXS)的X射線量測(cè)技術(shù)。

CD-SAXS是一種無(wú)損量測(cè)技術(shù),使用小光束尺寸的可變角度透射散射來(lái)提供量測(cè)結(jié)果,X射線的波長(zhǎng)小于0.1nm。其優(yōu)點(diǎn)是能在于小波長(zhǎng)能提供更高的分辨率,避免了OCD所具有的許多參數(shù)相關(guān)性問(wèn)題,并且計(jì)算更加簡(jiǎn)單。

但在在某些情況下,X射線是由R&D設(shè)施中的大型同步加速器存儲(chǔ)環(huán)產(chǎn)生的,這對(duì)晶圓廠來(lái)說(shuō)很不切實(shí)際。

對(duì)于Fab工具,CD-SAXS需要緊湊的X射線源。三星,臺(tái)積電等公司在實(shí)驗(yàn)室中均有CD-SAXS工具。

基于晶圓廠的CD-SAXS的問(wèn)題在于X射線源有限且速度慢,會(huì)影響吞吐量。另外據(jù)VLSI研究公司總裁Risto Puhakka介紹,其成本也是一個(gè)問(wèn)題,“可能貴5倍或10倍”。

Puhakka認(rèn)為,短期內(nèi)芯片制造商不會(huì)將CD-SAXS插入到在線監(jiān)控流中。

CD-SAXS在內(nèi)存方面正在取得進(jìn)展。如今,在研發(fā)方面,內(nèi)存制造商正在使用該技術(shù)來(lái)表征硬掩模和高寬比結(jié)構(gòu)。在邏輯芯片方面,該技術(shù)仍處于概念階段,X射線強(qiáng)度還將面臨挑戰(zhàn)。

六、像搭樂(lè)高一樣堆疊封裝芯片

傳統(tǒng)設(shè)計(jì)方法是通過(guò)縮小每個(gè)節(jié)點(diǎn)上不同的芯片功能,并將它們封裝到一個(gè)單片芯片上。

但是對(duì)很多人來(lái)說(shuō),集成電路的擴(kuò)展變得愈發(fā)昂貴,且每個(gè)節(jié)點(diǎn)上的性能和功率優(yōu)勢(shì)都在減少,因此需要高級(jí)封裝等替代方案。

當(dāng)今高級(jí)封裝技術(shù)能讓內(nèi)存更接近邏輯處理單元,提升互聯(lián)密度和信號(hào)傳輸速率。

邏輯內(nèi)核與存儲(chǔ)單元之間的物理距離會(huì)導(dǎo)致延遲,人工智能等應(yīng)用又需要密集的計(jì)算操作,信號(hào)從大型芯片的一端傳輸?shù)搅硪欢怂ㄙM(fèi)的時(shí)間,遠(yuǎn)比使用高速接口從一個(gè)芯片傳輸?shù)搅硪恍酒ㄙM(fèi)的時(shí)間更長(zhǎng)。

因此,通過(guò)封裝邏輯核心和內(nèi)存,可以大大減低功耗并增加內(nèi)存帶寬。許多封裝廠研發(fā)先進(jìn)的封裝技術(shù),以增加晶體管速度,從而提高整個(gè)封裝系統(tǒng)的性能。

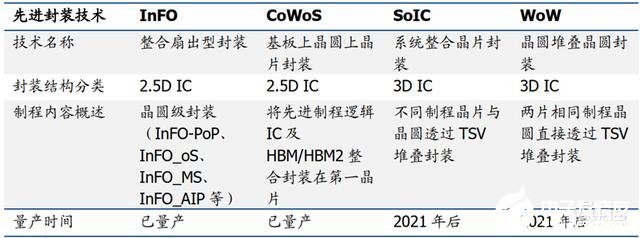

在已量產(chǎn)的2.5D集成電路領(lǐng)域,臺(tái)積電主推CoWoS工藝,英特爾主推EMIB工藝,三星主推FOPLP。

▲臺(tái)積電先進(jìn)封裝技術(shù)一覽

未來(lái)通過(guò)難度更高的硅通孔(TSV)3D封裝技術(shù),臺(tái)積電將進(jìn)一步量產(chǎn)系統(tǒng)整合SoIC、 WoW等3D集成電路,英特爾推出Foveros技術(shù),三星推出3D SiC。

小芯片(chipset)是實(shí)現(xiàn)異構(gòu)集成的一種新形式,通過(guò)在特定空間像樂(lè)高似的堆疊多種芯片,實(shí)現(xiàn)更快的開(kāi)發(fā)速度和更高的計(jì)算力。

去年臺(tái)積電展示的7nm小芯片系統(tǒng)就是一個(gè)很好的例子,通過(guò)采用COWOS封裝技術(shù)和LIPINCON互連技術(shù),將大型多核設(shè)計(jì)劃分成多個(gè)小芯片,從而提供更高的良率和更好的經(jīng)濟(jì)性。

英特爾也做到將不同IP、不同工藝的各種方案封裝在一起,從而省去漫長(zhǎng)的重新設(shè)計(jì)、測(cè)試、流片過(guò)程。

2019年7月,英特爾推出將EMIB和FOVEROS相結(jié)合的CO-EMIB技術(shù),無(wú)論是2D水平互連還是3D堆疊互連,單片與單片之間都可實(shí)現(xiàn)近乎于SoC級(jí)高度整合的低功耗、高帶寬、高性能表現(xiàn)。

▲臺(tái)積電、三星、英特爾均為堆疊封裝技術(shù)的主要參與者

研究人員也在功率半導(dǎo)體封裝方面進(jìn)行改進(jìn)。例如,碳化硅(SiC)比硅具有更高的擊穿電場(chǎng)和熱導(dǎo)率,供應(yīng)商將SiC功率MOSFET和其他組件集成到功率模塊中。

但要充分利用碳化硅,還需在封裝方面做很多優(yōu)化工作。Cree CTO John Palmour在最近的一次采訪中表示,如果僅使用用于硅的標(biāo)準(zhǔn)功率模塊設(shè)計(jì),則只能獲得碳化硅所應(yīng)具有的性能的一半左右。

結(jié)語(yǔ)

隨著半導(dǎo)體制程的不斷發(fā)展,摩爾定律的推進(jìn)節(jié)奏逐漸趨緩,延續(xù)摩爾定律的生命力需要?jiǎng)?chuàng)新技術(shù)和設(shè)備的突破。

胡正明教授曾說(shuō)過(guò),半導(dǎo)體行業(yè)大約每隔20年,就會(huì)有新的危機(jī)出現(xiàn)。20年前,大家一度非常悲觀,看不清如何才能將芯片性能做得更好、功耗更低且控制住成本。

如今半導(dǎo)體行業(yè)回到了20年周期的“危機(jī)”循環(huán)節(jié)點(diǎn),全球最頂尖的芯片公司都不知道,當(dāng)先進(jìn)制程走到5nm、3nm、2nm、1nm后,未來(lái)半導(dǎo)體行業(yè)的創(chuàng)新發(fā)展,路又在何方?

這個(gè)問(wèn)題的答案,也許藏在人工智能、5G等新興應(yīng)用里,也許藏在半導(dǎo)體的新器件、新技術(shù)、新模式里,整個(gè)半導(dǎo)體行業(yè)都在不斷探索前行。

無(wú)論未來(lái)誰(shuí)是創(chuàng)新風(fēng)暴的引領(lǐng)者,最終受益的都將是享用更高性能電子產(chǎn)品的每一個(gè)人。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

453文章

50406瀏覽量

421819 -

英特爾

+關(guān)注

關(guān)注

60文章

9886瀏覽量

171523 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27010瀏覽量

216296

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文解讀全球汽車(chē)半導(dǎo)體市場(chǎng)的未來(lái)發(fā)展

中國(guó)半導(dǎo)體的鏡鑒之路

領(lǐng)泰 / LEADTECK領(lǐng)泰半導(dǎo)體(深圳)有限公司由一級(jí)代理提供技術(shù)支持

全球半導(dǎo)體巨頭近期聚焦哪些創(chuàng)新?

恩智浦半導(dǎo)體攜手亞馬遜云科技,共創(chuàng)新紀(jì)元半導(dǎo)體創(chuàng)新之路

變革性的半導(dǎo)體IP,如何驅(qū)動(dòng)未來(lái)?

照亮半導(dǎo)體創(chuàng)新之路

半導(dǎo)體

MDD辰達(dá)半導(dǎo)體榮獲半導(dǎo)體市場(chǎng)創(chuàng)新企業(yè)獎(jiǎng)、創(chuàng)新產(chǎn)品獎(jiǎng)兩項(xiàng)大獎(jiǎng)

喜訊 | MDD辰達(dá)半導(dǎo)體榮獲藍(lán)點(diǎn)獎(jiǎng)“最具投資價(jià)值獎(jiǎng)”

深迪半導(dǎo)體榮獲“2023-2024半導(dǎo)體行業(yè)/MEMS芯片創(chuàng)新引領(lǐng)企業(yè)”獎(jiǎng)

全球半導(dǎo)體先進(jìn)制程之戰(zhàn)打響,未來(lái)半導(dǎo)體行業(yè)的創(chuàng)新之路在何方

全球半導(dǎo)體先進(jìn)制程之戰(zhàn)打響,未來(lái)半導(dǎo)體行業(yè)的創(chuàng)新之路在何方

![[<b class='flag-5'>半導(dǎo)體</b>前端工藝:第二篇] <b class='flag-5'>半導(dǎo)體制程</b>工藝概覽與氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

評(píng)論