前言

開關電源的設計在確保其它參數滿足要求的前提下,還需要將功率半導體和功率磁元件開關過程產生的EMI噪聲降低到標準限制以下。按照產品設計流程,通常在確定了拓撲方案后,從理論上既可以得到理想情況下的開關傳導噪聲特性,而實際產品測試中需要考慮到開關環路雜散參數和實際器件中的雜散參數帶來的影響。其中既有雜散參數的引入造成系統傳遞函數變化的影響,又有磁元件等高di/dt、dv/dt器件或線路在工作中的電磁場耦合的影響。這些影響在設計前期很難簡單的預估,但卻嚴重影響開關電源的傳導特性。

本文通過使用ANSYS等工具,提取開關電源中的雜散參數,通過模擬電源工作環境獲得接近實際工作時的傳導特性。

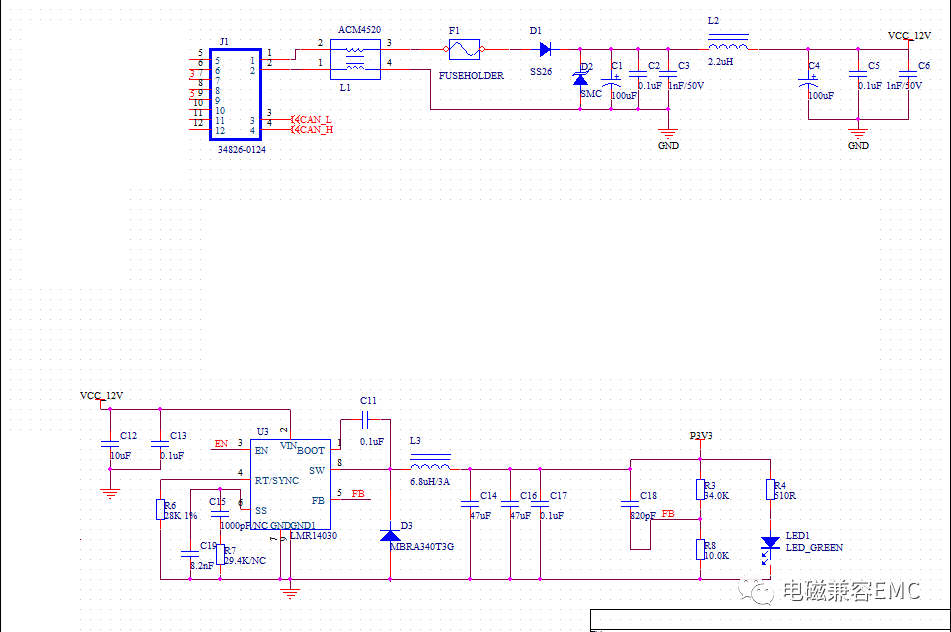

為了方便,這里使用了某產品的PCB設計,其主電源采用DC12V輸入,3.3V/2A輸出,芯片方案采用TI公司的LMR14030。該方案為非隔離BUCK方案,常見于汽車電子等小功率電子設備中。

電源拓撲設計

1.1、基本參數

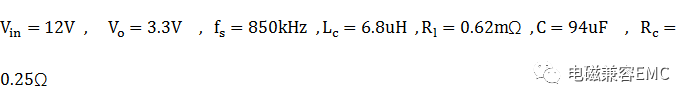

已知

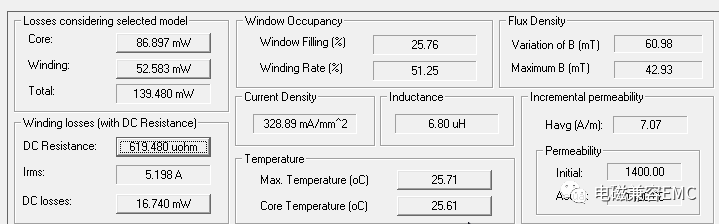

其中 為開關頻率,根據LMR14030規格書中給出的

為開關頻率,根據LMR14030規格書中給出的 阻值和?

阻值和? ?的關系式得出。

?的關系式得出。

(1)

為輸出電感

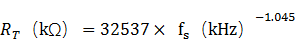

為輸出電感 的直流電阻,其值由PExprt計算得到。

的直流電阻,其值由PExprt計算得到。 為輸出電容引腳電阻,根據SIwave中電容庫參數得到。

為輸出電容引腳電阻,根據SIwave中電容庫參數得到。

圖1、PExprt中輸出電感參數

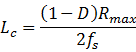

根據張占松的《開關電源原理與設計》中的公式

代入數據可得 ?。由規格書中可知電源芯片的最大供電能力為3.5A,因此電源多數情況下工作在CCM模式下。要求輸出電壓紋波

?。由規格書中可知電源芯片的最大供電能力為3.5A,因此電源多數情況下工作在CCM模式下。要求輸出電壓紋波 ,根據下式

,根據下式

可得電容大小為 ?實際取值為2顆47uF電容并聯。

?實際取值為2顆47uF電容并聯。

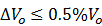

1.2、BUCK的開環仿真

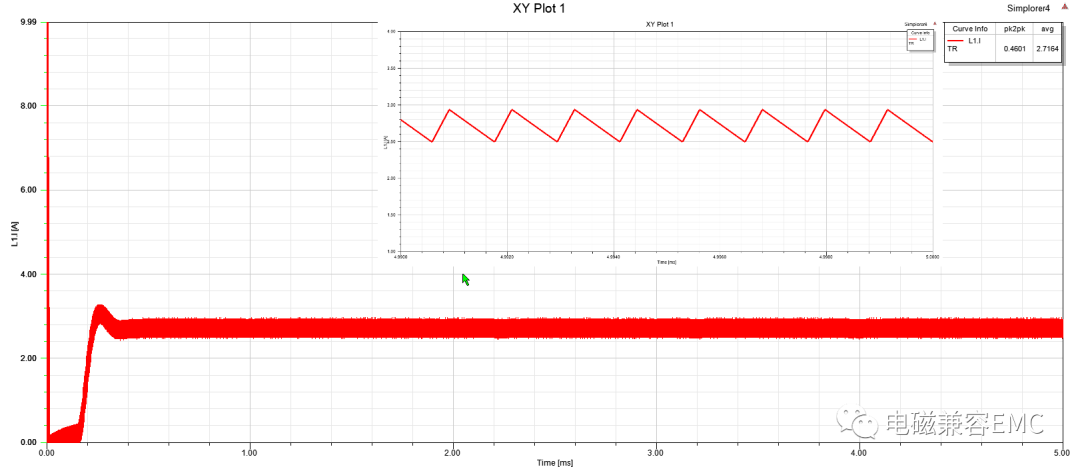

利用simplorer搭建如下電路,將上面參數定義到對應器件中。其中開關頻率為850khz,占空比為0.275。最終得到的電感電流和輸出電壓波形如下圖所示。

圖2、BUCK開環仿真拓撲

圖3、負載電阻電壓

圖4、輸出電感電流

由電感電流結果可知,電路確實工作在CCM模式。負載電阻紋波電壓為0.096V,電壓平均值為2.72V,紋波電壓超出設計要求。原因主要為輸出電容選擇了一個ESR較大的物料,當調整為0.02Ω后,電壓紋波降低到0.4%,符合要求。開始選擇的47uF電容為1206封裝,觀察物料庫中該封裝尺寸的ESR,對比同樣容值2816封裝尺寸電容,可以發現小封裝尺寸電容具有更大的ESR值。

圖5、不同封裝電容的寄生電阻對比

1.3、閉環仿真

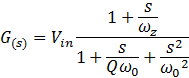

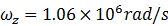

理想情況下Buck電路的傳遞函數為

其中, ,

, ,

, ,代入數據可得它們的值如下:

,代入數據可得它們的值如下:

,

, ,

, ?.

?.

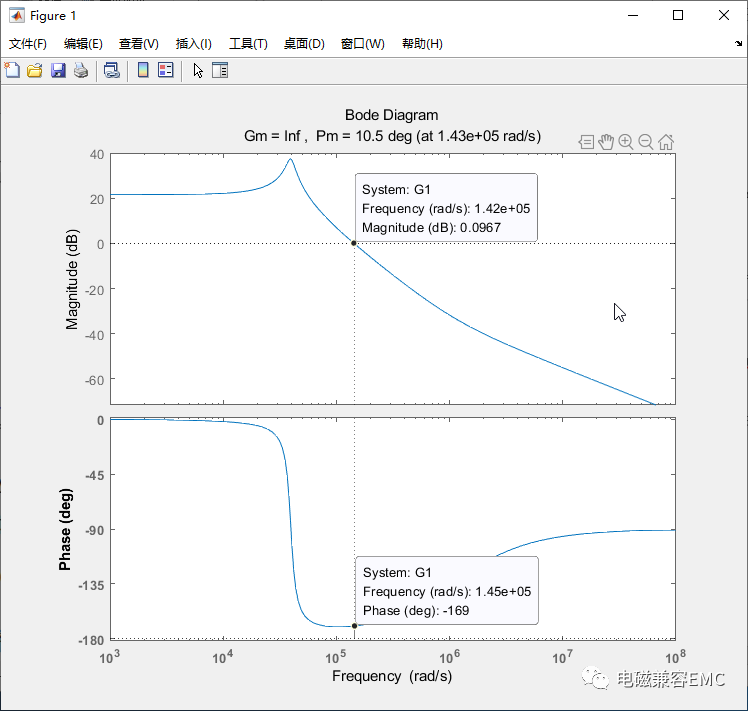

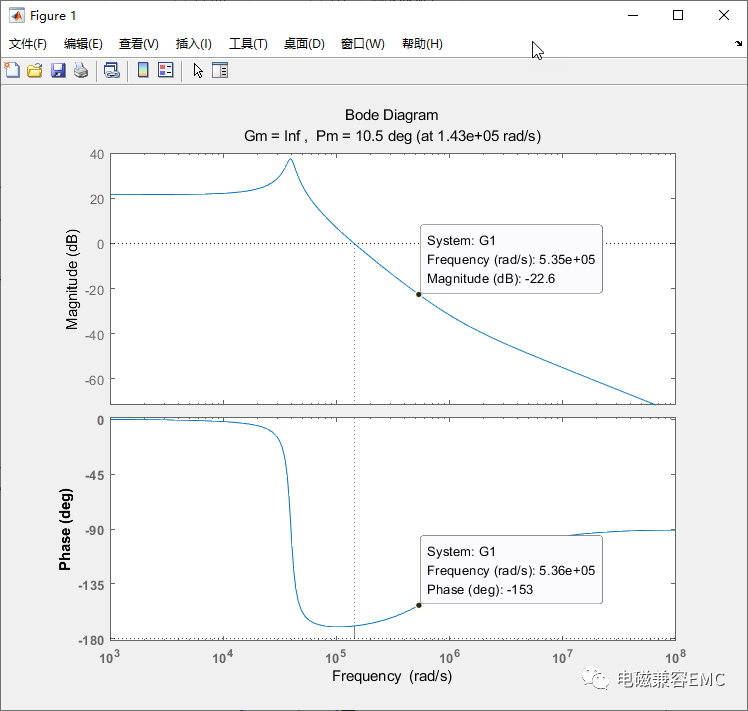

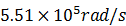

采用MATLAB計算得到所設計的開環Buck幅頻相頻特性曲線如下

圖6 開環Buck幅頻相頻特性曲線

由上圖可知,穿越頻率為 ,開環Buck的相位裕度為10.5°,小于45°,需要進行相位補償。增益裕度不需要補償。

,開環Buck的相位裕度為10.5°,小于45°,需要進行相位補償。增益裕度不需要補償。

常用的補償方式有比例補償,PI補償,PD補償,PID補償等等。我們只要選取一種補償方式使其相位裕度大于等于45°,幅值裕度大于7dB就可以了。

我們選取補償后的穿越頻率 ?,對應的角頻率為

?,對應的角頻率為 ,利用MATLAB的點捕捉功能,在圖上捕捉出角頻率為

,利用MATLAB的點捕捉功能,在圖上捕捉出角頻率為 的點,如下圖所示。

的點,如下圖所示。

圖7、 85kHz幅頻相頻點捕捉圖

由上圖可知,在頻率為 85kHZ 處的相角為-161°。如果單單采用比例補償,是不行的。因為采用比例補償將開環 buck 的穿越頻率由 增加到

增加到 ?后,此時的相位裕度為 180°-153°=27°<45°,顯然不行。頻率為 85kHZ 處的相角為-161°,要是 buck 穩定,在此處的相角最小應該為-135°(此時對應的相位裕度剛好為45°),只有這樣,最終的相位裕度才能大于等于 45°。所以,應該找一個相頻曲線有大于 0 的部分補償網絡對該 buck 進行補償(這里采用 PI 補償是不行的,有興趣的可以自己嘗試)。根據各類補償網絡的相頻曲線可知,有 PD、PID 補償網絡的相頻曲線存在大于 0 的部分。在這里,為了增大靜態增益,我們選取 PID補償網絡對系統進行補償(有

?后,此時的相位裕度為 180°-153°=27°<45°,顯然不行。頻率為 85kHZ 處的相角為-161°,要是 buck 穩定,在此處的相角最小應該為-135°(此時對應的相位裕度剛好為45°),只有這樣,最終的相位裕度才能大于等于 45°。所以,應該找一個相頻曲線有大于 0 的部分補償網絡對該 buck 進行補償(這里采用 PI 補償是不行的,有興趣的可以自己嘗試)。根據各類補償網絡的相頻曲線可知,有 PD、PID 補償網絡的相頻曲線存在大于 0 的部分。在這里,為了增大靜態增益,我們選取 PID補償網絡對系統進行補償(有 部分)。

部分)。

1.4、PID補償網絡的參數設計

采用 PID 補償網絡對我們的開環 buck 進行補償,按照以下步驟就可以確定 PID補償網絡的各個參數。

首先將穿越頻率調整到 ??處,具體計算方法如下:

??處,具體計算方法如下:

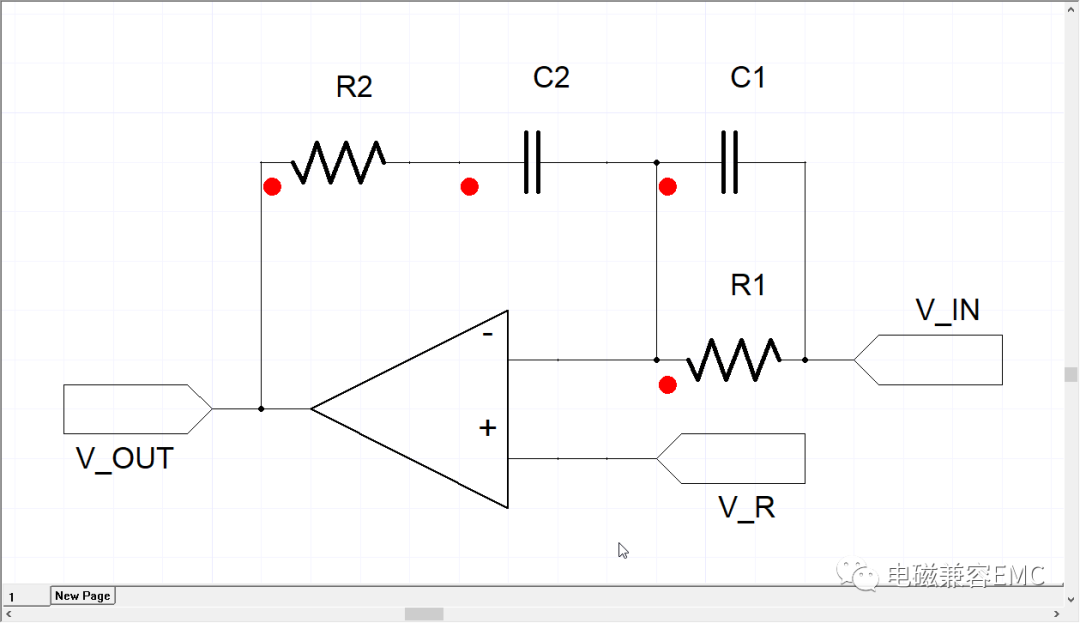

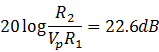

還是使用點捕捉功能,在 matlab 畫出的幅頻相頻曲線上捕捉角頻率為 的幅值,如圖 7 所示,可得此時幅值為-22.6dB,所以補償網絡的應該在開環的幅頻曲線基礎上加上22.6dB?(向上平移22.6個單位),使穿越頻率額由

的幅值,如圖 7 所示,可得此時幅值為-22.6dB,所以補償網絡的應該在開環的幅頻曲線基礎上加上22.6dB?(向上平移22.6個單位),使穿越頻率額由 變成到

變成到 。平移多少個單位,也可以通過計算得來。計算很簡單,如下:

。平移多少個單位,也可以通過計算得來。計算很簡單,如下:

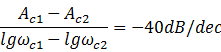

所以 85kHz 對應的點也在斜率為-40dB的直線上,因此在相頻曲線上取角頻率為 和

和 的兩個點(設這兩個點的幅值分別為

的兩個點(設這兩個點的幅值分別為 和

和 (單位dB)),利用直線斜率的定義可得:

(單位dB)),利用直線斜率的定義可得:

顯然有 (穿越頻率過橫軸),所以可得

(穿越頻率過橫軸),所以可得

(和-22.6差不多)

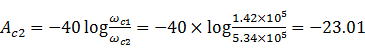

補償網絡的電路圖如下:

圖8、PID補償網絡電路圖

原理圖中給出的采樣網絡電阻值分別為 和

和 。取

。取 (

( 是三角波峰值,閉環網絡傳遞函數里最終會因為三角波的比較環節引入一個

是三角波峰值,閉環網絡傳遞函數里最終會因為三角波的比較環節引入一個 的比例因子,也相當于一個比例環節,所以這里需要將它帶上),則有:

的比例因子,也相當于一個比例環節,所以這里需要將它帶上),則有:

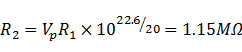

所以

。將PID網絡的比例系數P乘到開環Buck傳遞函數里得到的傳遞函數如下:

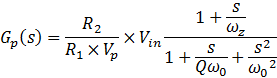

在MATLAB 中計算上述傳遞函數,可以得到 的幅頻相頻曲線如下圖所示:

的幅頻相頻曲線如下圖所示:

圖9、傳遞函數Gp的幅頻相頻曲線

由上圖可知,傳遞函數 穿越角頻率為

穿越角頻率為 ,很接近85kHz,所以R2選擇基本合理。此時相裕角度也增加到了28°,幾乎與153°互補,說明計算正確。

,很接近85kHz,所以R2選擇基本合理。此時相裕角度也增加到了28°,幾乎與153°互補,說明計算正確。

2)提高靜態增益

為了能夠使用 PID 補償網絡提供開環 buck 的靜態增益,又不影響到它的幅值裕

度(為什么會影響到幅值裕度請觀察 PID 補償網絡的相頻曲線)。

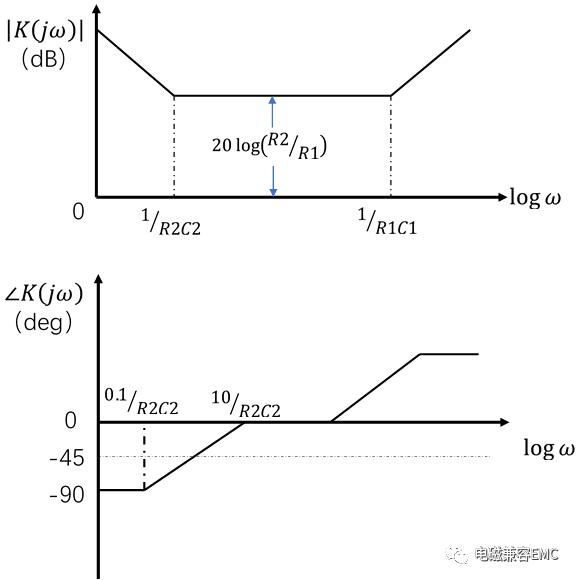

圖10、PID網絡的相頻曲線

因為 PID 補償的相頻曲線有個從-90°增加到 0°的過程,而開環 buck 的相頻曲初始有個從 0°向 180°減小的過程,如果把這個這兩個過程疊加起來,可能為產生一個-180°的相角。這個-180°相角對應的頻率所對應的幅值就是系統的幅值裕度的相反數。而在這兩個過程中,PID 補償網絡的幅值一直為正,開環 buck的幅值也一直為正。這樣一來,疊加后的幅值必然大于 0,從而幅值裕度必然小于 0,顯然是不行的。因此,為了避免產生這種情況,我們應該選取合適的C2。根據 PID 補償網絡和 Gp 的相頻曲線可知,如果我們使得下式成立,那么一定不會出現上文所說的那種情況。

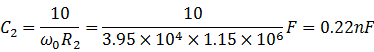

所以可得

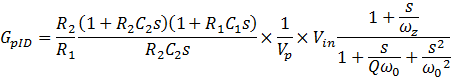

現在可將PID補償網絡的PI部分加入開環Buck的傳遞函數中,得到新的傳遞函數如下:

根據這個傳遞函數的幅頻相頻曲線可以判斷我們選取的 ,

, ?是否合理。

?是否合理。

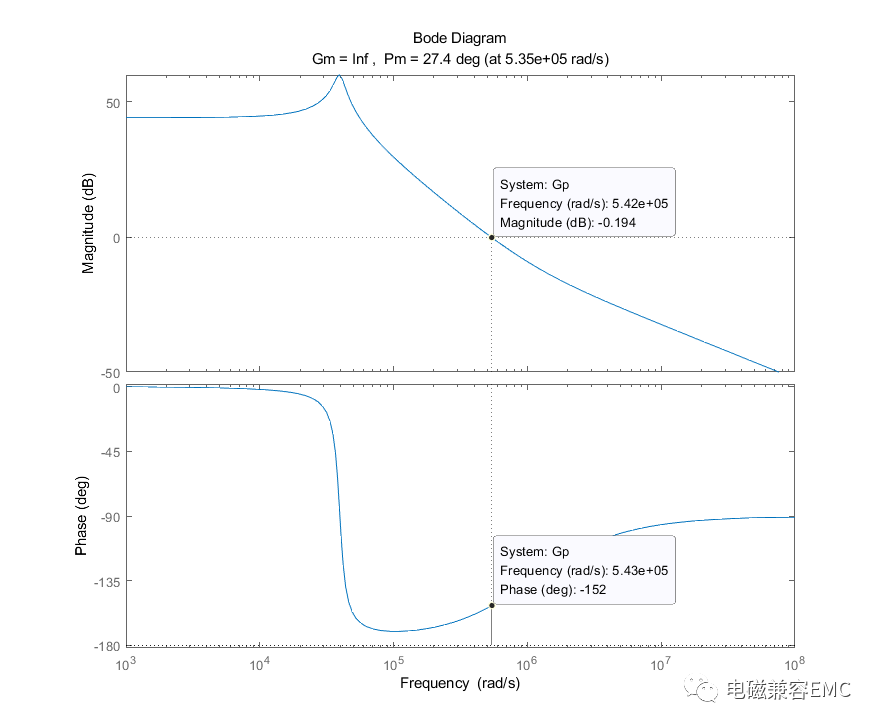

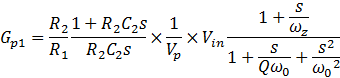

在MATLAB 中重新運行計算可得到傳遞函數 的幅頻相頻特性曲線如下圖所示:

的幅頻相頻特性曲線如下圖所示:

圖11、傳遞函數Gp1的幅頻相頻特性曲線

由上圖可知, 的穿越角頻率為

的穿越角頻率為 ,與

,與 的穿越角頻率一致,接近85kHz。相位裕度為27°,相對于

的穿越角頻率一致,接近85kHz。相位裕度為27°,相對于 的28°幾乎不變。這里沒有出現我們上文說的幅值裕度為負的那種情況,說明我們選擇C2的值基本合理。接下來,我們需要做的就是增大相位裕度,使其大于等于45°。

的28°幾乎不變。這里沒有出現我們上文說的幅值裕度為負的那種情況,說明我們選擇C2的值基本合理。接下來,我們需要做的就是增大相位裕度,使其大于等于45°。

3)提高相位裕度

觀察PID補償網絡的相頻特性曲線可知,如果要提高開環Buck的相位裕度,應該PID補償網絡的相頻曲線上相角大于(45°-27°)=18°的部分加到 上,也就是有

上,也就是有 。如果我們先取

。如果我們先取 試試看,此時可確定

試試看,此時可確定 的值如下:

的值如下:

經過PID補償后,閉環網絡的傳遞函數 ?如下:

?如下:

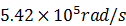

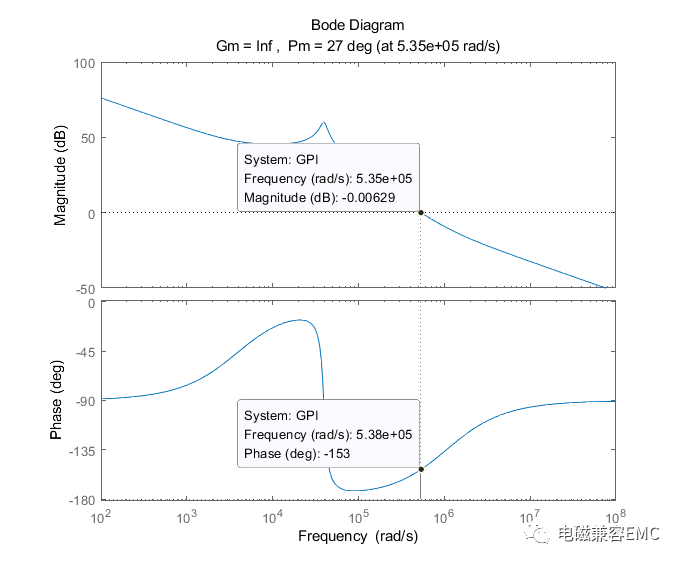

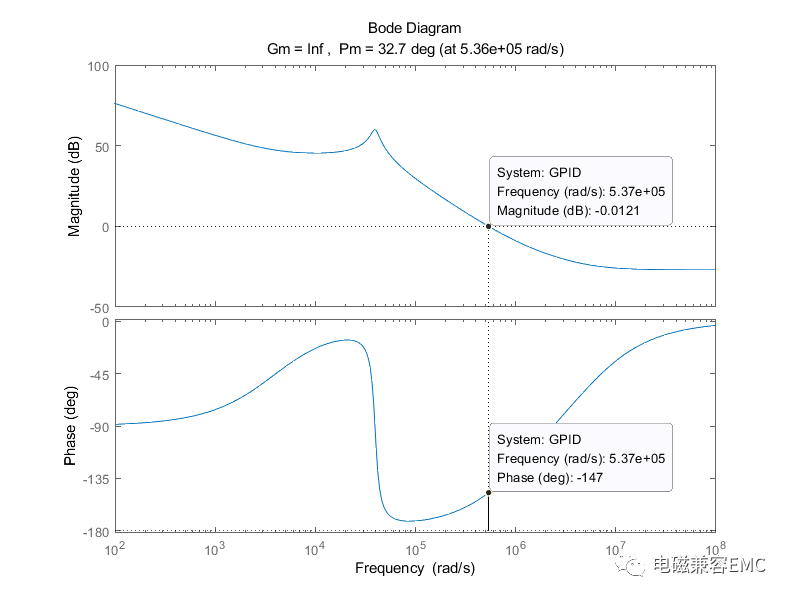

通過MATLAB 可得 的幅頻相頻曲線如下圖所示:

的幅頻相頻曲線如下圖所示:

圖12、GpID的幅頻相頻曲線

的穿越角頻率為

的穿越角頻率為 ,接近85kHz,但是相位裕度為33°偏小。我們在此技術上增大C1,相位裕度也會增加,經過一番嘗試后最終取得C1=18pF,此時閉環Buck的幅頻相頻曲線如下:

,接近85kHz,但是相位裕度為33°偏小。我們在此技術上增大C1,相位裕度也會增加,經過一番嘗試后最終取得C1=18pF,此時閉環Buck的幅頻相頻曲線如下:

圖13、最終幅頻相頻曲線

由上圖可知,閉環Buck的穿越角頻率為 ,相位裕度為46.3°,幅值裕度為無窮大,滿足要求。至此PID補償網絡的參數全部計算完畢,下面開始進行閉環Buck的仿真。

,相位裕度為46.3°,幅值裕度為無窮大,滿足要求。至此PID補償網絡的參數全部計算完畢,下面開始進行閉環Buck的仿真。

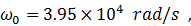

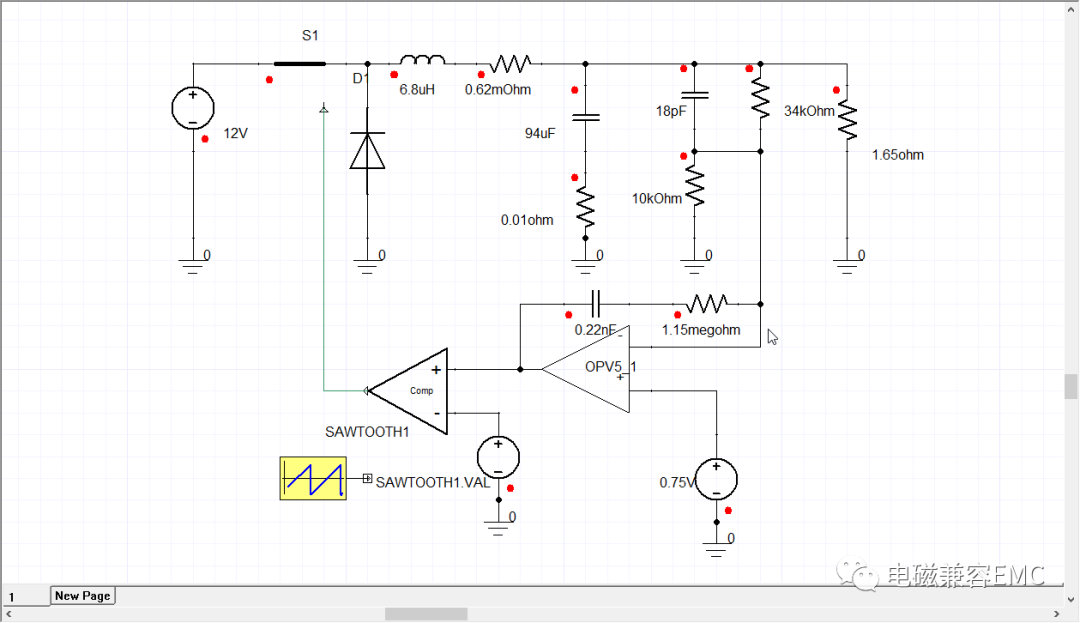

1.5、Buck閉環仿真

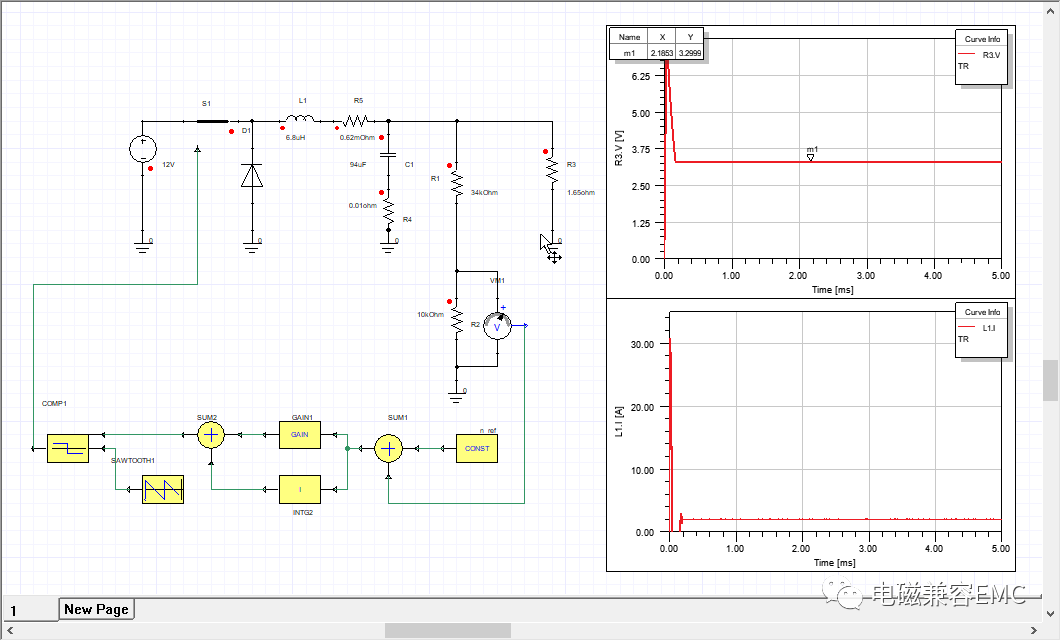

閉環仿真電路如下圖所示:

圖14、閉環仿真電路拓撲

這里需要注意放大器中傳輸頻率(放大器帶寬)參數的設置,由于放大器具有頻率響應特性,如果其傳輸頻率接近采樣電阻輸入電壓的波動頻率,就會出現信號失真的情況,這里我們先不考慮由于實際放大器在工作中出現的信號失真問題,所以將其傳輸頻率設置為200MHz,即遠大于電路開關頻率850kHz。

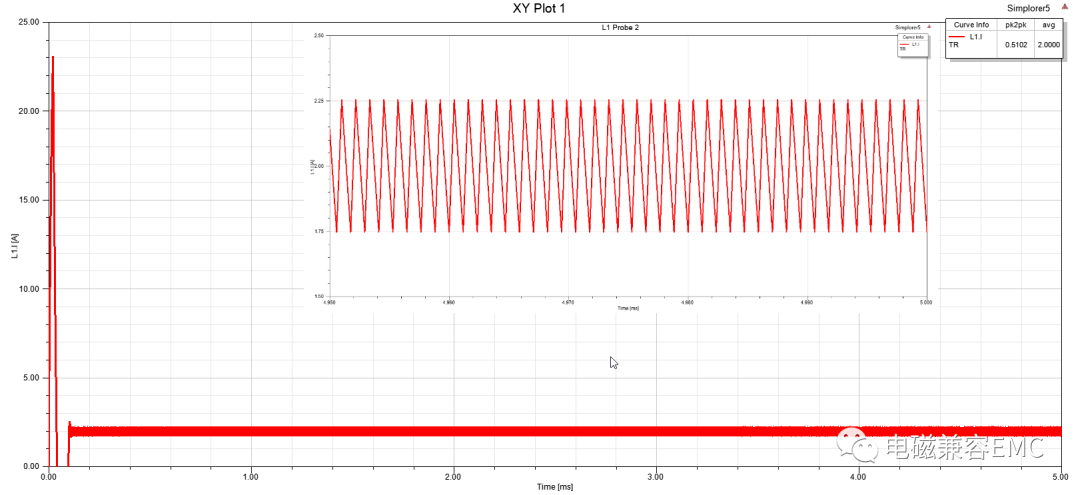

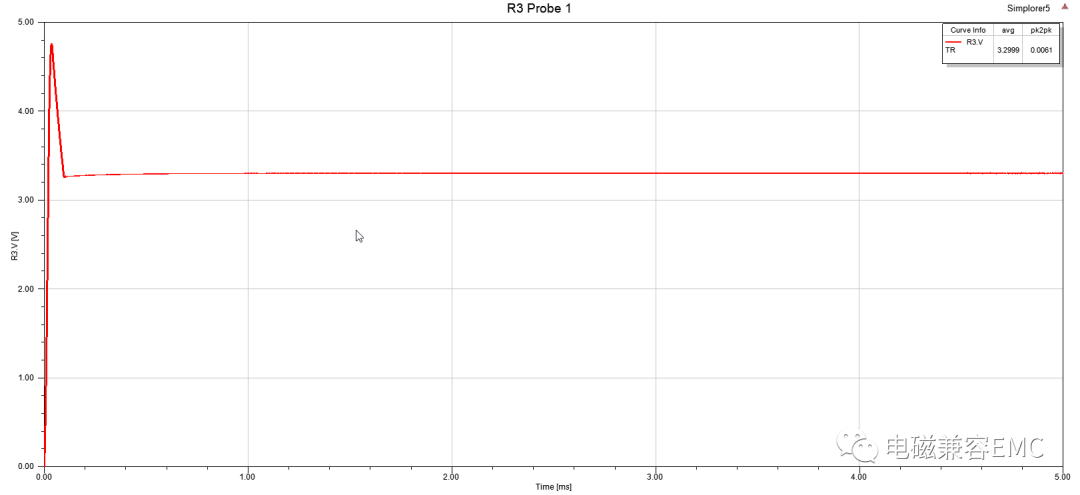

仿真結束后的電感電流波形如下圖所示,電流峰峰值的0.5倍小于電感平均電流值,buck工作在CCM模式。下圖中的三角波為將電流波形進行局部放大的部分。

圖15、電感電流波形

圖16、負載電阻電壓波形

輸出電壓 ,紋波電壓

,紋波電壓 ?,紋波電壓

?,紋波電壓

,滿足設計要求。

前面仿真采用了具有實際物理參數的模型,所以其環路響應過程存在特定的幅頻相頻響應特性,如果以純粹的數學模型替代,是不需要對環路部分進行補償的。如下面就采用數學模塊替代放大器、電容電阻和比較器,其具有簡單且計算結果理想的特點。方便最終進行驗證。下圖a中的模塊搭建最為簡單方便,圖b中需要對PID模塊中的P、I、和D參數進行合理的設置,才可得到正確的結果。

(a)

(b)

圖17、采用數學模塊作為環路控制

2、PCB及磁元件寄生參數的提取

2.1、PCB的寄生參數提取

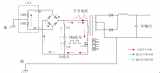

下圖為本次需要仿真的電源原理圖和PCB部分,該電源采用TI公司的LMR14030芯片方案。其開關特性已經由第一章中結合芯片參數與環路補償計算獲得,其計算結果應該接近電源實際工作的狀態。由于無法獲得該芯片的spice模型,所以采取第一章中的控制模型,下圖U3電源芯片中的EN、RT/SYNC、SS和BOOT管腳在實際工作中對EMI傳導噪聲的影響并不大,所以沒必要對這些管腳內部的電路進行建模。

圖18、主電源部分原理圖

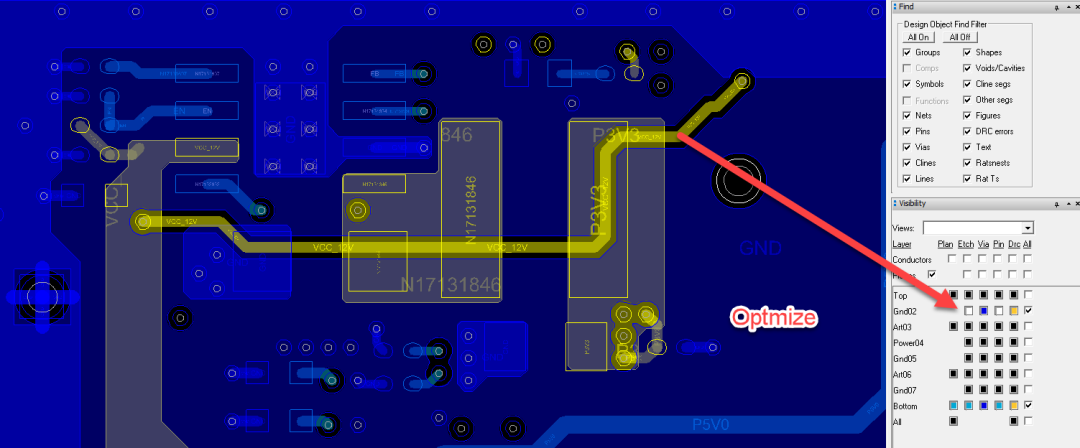

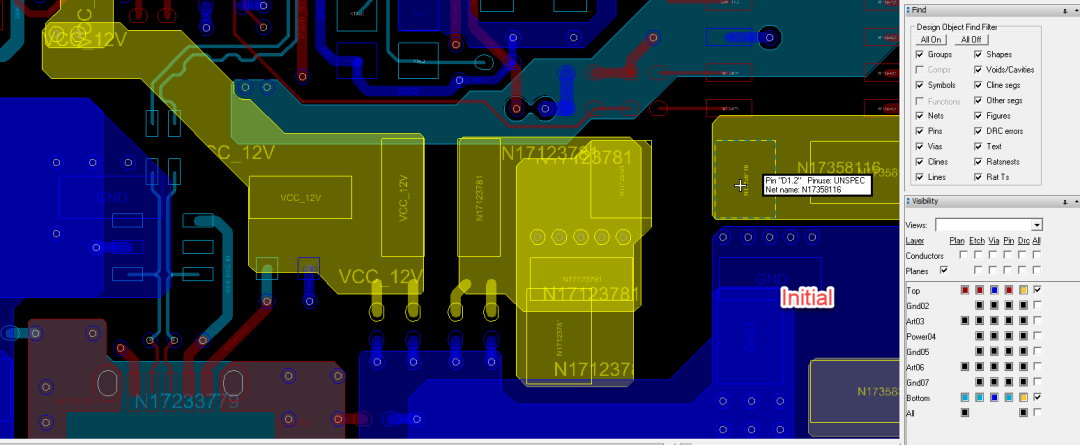

圖19、主電源(黃色部分)PCB布局

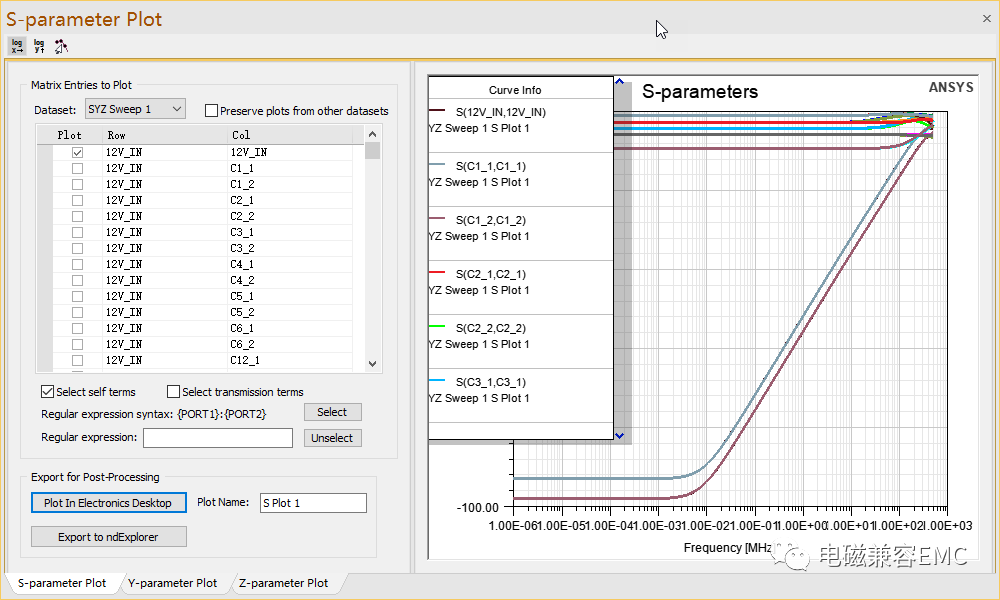

將PCB文件導入SIwave軟件中,將目標電源部分網絡中的各器件設置為端口,抽取寬頻S參數。

圖20、PCB文件的S參數

2.2、磁元件模型建立

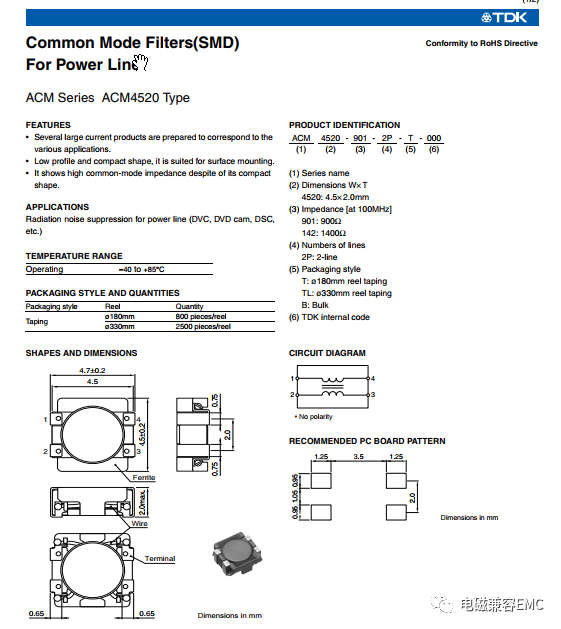

由圖18原理圖部分可以知道,12V電源部分包含3個電感原件,分別為L1、L2、L3,其中L1為TDK公司的ACM450型號共模電感,其參數如下,粗略計算得到該共模電感的感值為1.4uH。L2和L3為未知廠家的差模電感。

圖21、L1共模電感參數

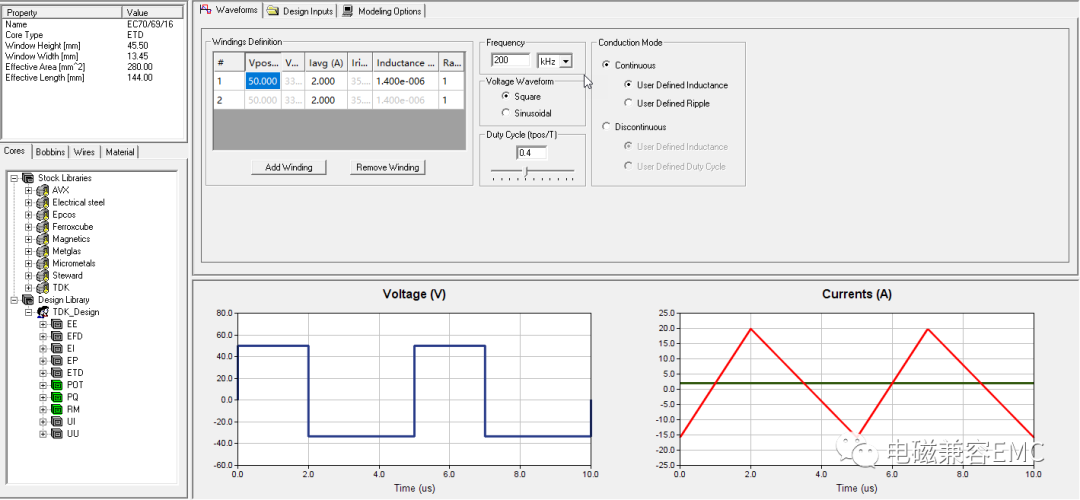

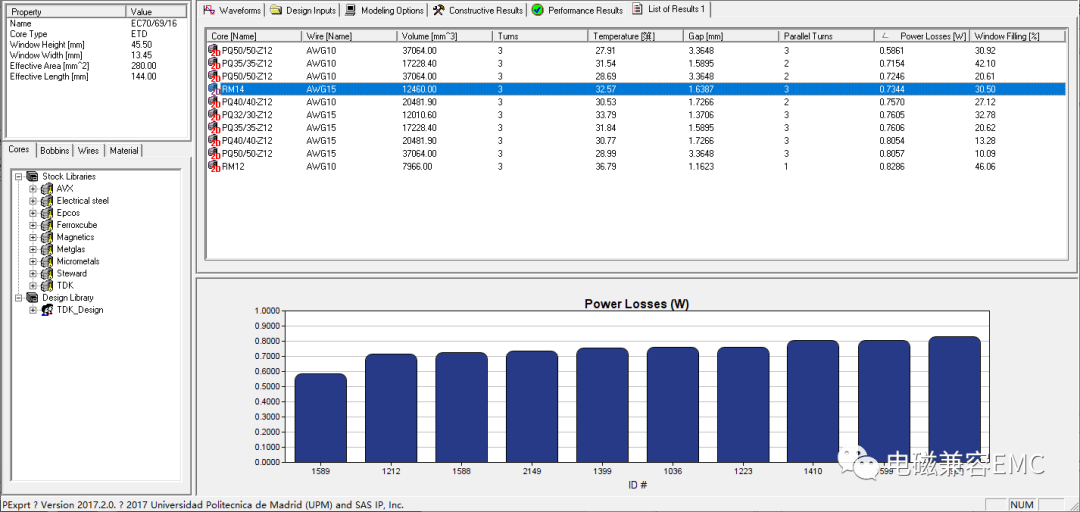

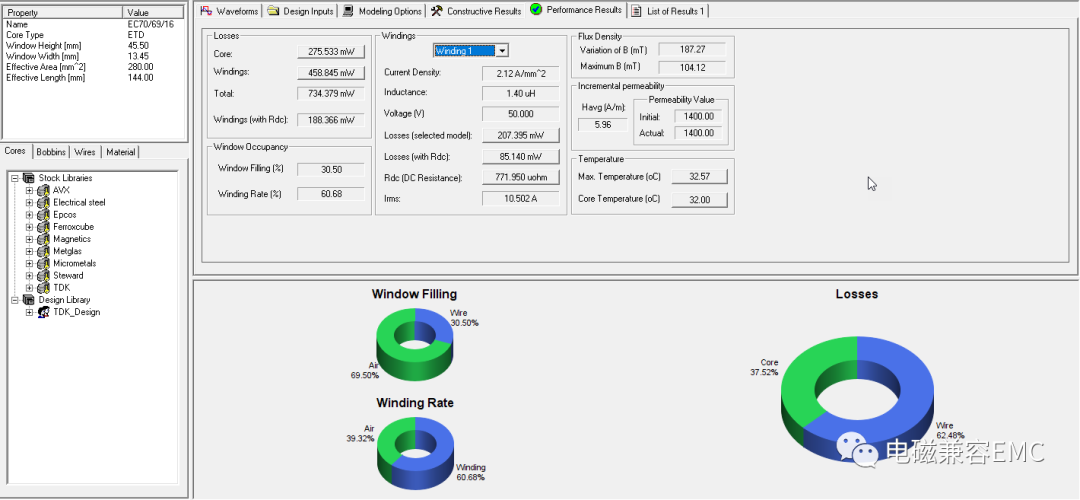

新建PExprt文件,選擇共模電感,輸入電感的電壓電流和感值,然后選擇TDK公司的磁芯。由軟件給出自動設計得到的結果。我們選擇RM14磁芯作為本次電感模型的磁芯。計算得到的電感參數如下圖所示。

圖22、共模電感L1的設計參數

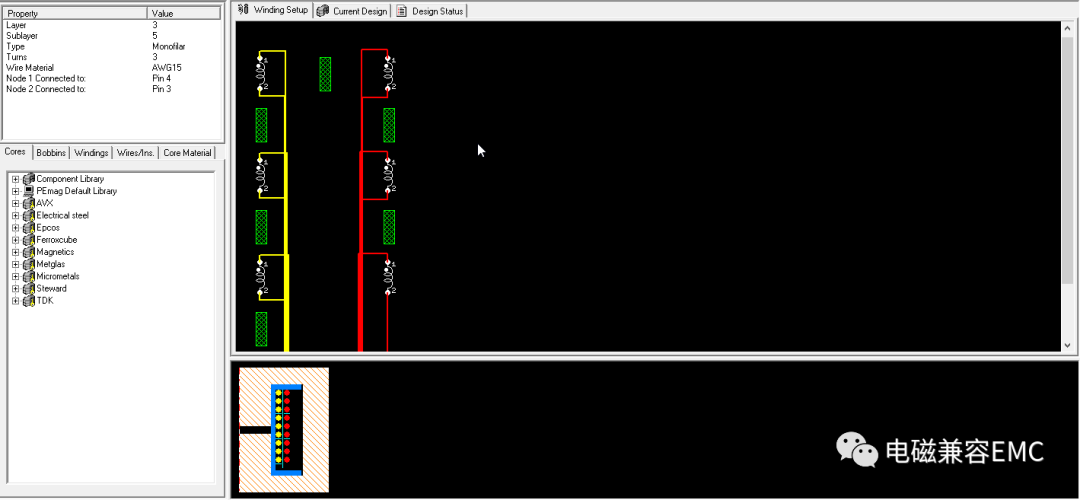

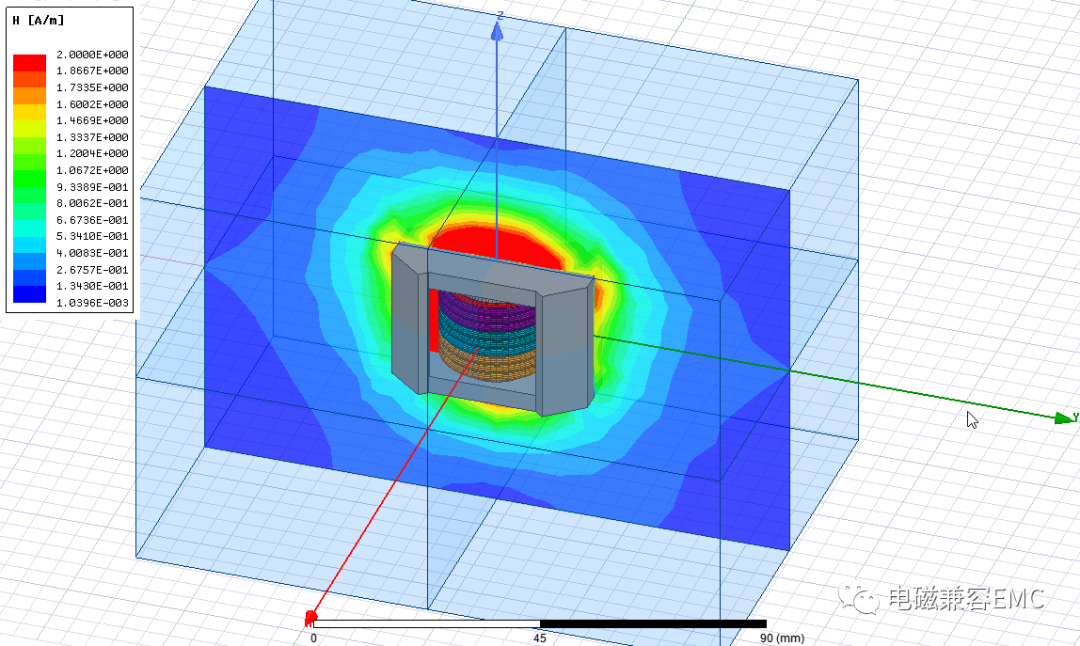

設計完畢后,將選擇的方案導入到PEmag中,由PEmag自動生成電感的Maxwell模型,并完成求解過程。求解完成后,將其導出為SML模型,以方便simplorer調用。

圖23、共模電感L1的繞組結構以及Maxwell磁場分布

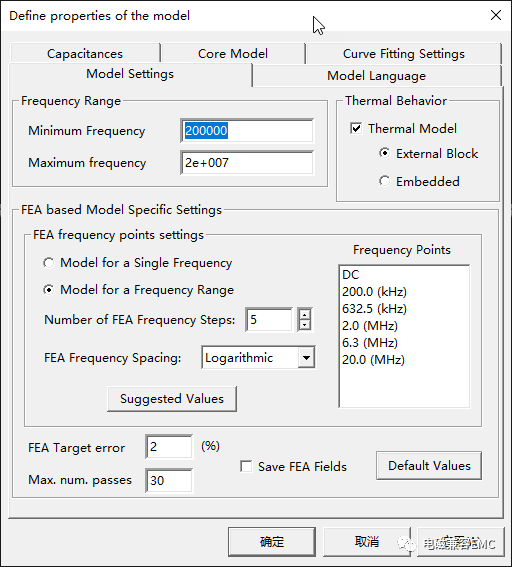

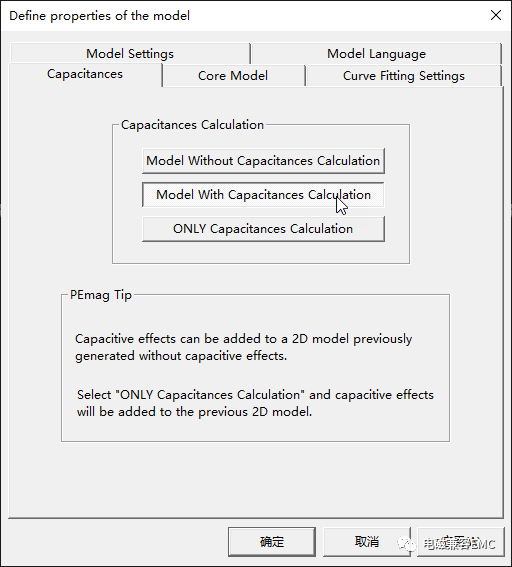

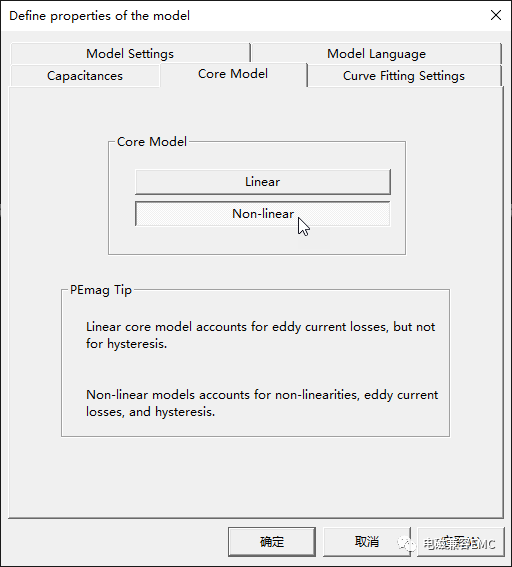

由于磁芯材料具有非線性,實際電感需要考慮匝間電容效應,所以求解過程中這些因素都要考慮進去,按照下圖參數設置。

圖24、求解設置

與L1的設計過程一樣,L2選擇TDK公司PC50材質、RM12形狀的磁芯,L3選擇Epcos公司PC50材質,PM70形狀的磁芯。

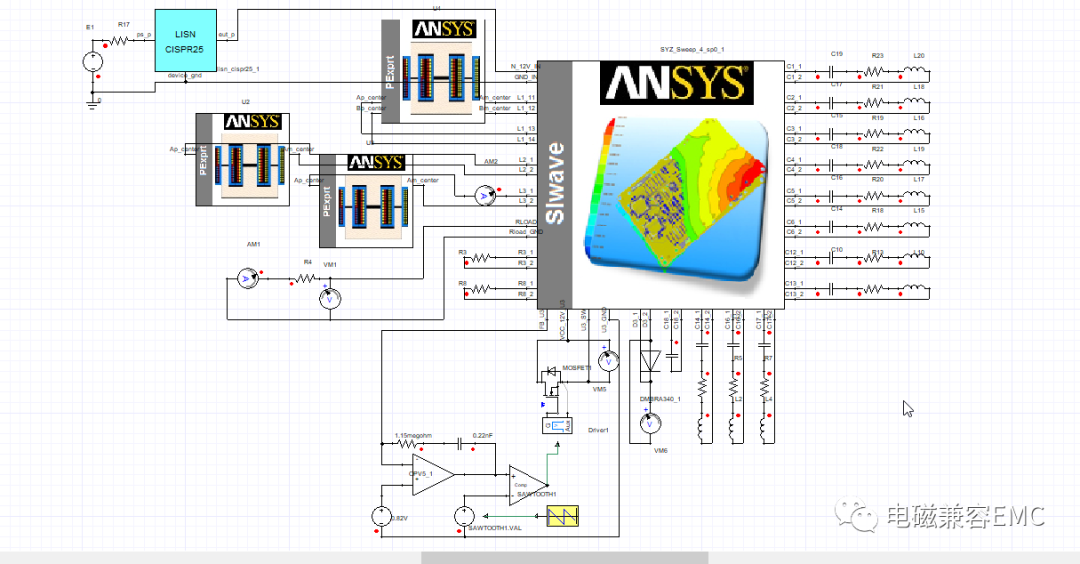

2.3、傳導仿真系統電路搭建

SIwave求解PCB文件后,獲得了電源走線部分的寬頻S參數。由PExprt設計電感原件,然后由Maxwell對電感模型進行三維求解。同時也根據第一章部分得到該電源的環路控制部分參數。至此,系統仿真電路所需的參數已經全部獲得,打開simplorer,將SIwave模型以SML模型形式導入,然后導入電感原件的SML模型,并將PID控制環路添加進來。最終得到下圖電路。

圖25、系統仿真電路

上圖仿真電路中的電容采用含有寄生參數的集總電路表示,以描述其在寬頻范圍內的非線性特征。其特征值采用SIwave電容庫中各大電容廠家給出的電容參數,具體如下表所示。

表1、系統仿真電路中的電容參數

| 電容代號 | C1、C4 | C14、C16 | C12 | C2、C5、C13、C17 | C3、C6 |

| 容值 | 100uF | 47uF | 10uF | 0.1uF | 1nF |

| ESR | 90mΩ | 20mΩ | 300mΩ | 0.06Ω | 240mΩ |

| ESL | 0.28nH | 0.49nH | 0.56nH | 0.82nH | 0.298nH |

| 封裝 | 08X10 | 1206 | 0603 | 0402 | 0402 |

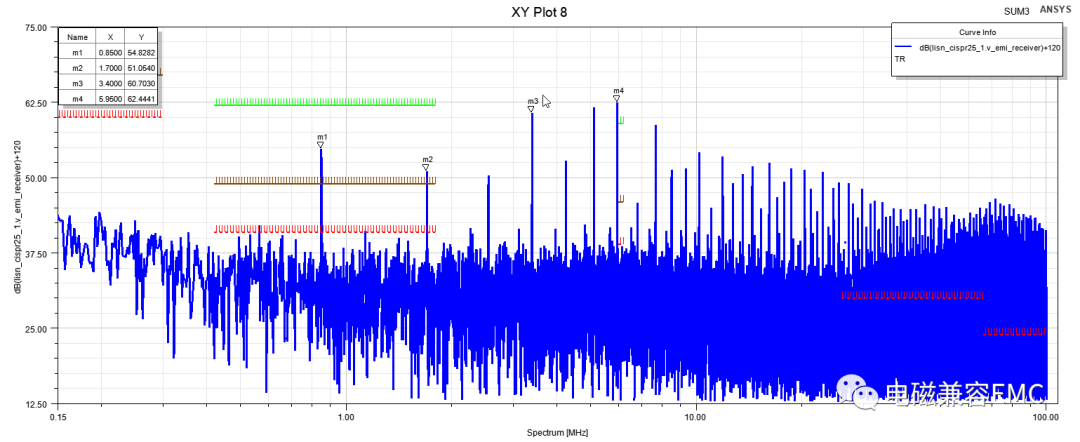

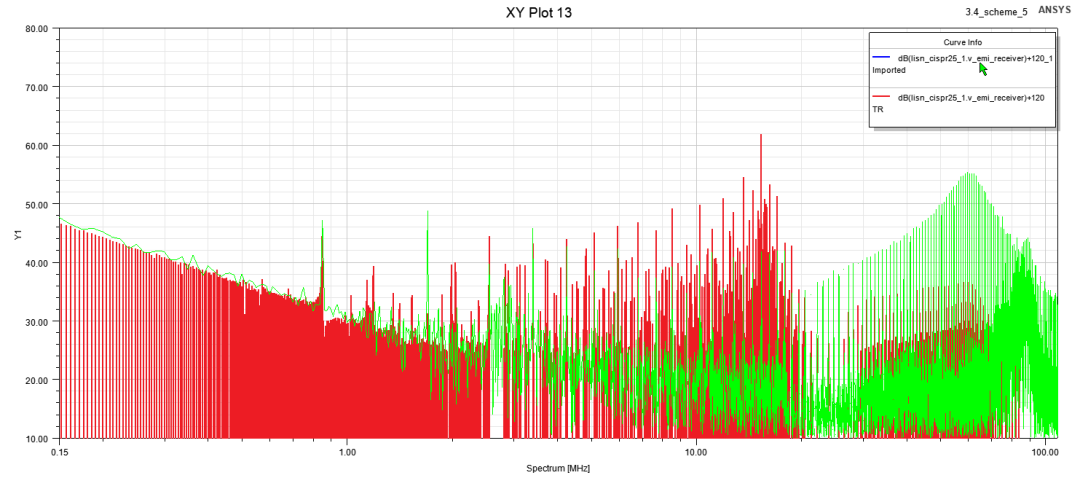

仿真完成后,將LISN上檢測到的傳導噪聲經過傅里葉變換得到頻域結果,如下圖所示,可以看到,開關頻率的基頻和二次諧波超標,6MHz左右幾乎剛剛躲過限制線,高頻超標。

圖26、傳導仿真結果

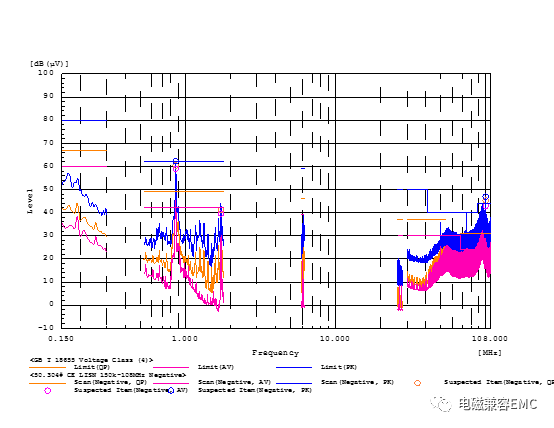

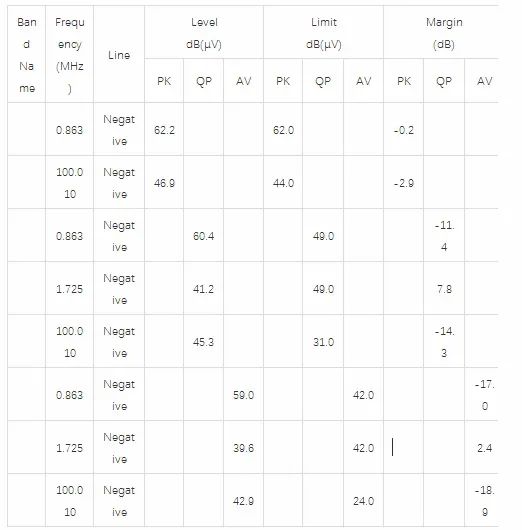

下圖為測試結果,由于沒有采用連續頻譜測試,丟失了很多信息,從現有的數據來開,基頻實測PK值62.2dBuV,仿真結果中該頻率為54.8dBuV,1.7MHz位置仿真結果為51dBuV,實測結果PK值約為45dBuV。

圖27、傳導測試結果

3、結果分析及優化

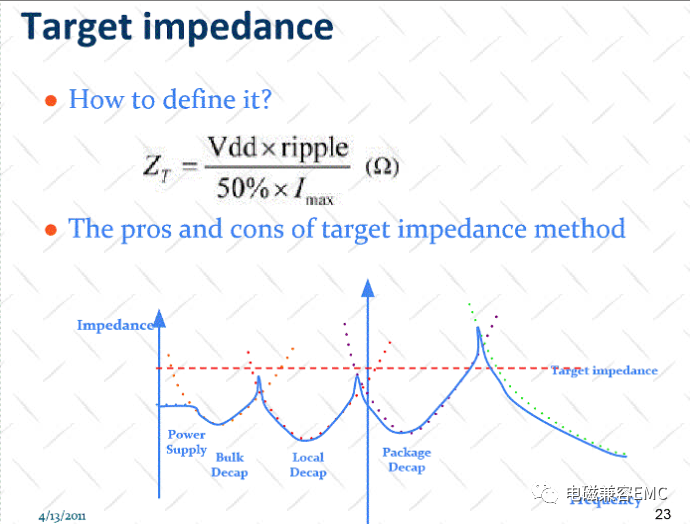

產品前期設計中,工程師是無法憑借個人經驗直接對電源傳導噪聲進行有效的優化的。而優化無非是優化開關電源拓撲,PCB布局布線,和接口濾波電路這三種方式,從操作性和難易程度來講,三種方式依次降低。第一種方式可實現性最低,因為EMC工程師在電源拓撲選擇上是沒有多少話語權的。第二種方式需要根據傳導噪聲在PCB上的分布,對PCB走線布局進行重新設計的,而優化PCB走線及布局是需要結構和layout工程師配合進行的。EMC工程師最具話語權的方式僅剩濾波電路了,這里就嘗試采用PI中目標阻抗優化的方式,快速調整輸入端電源網絡的阻抗特性,增加高頻隔離度。

注:這里僅提供電容部分優化思路,電感部分的邏輯是一致的,對于電容無法照顧到的頻段,可以采用電感進行補充,其過程無非是調整電感參數將整個阻抗曲線控制在更低水平。

根據oldfriend電源完整性優化設計文章中對目標阻抗的設計,文章中給出的建議是0.5*Imax(以1/2最大電流值作為目標值)。

圖28、目標阻抗的設定

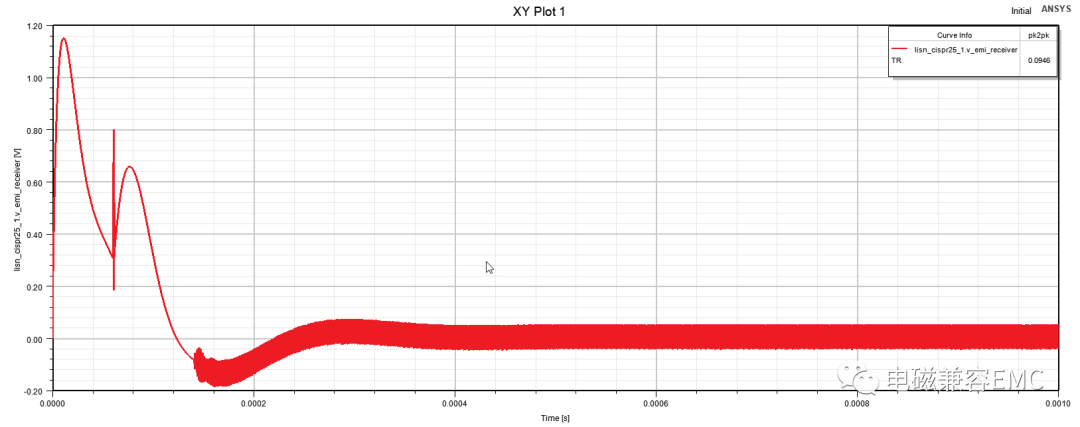

由于最終是以LISN端接收到的紋波大小來評估EMI特性,所以采用第二章中LISN上的傳導噪聲紋波作為紋波參考,其穩定后的紋波峰峰值為0.095V,負載電流為2.18A,因此目標阻抗設計為0.087Ω。

圖29、LISN端的噪聲電壓波形

3.1、隨機電容組合參數

采用siwave中的PI Advisor模塊對12V輸入網絡進行阻抗優化設計,查找siwave電容庫中對應封裝和容值的電容寄生參數,隨機選擇滿足封裝和容值要求的電容型號,其中C1和C4暫且用2816陶瓷電容替代,最終電容參數如下表所示。

表2、隨機選取的陶瓷電容參數

| 電容代號 | C1、C4 | C14、C16 | C12 | C2、C5、C13、C17 | C3、C6 |

| 容值 | 100uF | 47uF | 10uF | 0.1uF | 1nF |

| ESR | 46mΩ | 56mΩ | 4mΩ | 0.06Ω | 0.26Ω |

| ESL | 0.28nH | 0.45nH | 0.78nH | 0.82nH | 0.298nH |

| 封裝 | 08X10 | 1206 | 0603 | 0402 | 0402 |

3.2、優化電容參數

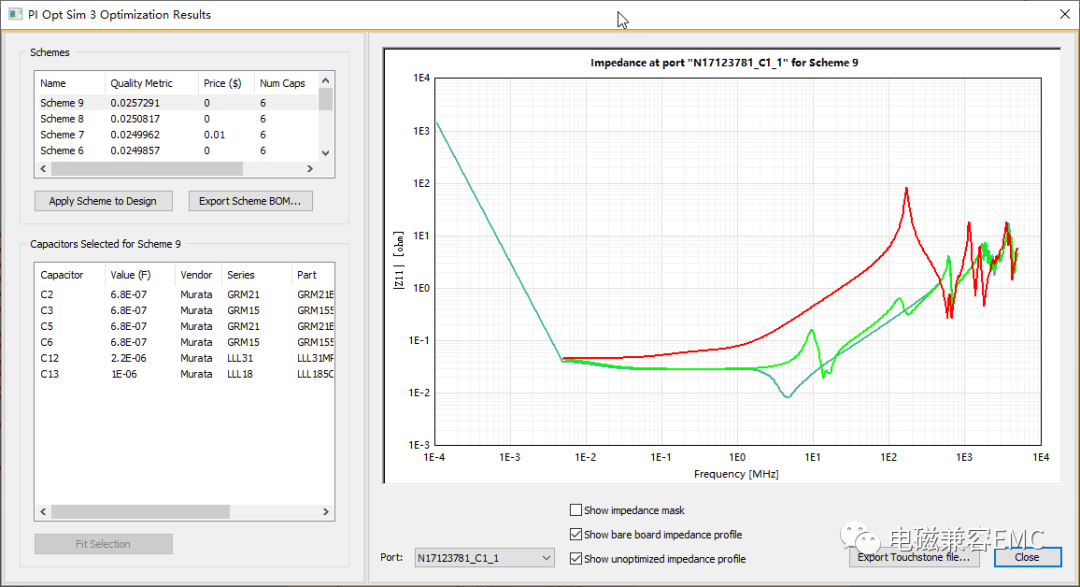

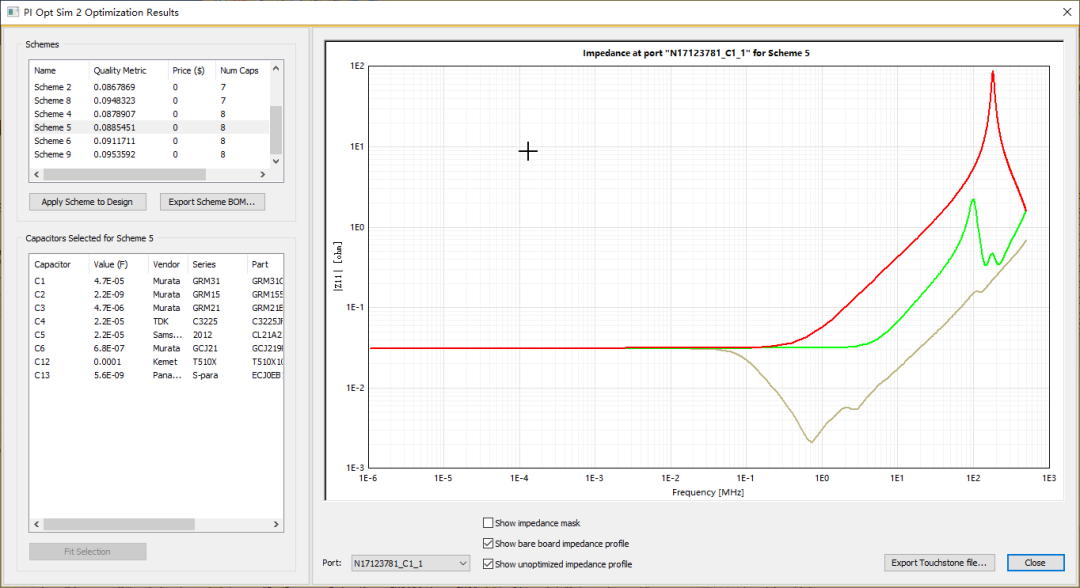

打開PI Advisor,選擇0.087Ω作為目標阻抗,得到10個優化方案,分別總結如下

圖30、十種優化方案的電容容值及型號

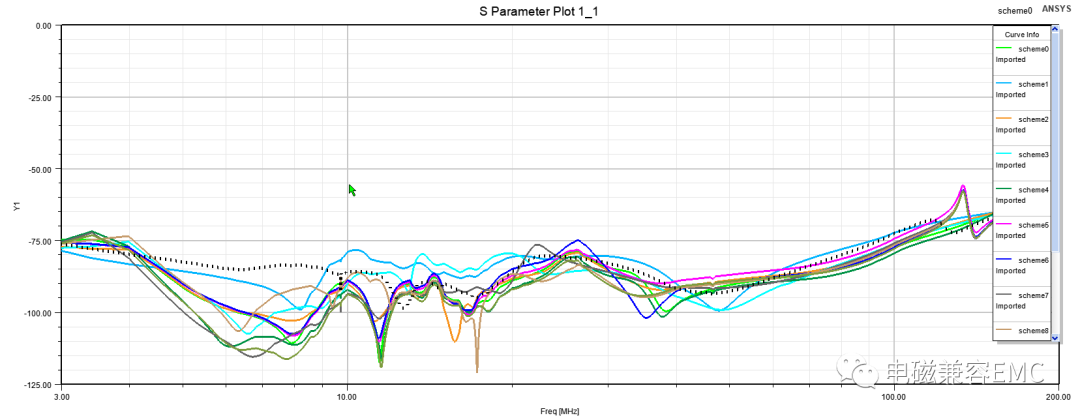

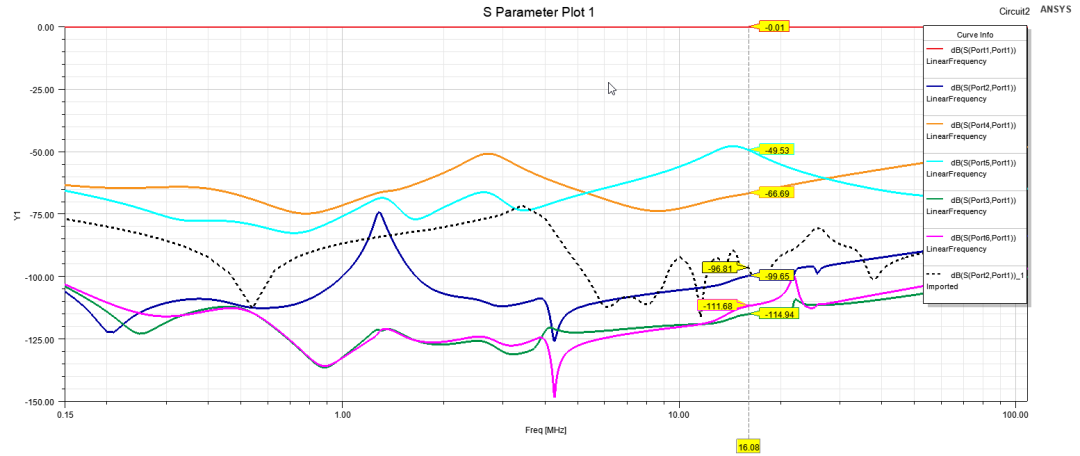

以上十種方案的輸入輸出隔離度結果對比如下,對比可見其中第4種結果的隔離度較好。缺陷在于該方案在低頻3MHz左右的阻抗高于初始方案。

圖31、不同電容方案的S參數對比

3.3、電容結果對比

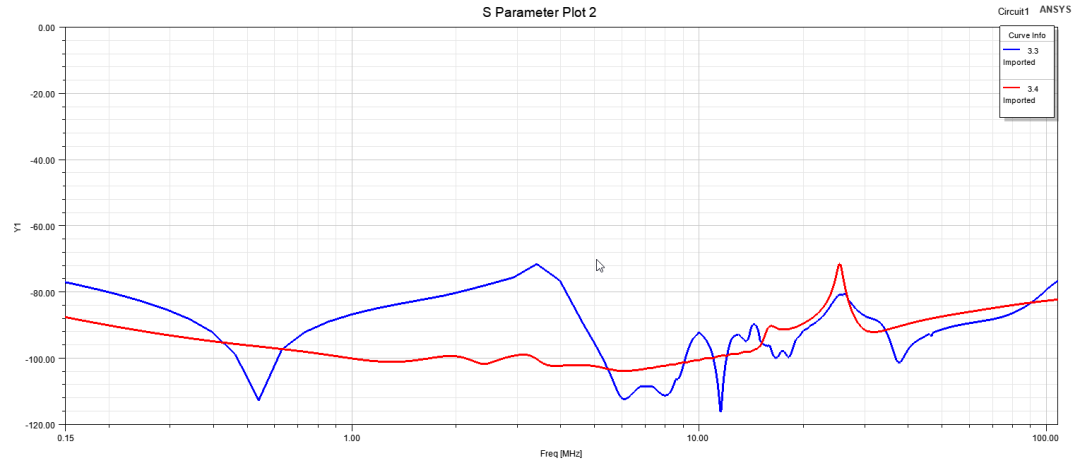

將3.1和3.2中Scheme 4的電容參數作為對比,分別帶入系統電路中,得到的傳導結果如下,從中可以看出,3.2節中的電容方案在3MHz以上的高頻部分具有較低的EMI傳導噪聲,而低于3MHz的部分,其噪聲幅值是高于3.1節中的電容方案的。

圖32、兩種電容方案在系統電路中得到的傳導結果

上圖中4MHz~10MHz部分,3.2節方案的結果是明顯低于3.1節對應方案的,這與圖32中的S參數結果是對應的。兩者分別采用了ANSYS designer和simplorer求解,采用designer求解所需時間為16秒,而采用simplorer求解所需時間為3個小時,對于需要優化濾波電路參數的工作來講,采用designer無疑是最快速的。

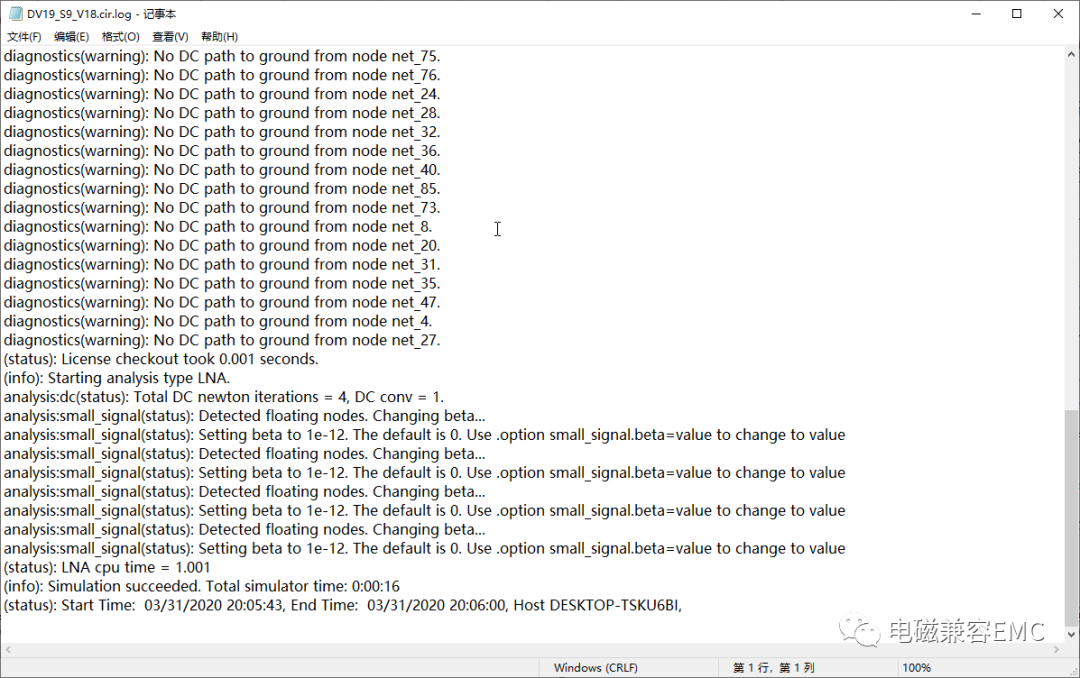

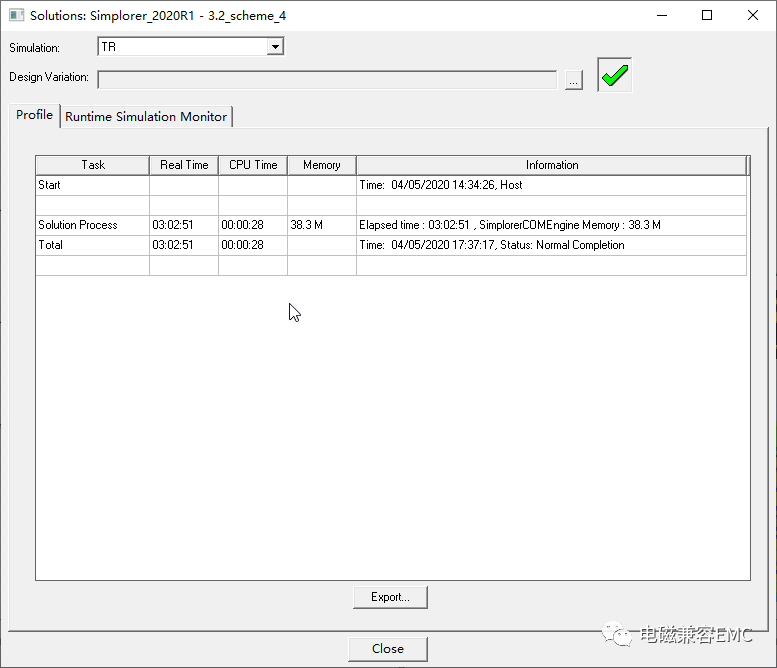

圖33、Designer仿真記錄

圖34、Simplorer仿真記錄

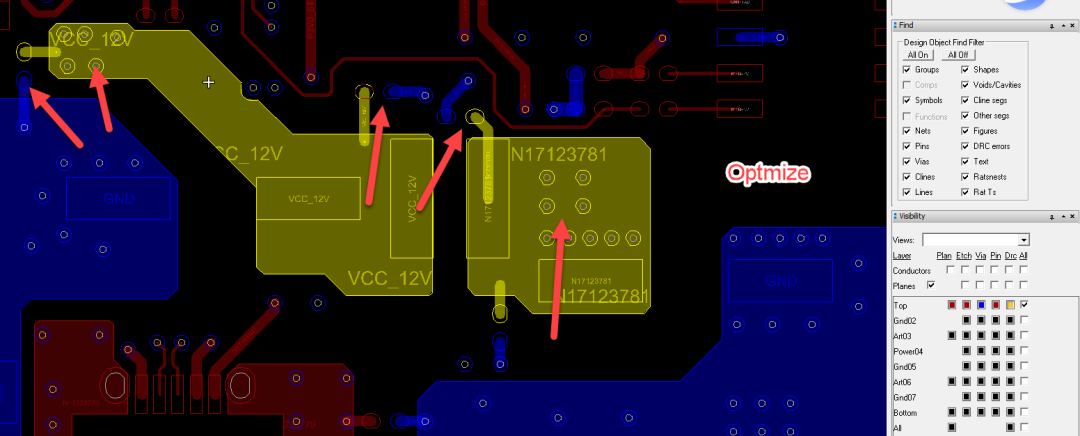

3.4、調整布局繼續優化

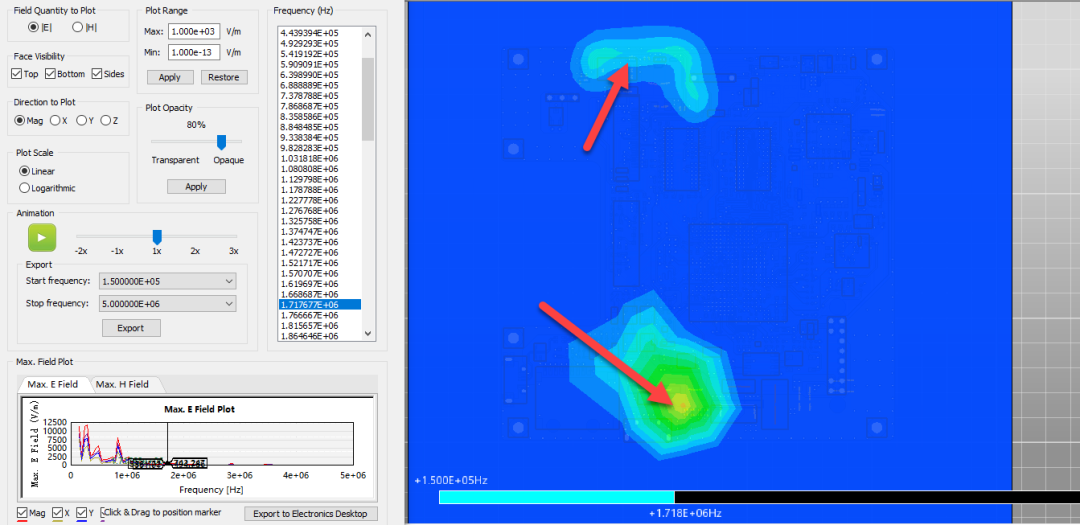

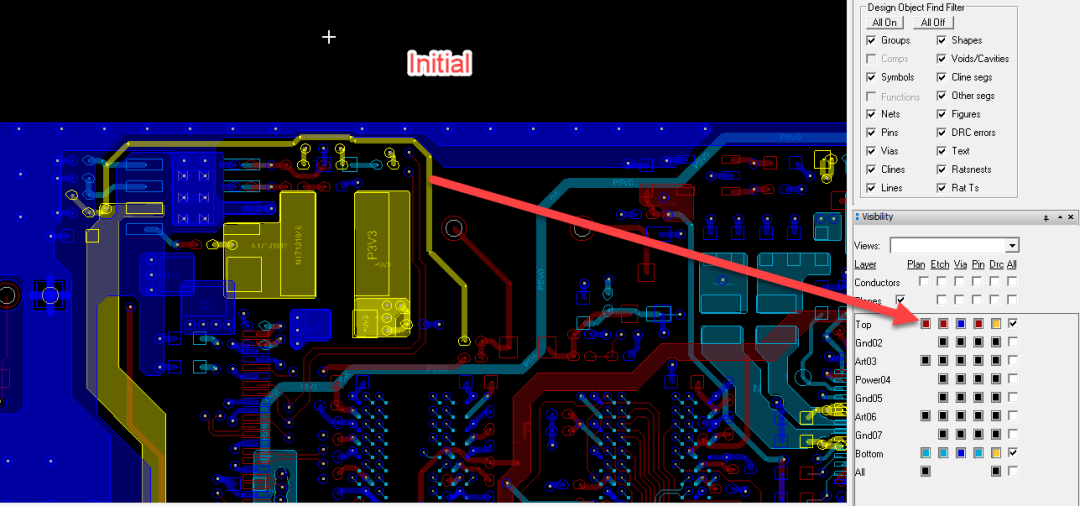

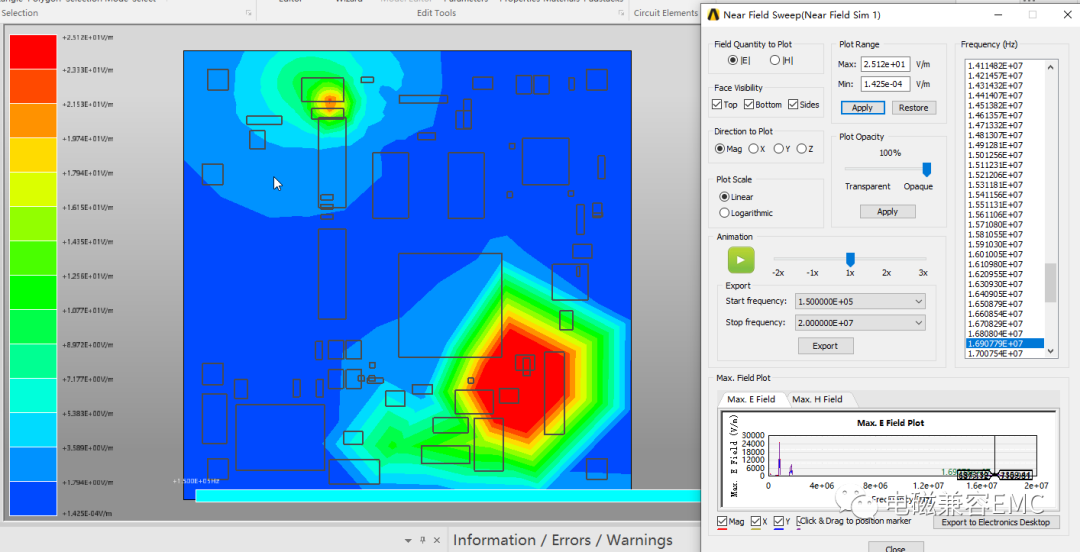

根據3.3節simplorer仿真結果,將其作為激勵源導入siwave中,進行近場仿真,獲取低頻噪聲對應的電場分布如下,可以看到1.7MHz頻率對應的近場噪聲主要分布在L2和U3位置的12V網絡,傳導噪聲分布主要在TOP層。

圖35、1.7MHz傳導噪聲的近場分布

檢查PCB布局,36-(a)可以明顯發現,初始狀態下12V網絡在Top層走包圍U3區域,(U3和P3V3在底層),由于邊緣效應,以及接近輸出在表層的FB信號部分走線,會耦合部分傳導噪聲,因此將其遷移到第二層,遠離板邊及其他敏感電源網絡。36-(c)可以發現,硬件工程師將C1儲能電容放在了L2之前,這是極其錯誤的做法,而且C1和C4兩顆電容均遠離U3,這都會增加U3從C1取電的阻抗。因為有D1防反二極管存在,后面可將D1修改為L1進行嘗試。另一個問題在于L1周邊的電容過于集中,所以將其分散開來,同時增加電源網絡過孔數量,在盡量不修改布局的前提下進行優化處理。

(a)

(b)

(c)

(d)

圖36、PCB優化前后

(a)(b)優化前;(c)(d)優化后

以上面PCB優化為基礎,導入初始狀態下的電容參數進行PI電源網絡阻抗優化,從優化結果中得到下面兩個低頻較好的方案,選擇方案5作為電容組合。

圖37、去耦電容優化

表3、電容組合參數

| 電容代號 | C1 | C2 | C3 | C4 | C5 | C6 | C12 | C13 |

| 容值 | 22uF | 22uF | 12nF | 47uF | 22uf | 2.2nf | 22uF | 1uF |

| ESR | 3mΩ | 3mΩ | 6mΩ | 2mΩ | 3mΩ | 135 mΩ | 3mΩ | 11mΩ |

| ESL | 0.4nH | 0.5nH | 0.345nH | 0.75nH | 0.5nH | 0.3nH | 0.4nH | 0.35nH |

| 封裝 | 0805 | 0805 | 0805 | 1210 | 0805 | 0603 | 0805 | 0603 |

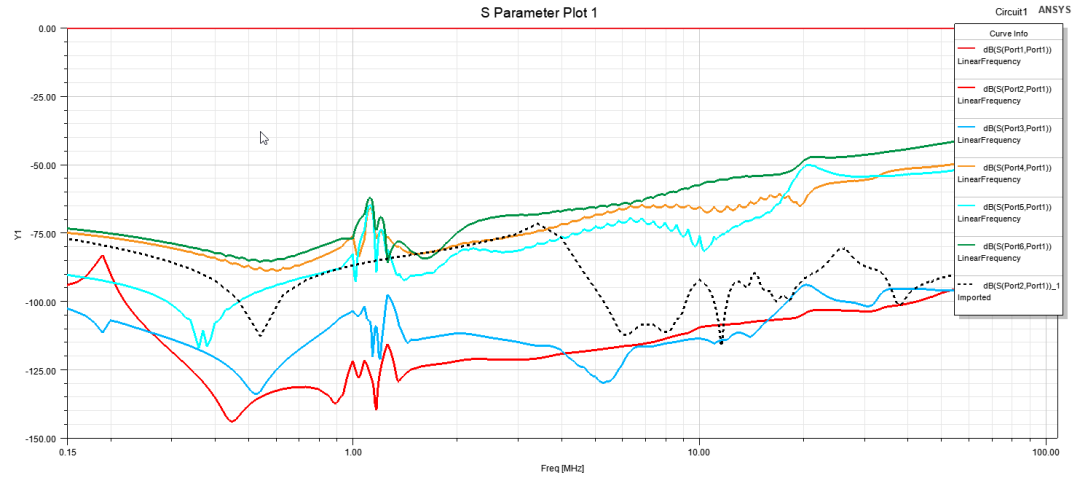

暫不考慮耐壓等其他問題,將其直接導入Designer仿真S參數,同時考慮電感部分,得到的S參數如下,在不同位置放置端口查看觀察不同位置的濾波效果,可以看到S21(連接器到電源芯片-藍色線)并不是插損最低的曲線,最低位置在D1和L2之間。

圖38、表3得到的S參數

將3.3節的電容參數導入進來,對比布局調整后的變化,如下圖所示,可以看到低頻有所降低,布局的優化使濾波電路整體波動降低了,所以說即便是輕微的布局調整對電源濾波電路效果的影響也是巨大的。

圖39、調整PCB布局前后后相同電容組合的S參數對比

根據designer中調整的情況,發現在調整L2到電源芯片之間的電容參數時,端口到電源芯片之間的S21結果變化不大,因此假設主要影響濾波電路性能參數的部分在于接口到L2之間,筆者在共模電感兩側和防反二極管位置增加X電容后發現,確實有明顯改善。由于PCB布局的不合理,重新布局會嚴重增加筆者的工作量,加上筆者個人水平有限(想偷個懶^_^!)優化部分到此為止。結果中的部分電容和電感對電源傳導噪聲并無有效濾波效果,所以我們可以嘗試將部分電容去掉Cutdown部分

圖40、優化后的S參數(黑色虛線優化前;紅色為優化后)

表4、最終電容參數

| 電容代號 | C1、C4 | C2 | C3 | C5 | C6 | C12 | C13 |

| 容值 | 100uF | 0.33uF | 47uF | 4.7nF | 1uF | 22uF | 1uF |

| ESR | 46mΩ | 12mΩ | 20mΩ | 120mΩ | 8.5mΩ | 3mΩ | 11mΩ |

| ESL | 0.28nH | 0.43nH | 0.4nH | 0.3nH | 0.61nH | 0.4nH | 0.35nH |

| 電容代號 | C01 | C02 | C03 | C04 | C05 | C06 | C07 | C08 |

| 容值 | 4.7uF | 4.7uF | 0.22uF | 2.2nF | 4.7nF | 15nF | 2.2uF | 4.7uF |

| ESR | 6.8mΩ | 6.2mΩ | 6.5mΩ | 180mΩ | 130mΩ | 57mΩ | 8.2mΩ | 6.3mΩ |

| ESL | 0.33nH | 0.37nH | 0.15nH | 0.45nH | 0.3nH | 0.5nH | 0.32nH | 0.55nH |

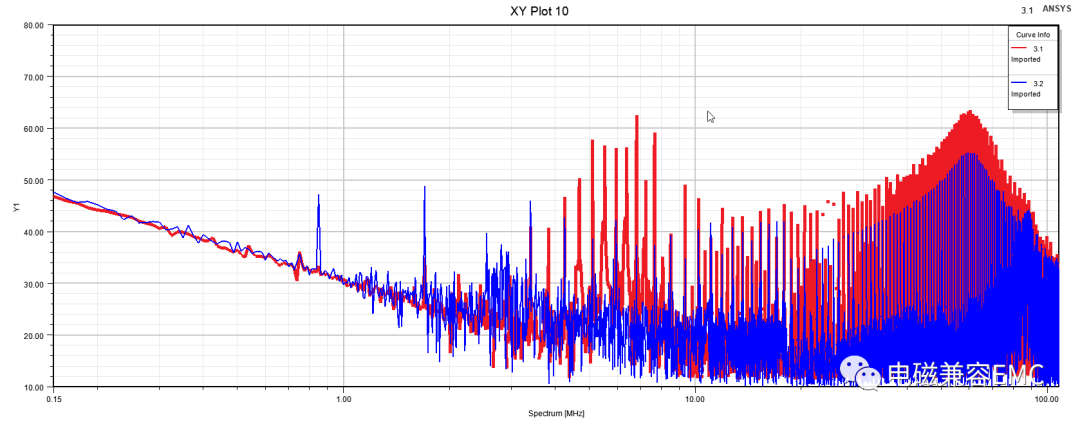

將得到的優化結果導入Simplorer進行系統電路仿真,得到的傳導結果如下,可以看到,除15MHz位置以外的整個傳導噪聲幅值均有下降,作為汽車電子產品,該頻段結果不做考察,所以這樣的結果勉強可以接受,對筆者來講純粹是為了偷懶,所以沒有繼續對電感部分進行優化。如果項目經理對產品的成本或者結構需求做出調整,那時我們就需要考慮每個EMI器件的必要性以及產品PCB布局的優化方向,當然這些需求都可以采用EDA工具進行快速的模擬。

圖41、優化前后的傳導電壓噪聲(藍色)

3.5、可做的其他工作

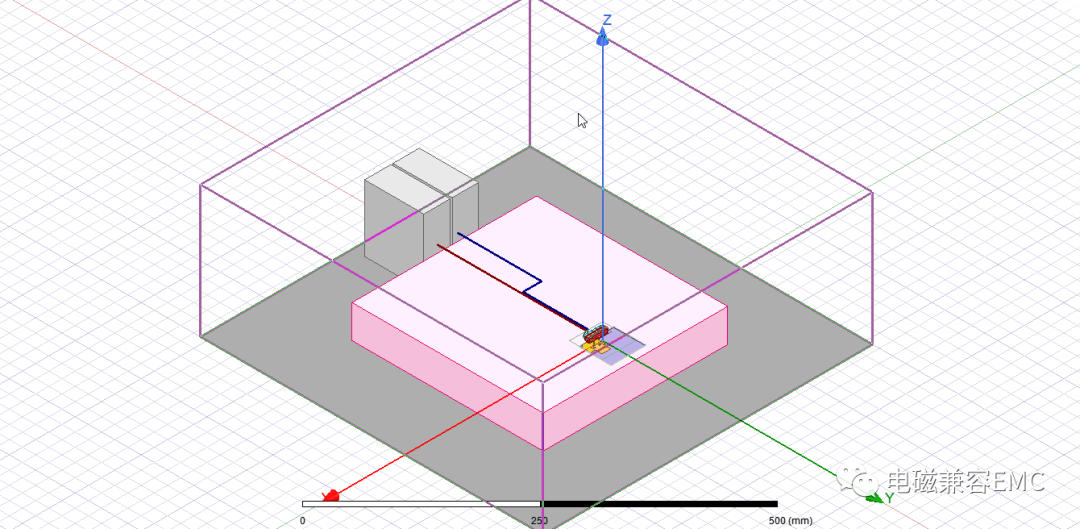

本次僅采用PCB文件對電源部分傳導噪聲進行仿真,對于需要考慮金屬外殼、散熱片以及復雜的外接線束所帶入的影響,需要采用Q3D或者HFSS進行三維準靜態/全波參數的提取,采用SIwave/HFSS與simplorer或者Designer的聯合仿真,在仿真結束后可以通過Push Excitations將電路仿真結果作為激勵源導入SIwave或者HFSS中,進行近場和遠場輻射仿真,以便使用者快速定位噪聲泄露途徑,優化PCB和結構布局,由于篇幅有限,這里僅貼個圖進行簡單描述,其余部分不再贅述。

圖42、符合CISPR 25標準要求的三維全波仿真

圖43、PCB的近場輻射

4、結語

系統電磁兼容的仿真,需要使用者同時掌握較多的軟件模塊,同時需要對系統關鍵環路響應狀態進行數字建模,在前期基于諸多測試數據的基礎上,不斷修正仿真中使用到的器件參數和系統仿真模塊參數,然后使用ANSYS 3D component將其封裝成可重復使用的器件庫,利用不斷的測試-仿真數據迭代,推進產品逐步走向正向設計。

-

電源

+關注

關注

184文章

17605瀏覽量

249562 -

開關電源

+關注

關注

6449文章

8290瀏覽量

480803 -

PID

+關注

關注

35文章

1471瀏覽量

85307

原文標題:基于PID閉環控制的開關電源傳導仿真[20200420_4A]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源的控制技術包含哪些種類

閉環控制的主要組成包括什么

雙閉環控制過程有哪些特點

雙閉環PID先調內環還是外環

開環控制和閉環控制的應用場景

PLC如何完成閉環控制及邏輯控制

閉環控制系統的工作原理和基本組成

閉環控制系統的原理和組成

基于PSIM軟件的BUCK開關電源仿真研究

基于PID閉環控制的開關電源傳導仿真

基于PID閉環控制的開關電源傳導仿真

評論