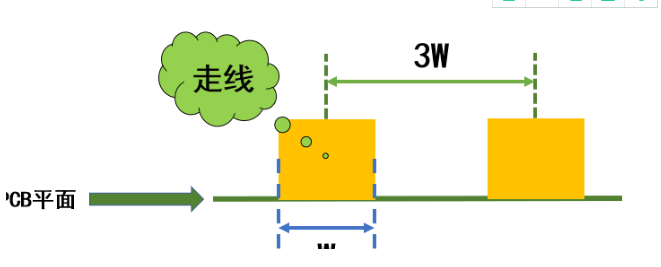

為了盡量減小單板設計的串擾問題,PCB設計完成之后一般要對線間距3W規則進行一次規則檢查。

一般的處理方法是直接設置線與線的間距規則,但是這種方法的一個弊端是差分線間距(間距設置大小不滿足3W規則的設置)也會DRC報錯,產生很多DRC報告,難以分辨,如下圖所示。

如何解決這個問題呢?可以利用Altium Designer的高級規則編輯功能、利用PADS的設計規則、利用Allegro、Mentor等對差分線進行過濾。

01

利用Altium Designer ……

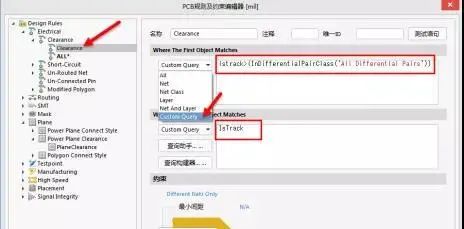

(1)按快捷鍵“DR”,進入PCB規則及約束編輯器,新建一個間距規則,并把優先級設置到第一位。

(2)如圖下圖規則設置,在“Where The First Object Matches”處選擇“Custom Query”,進入用戶自定義界面,然后再選擇“查詢助手......”,自定義幫助菜單。

(3)PCB規則及約束編輯器中存在高級工具菜單欄,包含“+”“-”“*”等。

這些可用于編輯高級規則,這其實和編寫C語言代碼類似。由于高級代碼的使用頻率較低,在此不做說明,如果讀者想了解可以參考Altium Designer的官方文檔,弄清楚每一個代碼的含義再進行編輯。

在此,在自定義代碼編輯框中輸入“istrack>(InDifferentialPairClass('All Differential Pairs'))”,表示的含義是不包含差分走線的導線。

(4)在“Where The Second Object Matches”處適配“IsTrack”,那么整個規則的含義表述為除了差分線之外的導線和導線之間的距離。

(5)按快捷鍵“TDR”,重新運行DRC,可以得到下圖所示的走線間距規則的結果,差分線之間的間距只有8.6mil,不滿足設計的3W規則12mil,但是不再進行報錯。

02

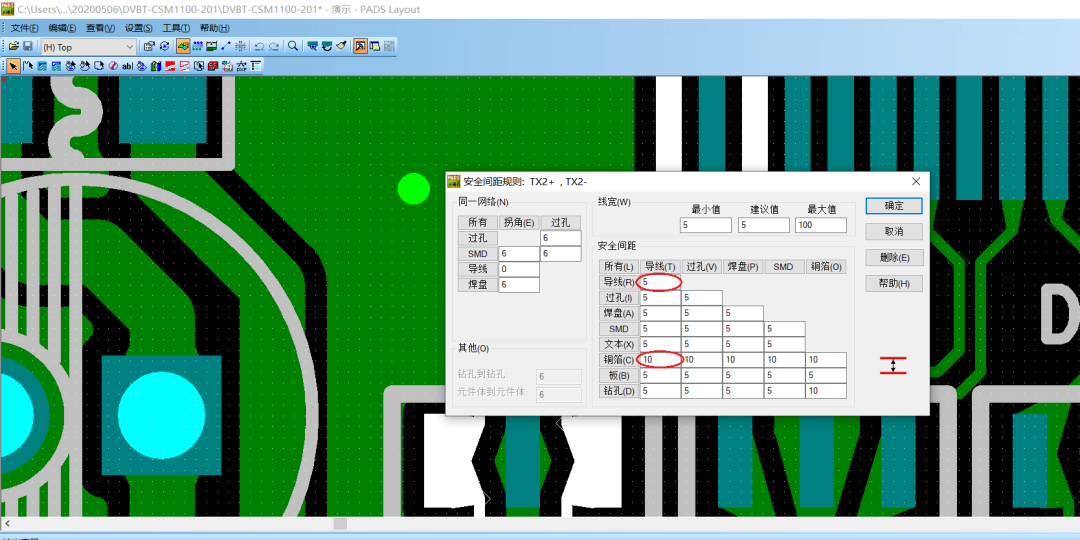

利用PADS ……

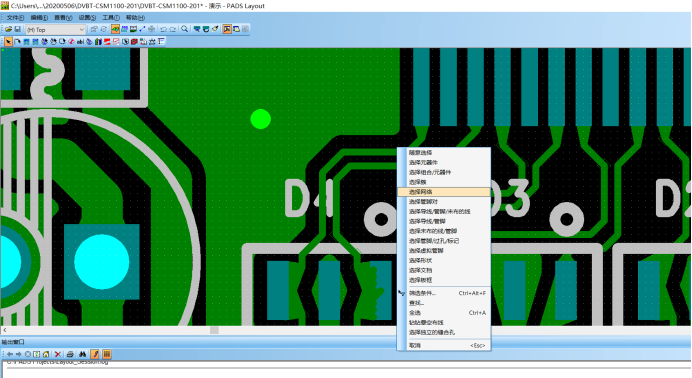

第一步:右鍵選擇網絡:

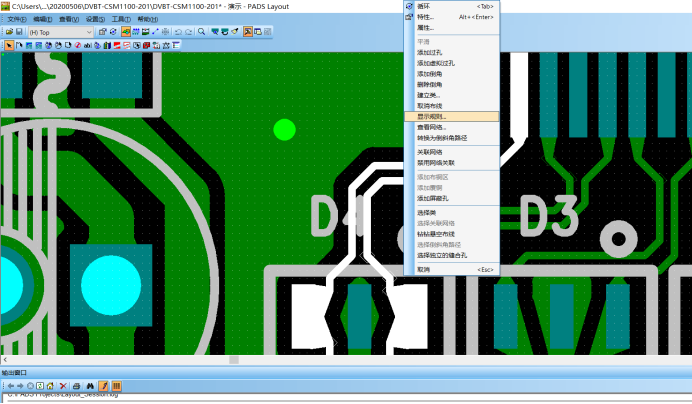

第二步:顯示規則:

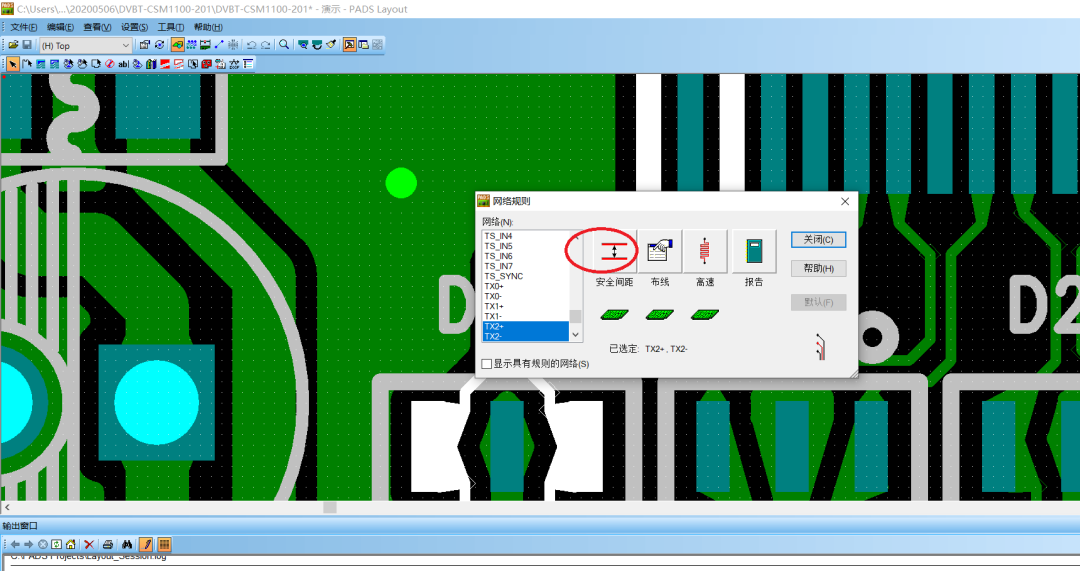

第三步:選擇安全間距:

第四步:修改規則:

完成后重新灌銅,就不會再出現DRC了。

03

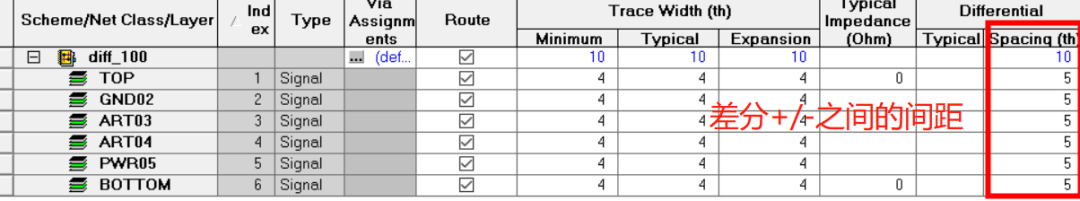

利用Allegro ……

Allegro里面,如果設置了Space約束(比如diff的3w規則),或者默認的space數值大于Primary,就需要添加一個參數,負責差分正負之間也會按照3w規則報drc,解決方法有兩個。

方法1:

約束管理器里面,點擊Physical---Physical Constraint Set---All Layers,把Min Line Spaceing的數值改小,且必須小于Primary的數值即可。

方法2:

給差分添加一個Diffp_Min_Space的屬性,Value值小于Primary的數值即可。

04

利用Mentor ……

肯定會有網友詢問,除了以上三個常用軟件,Mentor如何對線間距3W規則進行規則檢查?Mentor軟件比較智能,會自動識別差分正負之間的間距和差分對與差分對之間的3w,即:利用規則推動設計。

你常用哪種方法去檢查3W規則呢?如果還有更好的“招數”,可以文段后討論哦~

-

pcb

+關注

關注

4317文章

23006瀏覽量

396301 -

altium

+關注

關注

47文章

942瀏覽量

118035 -

DRC

+關注

關注

2文章

148瀏覽量

36128

原文標題:如何用AD、PADS、Allegro、Mentor?對3W規則進行檢查?

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Jtti:常用的網絡質量監控方法有哪些

求推薦與TPA6205A1管腳兼容的,并且3W以上的功放芯片?

瑞薩電子FemtoClock 3W時鐘解決方案解析

不按INTEL的“3W-2S”規則設計,出問題的概率有多大?

磁共振檢查常用線圈及分類方法

3W高效升壓轉換器,采用 MicroSiP?封裝TPS81256數據表

PCB設計時,哪些信號需要遵循“3W原則”?

你常用哪種方法去檢查3W規則呢?

你常用哪種方法去檢查3W規則呢?

評論