Synopsys、Cadence及Mentor Graphics(2016年被西門子并購)三家企業把持著全球60%,中國95%的EDA市場,通俗點說,中國的IC設計企業幾乎沒有不用他們產品的,無論盜版還是正版。而且三巨頭有著一般企業難以逾越的知識鴻溝,這些鴻溝并不僅僅是靠自身的技術沉淀與自主研發得來的,更多的是依靠商業手段拿下的。

國外EDA企業:

Synopsys(新思科技):成立于1986年,由Aart de Geus帶領通用電氣工程師團隊創立,在2008年成為全球排名第一的EDA軟件工具領導廠商,為全球電子市場提供技術先進的集成電路設計與驗證平臺。Synopsys在EDA行業的市場占有率約30%,它的邏輯綜合工具DC和時序分析工具PT在全球EDA市場幾乎一統江山。

Cadence(鏗騰電子):是EDA行業銷售排名第二的公司,在1988年由SDA與ECAD兩家公司兼并而成,Cadence通過不斷擴展、兼并、收購,到1992年已占據EDA行業龍頭地位,但到2008年被Synopsys超越。Cadence產品涵蓋了電子設計的整個流程,包括系統級設計、功能驗證、集成電路綜合及布局布線、IC物理驗證、模擬混合信號及射頻集成電路設計、全定制集成電路設計、PCCE設計和硬件仿真建模等。全球知名半導體與電子系統公司均將Cadence軟件作為其全球設計的標準。Cadence的Virtuso工具歷經27年不衰,成為業內傳奇。

Mentor Graphics(明導國際,2016年被德國西門子收購):1981年成立,90年代遇到經營困境,軟件的研發嚴重落后于進度,大量長期客戶流失。直到94年公司組織結構大調整后,才重新崛起。MentorGraphics是一家EDA軟件和硬件公司,也是電路板解決方案的市場領導者,主要提供電子設計自動化先進系統電腦軟件與模擬硬件系統。Mento的工具雖沒有前兩家全面,沒有涵蓋整個芯片設計和生產環節,但在有些領域,如PCB(印刷電路板)設計工具等方面有相對獨到之處。

國內EDA企業:

北京華大九天:規模最大,世界唯一提供全流程FPD設計解決方案的供應商,具有較強市場競爭力,布局領域:IC設計、IC產品、平板顯示電路設計。

杭州廣立微:在良率分析和工藝檢測的測試機方面產品具有明顯優勢,布局領域:高效測試芯片自動設計、高速電學測試和智能數據分析的、全流程平臺。

蘇州芯禾科技:專注仿真工具、集成無源器件IPD和系統級封裝SiP微系統的研發,布局領域:設計仿真工具、集成無源器件。

天津藍海微科技:在PcellQA工具領域技術實力雄厚,具有自動化程度高、檢查項全面、準確性高和支持先進工藝特殊處理等多項優勢,布局領域:集成電路工藝設計包。

北京芯愿景:集成電路技術分析能力始終緊跟半導體行業最先進工藝制程的發展步伐,目前已成功實現7nm FinFET芯片的工藝分析和電路分析,布局領域:IP核、EDA軟件、集成電路分析設計平臺。 北京博達微科技(被概倫電子收購):以SPICE Model參數提取著稱,現重點轉向數據端,從加速仿真轉為加速測試,測試主要以學習算法來驅動,競爭力在于測試速度比傳統測試高一個數量級,布局領域:半導體參數測試、器件建模與驗證。 濟南概倫電子:在SPICE建模工具及噪聲測試系統方面技術處于領先地位,業內稱“黃金標準”,布局領域:高端集成電路設計、先進半導體工藝開發。 蘇州珂晶達:專業提供半導體器件仿真、輻射傳輸和效應仿真等技術領域的數值計算軟件和服務。公司的主要服務對象為微電子、宇航和相關科研單位。公司產品的特色在于深入理解物理原理,并用軟件高效地實現,使得能在工程實踐中快速應用。半導體器件仿真(TCAD)是珂晶達公司的一項核心技術。公司研發的 Genius 器件仿真軟件擅長大規模高速 TCAD 仿真。受益于新算法半隱式求解器,Genius可以仿真包含幾十個晶體管、超過一百萬網格點的大規模問題。同時,局部犧牲一些精度(《 5%)的情況下,計算速度可以較傳統算法快 5-10 倍。

成都奧卡思微電:專精形式化功能驗證,可編程邏輯驗證,低能耗設計優化及驗證等技術,布局領域:形式驗證工具,全流程設計工具。

深圳鴻芯微納:成立于2018年,旨在通過自主研發、技術引進、合作開發等模式,完成數字集成電路EDA平臺關鍵節點的技術部署,打造完整的集成電路設計國產數字EDA平臺,實現國有半導體產業鏈在這一關鍵環節的技術突破;公司將依托國內完整的產業生態,組建專業的研發和支持團隊,建設具有競爭力的技術平臺,致力于在廣闊的工藝節點和應用領域,為全球集成電路設計業提供全方位的解決方案和技術服務。

若貝(Robei):若貝(Robei)是由美國硅谷的工程師創建的新型集成電路公司,擁有自主知識產權的若貝自適應芯片和Robei EDA軟件。公司于2012年在美國內華達州拉斯維加斯市注冊,成功研發Robei EDA軟件,一種全新的面向對象的可視化芯片設計軟件,有很多世界500強的公司員工參與試用。

南京創聯智軟:是國內領先的企業級研發管理、知識管理解決方案提供商,是軟件工程生態化治理的倡導者及踐行者,基于大數據、人工智能等技術打通研發測試工具鏈,貫穿整個研發流程,提供專業化定制開發服務的軟件生命周期智能化解決方案。在“軟件定義裝備”的背景下,為中國制造業裝備軟件聚力賦能。創聯智軟成立2014年7月,具有國家軍工相關資質、ISO 9001:2015/GJB 9001C-2017質量體系認證,是國家認定的雙軟企業和國家級高新技術企業。

這些天看了不少講國內EDA情況的帖子,有客觀的也有極其離譜的,作為一名從業十余年的芯片設計工程師,我以一線從業者的角度來談談我們在實際工作中的EDA軟件使用情況究竟是怎樣的吧。

先回答個很常見的問題:沒有了美國的EDA,我們是不是芯片都不能做了?這也是促成我寫這篇文章的因素之一吧。

我的簡要回答是:180nm/350nm以上的部分老工藝線是可以用破解版或國產替代版繼續做的,但深亞微米級130nm/90nm開始就很難離得開正版授權了,越往下越難,到了22nm以下,就完全不可能了。

和大家熟知的office, autocad等工具類軟件不一樣,這種軟件很純粹,脫機都可以用,完了打印出來就可以;芯片EDA工具軟件的最大特點是它與芯片代工廠具有高度的綁定關系,因為我們設計時,是需要代工廠提供數據包的,稱之為PDK,包含了諸如晶體管,MOS管,電阻電容等基礎器件或反向器,與非門,或非門,鎖存器,寄存器等邏輯單元的基本特征信息,這個數據包會不斷優化,更新頻繁,同時對EDA軟件有綁定及校驗的作用,一般只支持當前最新版的工具。

好的,首先我必須要講明白為啥必須要使用自動化設計軟件(EDA),否則我后面都是白說, 這部分懂的同學請直接往后拉,從第二部分開始看。文章有點長,受不了的請直接看第四段。

文章分五個部分:

一。為什么要用EDA;

二.EDA圈子的那些事;

三 。不得不提的IP

四。破局

一、為什么要用EDA?

EDA,Electronic design automation,中文叫電子設計自動化。

最早的集成電路是用手工做的,因為就幾個管子,前端可以手工完成其功能的計算,后端版圖就根據電路圖,將管子,連線用筆轉移為幾何圖形,畫出膠帶(算是掩膜的老祖宗),因為管子少,線也簡單,所以不容易出錯。這是60年代——70年代中期的事情。(國內有些公司十年前都還在用,不知道現在如何。)

但是,到了幾十個,幾百個器件或單元的時候就不行了,肉眼非常容易出錯。

比如這種:整個模塊也就五百多個管子吧,截了大概5%的區域出來,這個人手工怎么做呢,做完怎么保證百分百不會錯呢,如果用自動布局布線工具,大概也就幾秒就運行出來了,而且不會錯。

數字網表導出來的電路圖

這個自動布局布線出來的版圖,用了7層金屬,上千條毫無規律的線,試問怎么去畫?怎么去查?

數字版圖

這是目前比較典型的一個SOC(system on chip)芯片(CPU就是SOC的一種)的圖,里邊包含了數字電路也包含了模擬電路IP,上面這個數字版圖的截圖,可能只是下面這個完整版圖的千分之一,甚至更少,

你要知道最古老的SOC里的晶體管都是千萬級以上,現在的個數更是動輒就是幾億,甚至上十億:

典型的SOC示意圖

一條線連錯了,可能整個產品的功能就變了,也就是你花幾千萬,只能得到一堆人都砸不了的板磚。之前所有投入全部打水漂。一般來說制程越先進,制造和研發費用愈來愈昂貴,哪怕是很老的0.5um, 0.35um的工藝,

雖說只要幾十萬,幾百萬,但那也是錢哪,更別說到了28nm下制程動輒都是千萬級美元的費用,10nm,7nm更是億級美元了,流幾次片沒成功直接倒閉的公司數不勝數。所以必須使用計算機來輔助設計!

二、EDA圈子的那些事

1)EDA的選擇

做了張腦圖,大家先看下芯片的大致流程:

當然實際設計中會更為復雜,并隨著制程的變小,會進一步加劇流程各環節的復雜度以及增加環節內部的新的驗證項目,但大體還是以下步驟:前端設計和仿真——后端設計及驗證——后仿真——signoff檢查——數據交付代工廠(以gds的形式)

稍微解釋一下幾個重要概念:

Signoff, 中文翻譯叫簽核,比較抽象,簡單說就是按廠家的默認設置要求做最后一次的規則驗證,通常我們在設計的時候,會將廠家要求的標準提高一些來做。

后端設計:可以理解為將電路從器件符號形式轉為幾何圖形形式,以指導掩膜版的設計。

然后,我把設計流程里各個環節能用且好用的軟件列一下(可以看到基本都是Cadence, Synopsys, Mentor三家的產品):

模擬及混合信號類(包括模擬前端設計及仿真,模擬后端設計及驗證,芯片后仿真):

電路及版圖設計工具:Virtuoso (Cadence), 0.18um,0.35um等老工藝可以用L-edit.(這個不受限)

版圖物理驗證工具:Calibre(Mentor),老工藝還能用Assura(Cadence),dracura(Cadence更老,十幾年前剛畢業那會兒用過)

版圖參數提取工具:Star-RC(synopsys),Calibre XRC(Mentor),QRC(Cadence)

電路仿真工具:Hspice(Synopsys) ,Spectre(Cadence), ALPS(華大九天,中國)

數字及SOC類(數字前端,數字后端,驗證,仿真):

RTL綜合工具 :DC(Design compiler,Synopsys)

仿真驗證工具:VCS(Synopsys), ModelSim(Mentor),Incisive,Indago, MDV,VIP(Cadence)

數字后端設計工具:ICC(Synopsys),Innovus/Encounter(Cadence) 還有180nm制程可用的老掉牙的Astro( synopsys)。

DFT工具:DFT Compiler (Synopsys)

物理驗證工具:ICV(Synopsys)PVS(Cadence), Calibre(Mentor)

signoff 時序/噪聲/功耗分析工具:Prime time, PT(synopsys),PrimeRail(Synopsys) ,redhawk Fusion(Synopsys, 這套flow產品的核心redhawk是ansys的產品,ansys為s家戰略合作),Totem(Ansys, 美國)

PCB:

Allegro(Cadence) :這個還好,不更新也沒太大個問題。

這里再簡單說下國內的EDA情況,反向提圖抄襲軟件其實是走在世界前列的,芯X景(據說還要上市圈錢),客戶除了早就被拉黑的外,都不敢說用了他家產品,怕吃官司,這種不值得提倡,因為他們干的事早已超出了他們所宣稱的只用于合理學習的底線;

正向設計里目前真正得到認可的只有華大九天(我為他們點個贊),但主要是模擬產品上,具體的說是模擬電路的仿真工具(ALPS),再細化下是電源類產品的仿真上,有他們的獨到及NB之處,他們也有對標 virtuoso的兼容性產品Aether,但是得在成熟工藝下用。國內的EDA依然處于一個輔助角色狀態,還有很長很長的路要走。

可以這么說,世界上所有的芯片設計公司,不管你是5nm還是350nm吧,無論你多NB,多逆天,肯定采用了這三家的至少一種軟件,哪怕是盜版 。

2)設計平臺化產品閉環

Synopsys和Cadence一貫的發展戰略是平臺性發展,也就是說并不是某個環節的設計軟件強,而是從前端設計-前仿真/驗證-后端設計-后端驗證仿真直到流片的整套產品都很強,并形成設計的閉環,比如synopsys的Milkway, Cadence的OA(OpenAccess)。。

粗略的說,模擬/數模混合芯片設計用cadence平臺,數字芯片設計采用synopsys平臺,當然實際并非如此絕對,有一定的交叉使用情況。。對于客戶來講,他們自然會傾向于平臺化的EDA的采購,而不是分門別類的買,因為省事就意味著省錢啊,除非你的某項產品極其NB,

比如Mentor的功能或物理驗證產品,Ansys家的功耗分析軟件,那確實厲害,尤其是物理驗證C,S兩家真干不過,已經是全球所有代工廠公認的金標準,也迫于壟斷壓力收不了,那只能戰略合作。

3)與工藝廠的捆綁 (EDA聯盟+IP聯盟)

然后呢,EDA的壟斷還體現在于工藝廠的捆綁上,工藝廠早期要進行工藝研發,勢必也要進行器件,簡單功能芯片的設計,要設計就得基于eda設計平臺支持,這時候Synopsys, Cadence等EDA公司就來送溫暖了,他們甚至會免費直接幫你設計多種基礎IP, 各種規模的功能IP以擴充你的IP庫,IP庫越大越全,對客戶的吸引力也就越大,win-win;

在功能驗證,物理驗證環節,則有Mentor的一席之地,物理驗證會貫穿并頻繁往返于后端設計的全流程,對于軟件的效率和可視化要求很高,這點calibre做得非常好。另外EDA供應商還會給學校客戶優惠價甚至免費,其目的也很明顯,培養用戶習慣,除非學校也是光榮的上了美帝黑名單。

也就是:EDA 工具+IP授權的捆綁。

這樣一整,進入投產階段后,工藝廠發給客戶的PDK設計包自然也只能支持 Synopsys, Cadence,Mentor的了,其他的EDA替代品,多在兼容性上做功,并且無法提供平臺化產品,加上兼容和原生,在時效及使用上都有很大的差異。。

一旦做強了還面臨著Cadence,Synopsys的收購/絞殺威脅。還是那句話,人家提供的是平臺,除非你能像Mentor那樣提供整套驗證平臺也可。

三、不得不提的 IP

EDA說完了,再說說IP,IP對于今天SOC設計的重要性不用贅述了, Synopsys, Cadence的另一個殺手锏級的壟斷產品:接口類IP,

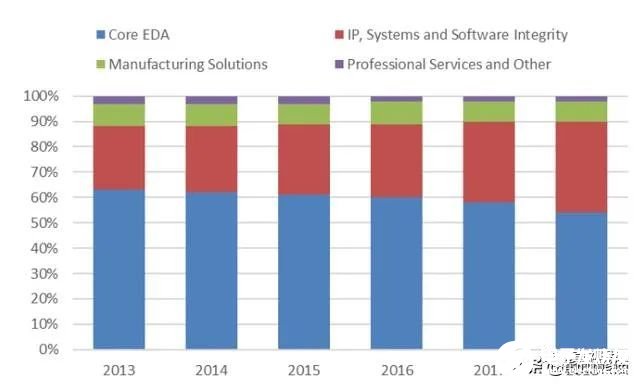

這是每一顆SOC必不可少的東西,比如:高速SerDes, ethernet以太網,PCIE, CPRI, SATA,USB,Type-C,MIPI, HDMI,DP.。.還有DDR; 如下圖所示,Synopsys 的IP業務在總營收里占第二。

Synopsys 2013~2018的產品及服務的營收占比

貌似從65nm開始吧,每一代工藝出來的早期基本只有Synopsys和Cadence兩家可選,因為這兩家是先進工藝研發的唯二工藝-產品的設計及驗證平臺,他們老早就進去了,至少是從設計PDK(芯片設計工具包)開始,產線開放后,陸續才會有其他IP供應商或自主研發的接口產品可用,

但到了14nm開始,除S,C兩家外,很長時間基本只有rambus, aphawave,esilicon等公司的IP可用,rambus,esilicon是美國公司,alphawave是加拿大公司,加拿大你懂的,不過華為是他們的T1客戶。。。

但是7nm,5nm下,能做到所有類型的接口IP都提供的,還是只有Synopsys或Cadence。就在前天,Cadence發了款TSMC 7nm的超高速112G/56G 長距離SerDes,用于云數據中心和光網絡芯片,5G基礎設施的核心IP。

SMIC14nm的10G多協議PHY IP也是他們獨家的,5月14日發布的。然后我來一張2019年半導體IP廠商TOP10榜單:

榜單中前三個就不說了:

SST:得益于NVM接口的流行,直接從十名開外, 沖到了第三。(總部美國加州)

imagination(一家被中資背景的美國私募控制的英國公司。。??) ,其主要產品是GPU IP,國有化了,但這兩年垮得很厲害;

Verisilicon(芯原,重點提一下,這家主要研發力量在中國,外面名氣不大,但業內名氣很大,很NB,作為研發力量主要在中國的公司,海外營收竟然占了70%+ ,不乏谷歌,Facebook、博世、亞馬遜、英特爾、恩智浦,高通,華為這樣的巨頭客戶。

全球IP供應商排名里排第7,國家大基金和小米這兩年都投了他們,昨天科創板上市已經過會了,是家中國公司。他們雖然技術儲備不錯,但體量偏小而且研發投入占比極大,所以財報不太好看,后面看資本注入后,有進一步擴張并做大的機會,看好他們厚積薄發。

他們的重要布局是Globalfoudry, Samsung 22nm FDSOI產線的低功耗產品,是三星和GF的IP聯盟中的戰略合作伙伴。

Achronix(美國), 主要是FPGA;

eMemory,看名字就知道memory。

四、破局

下策:用盜版EDA。國內有公司這么干,省錢是一方面,主要還是因為上了黑名單,人家給錢也不賣,用盜版軟件設計好,然后交給第三方代理公司處理,投片,然后交給廠家代工,但是這基本只能在0.18um甚至更高的制程的產品,65nm以下的產品基本上很難。(現在這種代理公司越來越少了,黑名單都快拉滿了。)

我就不說這玩意兒不能破解了,我相信這世界上沒有絕對無懈可擊的防御體系,哪怕這幾家的物理license manager體系設計幾乎已經做到了世界最好。

主要原因還是我剛剛說的工藝廠和EDA利益綁定的問題,工藝廠的設計數據包(PDK),尤其是驗證文件的更新非常頻繁,尤其是新工藝,因為隨著各種測試片,量產版的測試反饋,會不斷的調整器件模型,設計規則,不斷迭代,讓良率達到最高,一個月一更的都見過,甚至是1.x版本直接升到2.x版,都不是0.0x這么微小迭代。這種幅度的更新讓設計重來的都有。

幾個頂級代工廠的工具基本都是用最新版本,所以放出來的更新PDK也是用最新版工具校驗, 你老的工具很可能就得跟著更新,盜版根本來不及,也沒什么人愿意干這種費力不討好的事,所以能找到盜版的幾乎都是老點的版本。

除非是老工藝,比如臺積電的0.18um,貌似七八年沒更新了,因為已經完美了,就不存在過期這種問題。

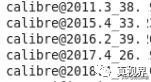

比如說之前做28nm以下模擬設計,最早還能用virtuoso的ic6.16, 6.17,到后來成了ICADV122,直到現在只能用ICADV123, 驗證就更快了,一年一代。比如這個Mentor 的Calibre,一年一個大更新,里邊還有小更新,17年的是打不開19年的工具校驗過的數據的,一個版本對應一批License(按個數賣):

Mentor Calibre版本示意

這也是為啥license一般都是買短期的,也可以稱之為租賃,終身買斷的那是家里有鉆石礦的。

如果對你停止了技術支持,那么也就意味著更新停止,License沒停你老的可以接著用。當年中興被封殺時,網上泄露出的Cadence群發郵件也提到過,但是實際上,我了解到的華為被制裁的沒中興那么慘,中興當時是直接一刀下去的。而華為不是,因為美國想拿這事作為重要的談判籌碼,而不是直接毀掉籌碼,終止談判。

最后,你盜版設計好的數據,為什么得拿給第三方潤一下(潤筆費可不菲。),也是因為數據在制版前,工藝廠還會校驗,因為license是與公司物理名稱及專用license服務器網卡地址全部綁定的,數據來源不明的不會給你流片的。

有人說,那我們自己的工藝線呢,悄悄的不行嘛?芯片產業是個發展了幾十年的全球化的鏈條,所謂的3+2結構,一家做不完全部環節。各種背景的人湊一堆玩一個游戲,最講究的就是一個游戲規則,哪怕這個規則有問題,但是絕大多數的人愿意相信就沒問題,比如常見的就是不能把客戶數據偷去自己生產自己賣,或賣給其他公司;

維護IP及工具聯盟的利益,不接來歷不明的單;一旦有人破壞規則,就會被全聯盟抵制甚至出局。(就好比大家在玩中國象棋,你非得說悔棋可以或要用國際象棋的規則來玩。)

芯片3+2結構

中策上策:先打局部戰爭,不要一來就想整個大的,建立一個獨有的體系,逆全球化是逆勢而為,是特沒譜才干的事。某國越封閉,咱們就越開放,讓自己在全球體系有自己的位置,哪怕一開始微不足道。

扶持本土EDA的發展,但需要很長的路要走,技術壁壘,專利壁壘這種東西并不是砸錢就可以破掉的,華人工程師在美國本土被防得很死,尤其是在核心技術上;而且EDA這個行業很燒錢,未來回報遠遠比不上互聯網行業,其總的市場規模也就100億美元,這個只能靠扶持。

另外,我再說一次,反向抄襲軟件不在討論之列,這種流氓盜版公司請讓他死掉,他們是導致芯片行業惡性及下作競爭的推手(這些年因被抄襲而死掉的不少是國內的有技術有創新的初創公司),這是我的一貫觀點。

但是,我們沒必要一來就以徹底取代為目的,可以從局部突破,把某一類工具做到極致,比如現在華大九天的模擬產品仿真工具就是一個很好的突破口,想Ansys那樣,成為工藝廠的金標準,人家想踢你都踢不掉,客戶不答應啊。

EDA-IP-工藝廠需要協同發展,各司其職,讓專業的人做自己最擅長的事,避免惡性競爭,才是效率最高的策略。在EDA還沒起步的時候,就先為現有的能在世界上排上號的IP公司和代工廠,促成IP聯盟,然后再帶動EDA的發展。

有人說講這些有啥用,是讓我們認命,認慫,知難而退的意思嗎?當然不是。

如何去應對危機?1.認清自己的優勢和底線,去堅持它;2.認清自己的劣勢與不足,去彌補它去糾正它或者暫時去繞過它。——這才是面對危機時正確的處理方式,而不是一味的頭腦發熱要打要殺以及直接認輸下跪,那都是莽夫和懦夫的行為。

分析形勢有利于認清形勢,認清了形勢可以幫助勇者更好的迎難而上,尋求到務實而有效的突圍方法,而不是盲目的如大煉鋼鐵般的勞民傷財,胡攪蠻干。相信無論革命先烈的長征勝利,還是兩彈一星重大突破,乃至改革開放的巨大成就,這都不是脫離現實,只靠空喊口號,一腔熱血得到的。掩耳盜鈴才是最可恥的認輸。

責任編輯:pj

-

美國

+關注

關注

1文章

394瀏覽量

26124 -

eda

+關注

關注

71文章

2711瀏覽量

172916 -

反向器

+關注

關注

2文章

24瀏覽量

11623 -

華秋DFM

+關注

關注

20文章

3493瀏覽量

4378

發布評論請先 登錄

相關推薦

EDA與傳統設計方法的區別

華大九天亮相第61屆設計自動化大會

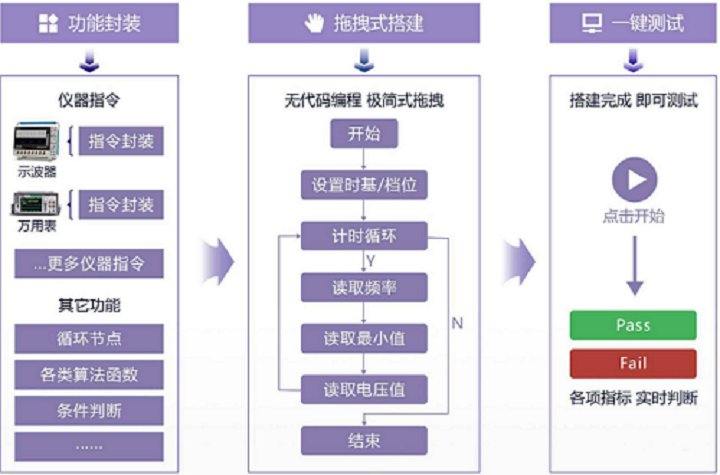

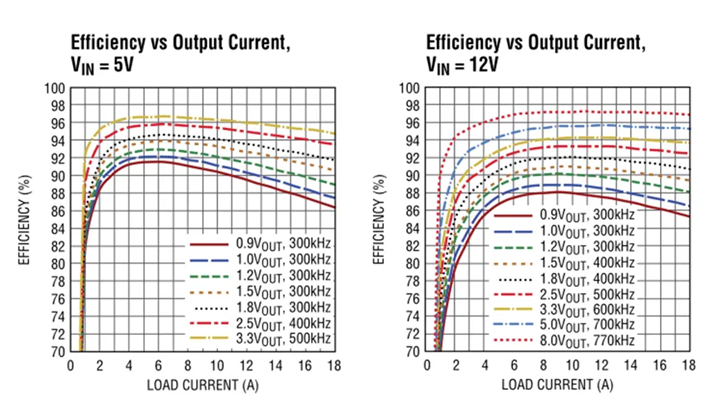

開關電源自動化測試設備:如何實現自動化測試?

機械自動化和電氣自動化區別是什么

機械自動化是自動化的一種嗎

機械制造與自動化是自動化類嗎

工業自動化和自動化區別是什么

軟件接口自動化測試,使用軟件工具+工裝治具測試

納米軟件自動化測試合作:4644芯片與VPX模塊測試

納米軟件分享:電源管理芯片自動化測試方案

工業自動化系統設計

TC397怎么自動化燒錄?

電源測試怎么自動化?電源模塊自動化測試系統如何實現?

LabVIEW與Tektronix示波器實現電源測試自動化

淺析中國工業自動化與智能化應用

為啥必須要使用自動化設計軟件(EDA)?

為啥必須要使用自動化設計軟件(EDA)?

評論