復位電路博大精深,并不是三言兩語就能說清楚的,因此這里也是聊聊復位電路的基礎,更深的研究需要在實際的項目中才能深有體會。本文的主要內容有:

·復位電路概述

·同步復位電路

·異步復位電路

·復位策略——復位網絡

1.復位電路概述

復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。有的電路需要復位信號,就像是有的電路需要時鐘信號那樣,而有的電路是不需要復位信號的。復位又分為同步復位和異步復位,這兩種各有優缺點。下面我們主要來說說復位信號的用途和不需要復位信號的情況。

(1)復位的目的

復位最基本的目的就是使電路(主要是觸發器)進入一個能穩定操作的確定狀態(主要是觸發器在在某個確定的狀態),主要表現為下面兩點:

①使電路在復位后從確定的初始狀態運行:

·上電的時候,為了避免上電后進入隨機狀態而使電路紊亂,這個時候你就需要上電復位了。

·有時候,電路在某個狀態下,你想或者別人要求你從電路的初始狀態開始進行延時你的電路功能,這個時候你就要對你的電路進行復位,讓它從最初的狀態開始運行。

②使電路從錯誤狀態回到可以控制的確定狀態:

有的時候,你的電路發生了異常,比如說狀態機跑飛了、系統供電炸了之類的,總之就是電路運行得不正常了,這個時候你就要對電路進行復位,讓它從錯誤的狀態回到一個正常的狀態。

上面說的都是和實際電路有關的,下面我們就從電路仿真的角度看一下復位信號的重要性。

·仿真的要求

復位信號在仿真里面主要是使電路仿真時具有可知的初始值:

在仿真的時候,信號在初始狀態是未知狀態(也就是所謂的x,不過對信號初始化之后的這種情況除外,因為仿真的時候對信號初始化就使信號有了初始值,這就不是x了)。

對于數據通路(數字系統一般分為數據通路和控制通路,數據通路一般是對輸入的數據進行處理,控制通路則是對運行的情況進行操作),在實際電路中,只要輸入是有效數據(開始的時候可能不是有效的),輸出后的狀態也是確定的;在仿真的時候,也是輸入數據有效了,輸出也就確定了。也就是說,初始不定態對數據通路的影響不明顯。

對于控制通路,在實際電路中,只要控制通路完備(比如說控制通路的狀態機是完備的),即使初始狀態即使是不定態,在經過一定的循環后,還是能回到正確的狀態上;然而在仿真的時候就不行了,仿真的時候由于初始狀態為未知態,控制電路一開始就陷入了未知態;仿真跟實際電路不同,仿真是“串行”的,仿真時控制信號的初始不定態會導致后續的控制信號結果都是不定態,也就是說,初始的不定態對控制通道是致命的。

(2)不需要復位信號的一些情況

復位信號很重要,但是并不是每一部分的電路都需要復位電路,一方面是復位電路也消耗邏輯資源、占用芯片面積,另一方面是復位信號會增加電路設計的復雜性(比如要考慮復位的策略、復位的布局布線等等)。

當某個電路的輸出在任何時刻都可以不受到復位信號的控制就有正確的值時,比如說數據通路中的對數據進行處理的部分。在某些情況下,當流水線的寄存器(移位寄存觸發器)在高速應用中時,應該去掉某些寄存器的復位信號以使設計達到更高的性能,因為帶復位的觸發器比不帶復位的觸發器更復雜,反應也更慢。

對復位信號/電路有一定的概念后,下面我們就來說說復位的方式,也就是同步電路和異步電路以及它們的優缺點。

2.同步復位

(1)同步復位電路

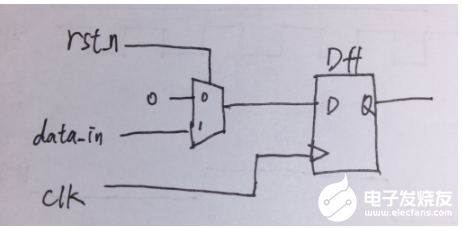

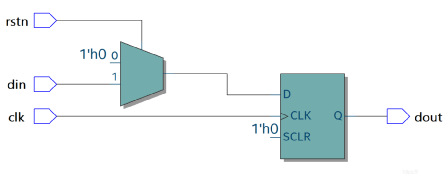

同步復位是指復位信號在時鐘有效沿到來時才復位電路(主要是復位觸發器)。因此同步復位的復位信號受到時鐘信號的控制。同步復位的觸發器RTL代碼和電路如下所示:

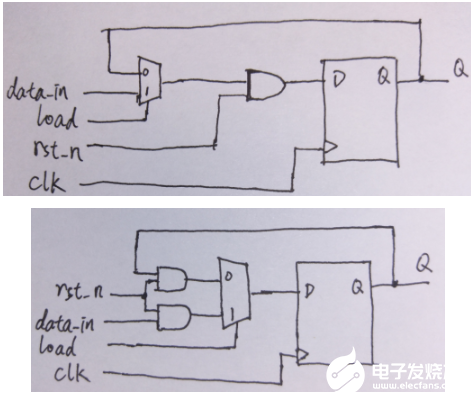

上面的電路在FPGA中容易綜合得到;也有可能綜合得到下面這樣的電路:

(2)同步復位的優點

①首先同步復位一般能確保電路是100%同步的,因為電路都是由同步時鐘觸發。

②同步復位會綜合為更小的觸發器(???更小??感覺有點不太對,可能FPGA跟ASIC不一樣吧?)。從前面電路中我們也可以看到,復位電路僅僅是由一個普通的觸發器和一個與門夠吃。

③由于同步復位僅僅發生在時鐘的有效沿,當外部的復位信號由毛刺時,時鐘可以當做過濾毛刺的手段,也就是說同步復位受到復位信號的毛刺影響小。

④當復位信號是由內部電路產生時,此時復位信號就有可能有毛刺,時鐘就可以過濾毛刺。也就是說,可以在那些使用內部信號當做復位信號的設計中,使用同步復位。

(3)同步復位的缺點

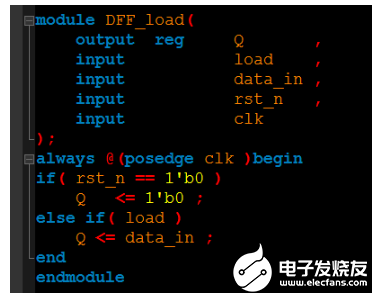

①使用同步復位可能使綜合工具無法分辨分辨復位信號和其他控制信號,導致進行復位的控制邏輯遠離觸發器(也就是說,并不是所以的ASIC庫都有內置的同步復位邏輯,綜合工具可能把符合邏輯綜合到觸發器自身之外)。例如對于帶同步復位和加載使能的觸發器,代碼如下所示:

綜合得到的電路圖如下所示,左邊是理想的電路,右邊是可能綜合出的電路:

這兩個電路的功能完全一樣,只不過右邊電路的復位控制邏輯(即復位與門)在多路復用器之外,也就是遠離了觸發器。這在門級仿真的時候(注意這是仿真),當。..。

解決方法就是:一方面這個只是綜合工具的問題,一般綜合工具會自動識別在敏感列表里面又在條件表達式信號中的第一個信號為復位信號;另一方面,可以在RTL代碼編寫的時候,加入相關的綜合指令,讓綜合的時候把復位邏輯靠近觸發器。

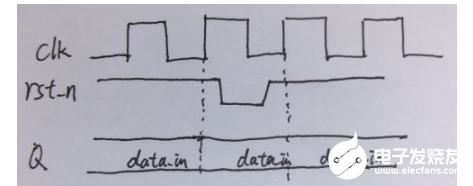

②由于同步復位需要在時鐘沿的觸發下才能起作用,復位信號是以短脈沖的方式出現時,時鐘沿就有可能錯失這個復位信號,導致復位脈沖丟失,同步復位電路沒有起到作用,時序圖如下所示:

解決辦法:一方面,可以采用脈沖捕捉電路,這個電路在我的跨時鐘域控制信號傳輸中有講到。;另一方面,可以將復位信號進行脈沖擴展,維持足夠長的時間,這個可以通過一個小的計數器實現,如下圖所示:

③同步復位可能有組合邏輯延時,當復位邏輯距離觸發器比較遠時,這個時候就不能把觸發器當做即時響應復位信號的觸發器,而是有一定延時的觸發器,這個時候就有了復位信號偏移的問題,關于復位信號偏移的描述,我們將在異步復位中進行描述。

解決方法:使用內置的同步復位觸發器;綜合的時候加入相關的綜合指令,這個和①類似。

④我們前面說過,在由內部組合邏輯的產生復位信號的設計中,推薦使用同步復位。其實這也是有缺點的,這是因為這樣產生復位信號的組合邏輯一方面在仿真的時候容易出現x態,另一方面在實際電路中,這樣的復位信號容易被外部(多個)信號影響。

解決方法:不建議使用內部產生的復位信號;使用異步復位。

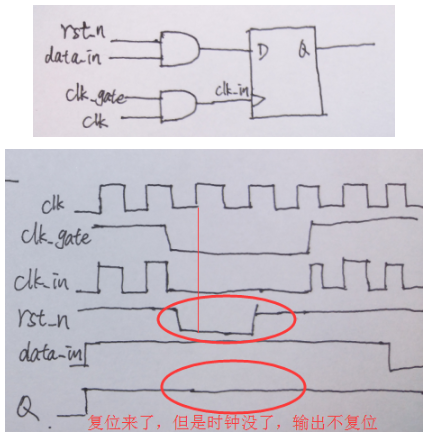

⑤門控時鐘的同步復位可能無效:

使用門控時鐘的時候,由于復位信號依賴于時鐘,在復位信號發出的時候,時鐘可能關閉了,這個時候就會導致實際的電路沒有被復位,如下圖所示:

解決方法:只能使用異步復位,并在時鐘恢復前移除異步復位。

⑥總線設計中的同步復位問題:

在總線控制中,系統上電復位的時候,我們要求不同芯片之間的總線工作在合理的狀態上(比如處于高阻態或者輸出);然而上電之后,由于系統時鐘可能仍未正常工作,上電(同步)復位就可能無效,這個時候各個模塊(芯片)就可能不會把總線接口設置為特定的狀態,(當多個模塊同時輸出數據到總線上時)就可能導致電平沖突,嚴重的話會燒壞接口。

解決辦法:為了防止芯片上電時內部總線出現競爭,有一下兩種解決辦法,一種是采用異步上電復位,如下圖所示:

這個時候使用了異步復位,使能信號oe輸出0,也就是有了初始的狀態

另一種方法是使用復位信號能直接撤銷三態使能的電路,如下所示:

從電路圖中可以看到復位信號一方面控制了復位邏輯,另一方面控制了三態的使能端;這種技術簡化了復位-高阻這個條路徑的時序分析。

3.異步復位

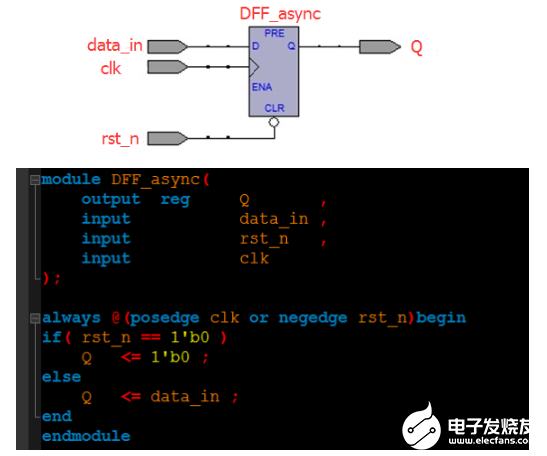

(1)異步復位電路

異步復位觸發器則是在設計觸發器的時候加入了一個復位引腳,也就是說復位邏輯集成在觸發器里面。(一般情況下)低電平的復位信號到達觸發器的復位端時,觸發器進入復位狀態,直到復位信號撤離。帶異步復位的觸發器電路圖和RTL代碼如下所示:

(2)異步復位的優點

①使用異步復位的最大好處就是復位路徑上沒有延時,如上面的圖所示,復位信號一直連接到觸發器的復位端口,而不是像同步復位那樣需要經過一個復位控制邏輯(如與門)。這樣子就減少了外界信號的影響。

②與時鐘沒有關系,不管時鐘上升沿有沒有到來,只要復位信號一有效,觸發器就會復位,也就是基本上做到實時性;由于與時鐘沒有關系,因此也可以用在門控時鐘里面。

③綜合工具能自動推斷出異步復位而不必加入任何綜合指令。

(3)異步復位的缺點

①復位撤離問題

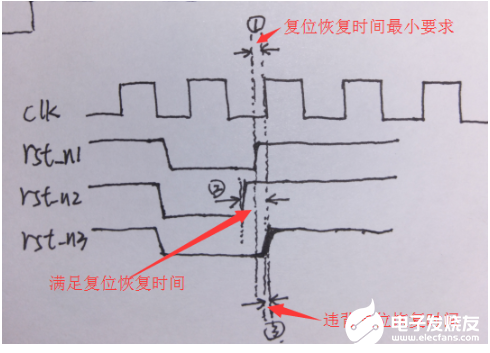

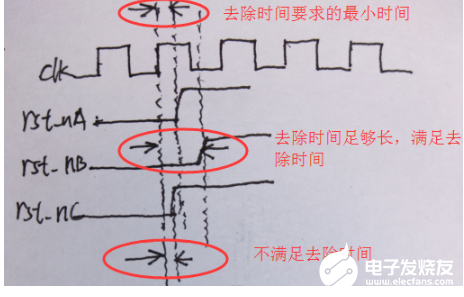

在介紹復位撤離問題之前,先說一下復位恢復時間和去除時間。所謂的復位恢復時間是指撤離一個復位信號時,復位信號從有效跳變為無效的時刻 與 下一個有效時鐘沿 之間的這段時間;去除時間是指撤離一個復位信號時,復位信號從有效跳變為無效的時刻 與 上一個有效時鐘沿 之間的這段時間(可以類比于觸發器的建立時間和保持時間)。如下圖所示:

上圖中,rst_n1是要求的復位恢復時間,rst_n2滿足復位恢復時間,rst_n3復位恢復時間不足。

上圖中,rst_nA是要求的復位去除時間,rst_n2滿足復位去除時間,rst_n3復位去除時間不足。

從上面的兩個圖中可以知道,如果你想讓某個時鐘沿起作用(也就是采數據),那么你就應該在“恢復時間”之前讓異步控制信號變無效;如果你想讓某個時鐘沿不起作用(也就是在這個時鐘沿依舊復位),那么你就應該在“去除時間”過后使控制信號變無效。異步復位信號的恢復和去除時間需要大于一定的時間,如果你的異步復位信號在這兩種情況之間(撤離),那么就沒法確定時鐘沿是否起作用了,即判斷不出是復位還是不復位(不復位即是D觸發器才輸入端的數據)。

介紹了復位恢復時間和去除時間之后,我們就可以看看異步復位信號的問題了。由于異步復位信號與系統時鐘毫無關系,復位可以在隨時施加,也可以隨時撤離。在施加的時候復位信號的時候,不存在任何問題,因為這跟復位恢復時間扯不上關系。但是,在撤離復位信號的情況下就有問題了,主要有兩個問題:

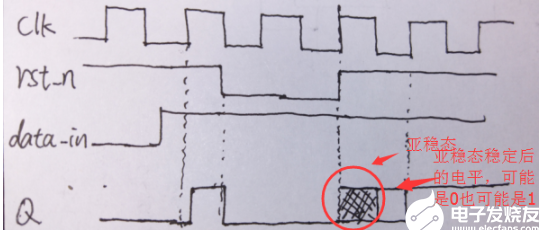

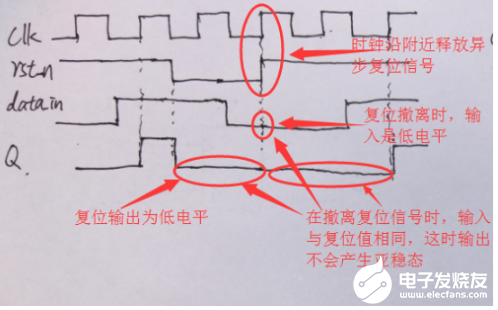

·當異步復位信號的撤離時刻在時鐘有有效沿附近時,就可能導致恢復時間或去除時間不足,即這個時候違背了復位恢復時間或去除時間,這時就可能導致觸發器的輸出端為亞穩態(注意是可能),如下所示:

但是并不是所有情況都會產生亞穩態,當復位值和此時的的輸出相同時,就不會產生亞穩態,如下圖所示:

這是因為:復位信號翻轉的時候,如果復位信號判斷是低電平,輸出就復位即一定是低電平;如果判斷復位信號是高電平,輸出信號就等于對輸入信號的采樣值。圖里面輸入信號就是低電平,不管你是復位還是不復位,輸出一直是低電平,沒有亞穩態。

·復位狀態不一致的問題:

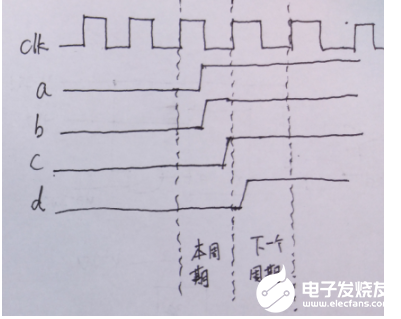

復位信號很時鐘信號一樣,復位通過復位網絡到達各個觸發器。一方面,復位網絡具有非常大的扇出和負載,到達不同的觸發器存在不同的延時,也就是存在復位偏移,因此撤離異步復位的時刻也是不一樣的;另一方面,由于時鐘網絡也存在時鐘偏移。這個時候異步復位信號就有可能在不同的觸發器的不同時鐘周期內進行撤離,也就是說異步復位的信號不一致,如下圖所示:

異步復位信號a是異步復位信號源,異步復位信號b、c、d是到達觸發器的異步信號。我們可以看到,b信號是在本周期就撤離了復位;c信號則由于復位恢復時間不滿足,則可能導致觸發器輸出亞穩態;而d信號則由于延時太長(但是滿足了復位去除時間),在下一個周期才撤離復位。

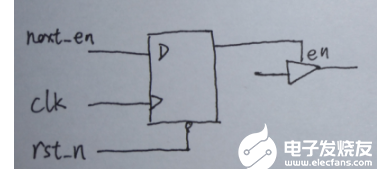

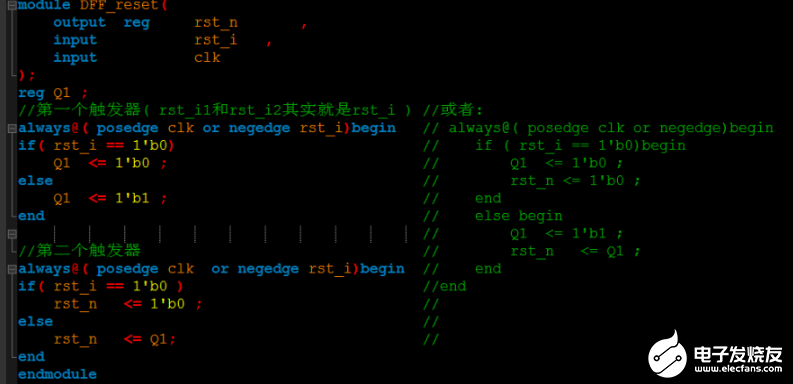

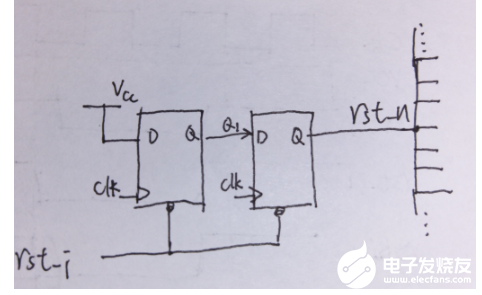

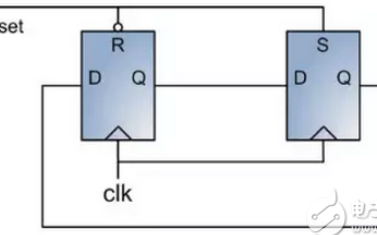

撤離問題的解決方法:異步復位的同步釋放

異步復位的同步釋放電路也稱為復位同步器,這個方法是將外部輸入的異步復位信號進行處理,產生另外一個適合用于后面電路的復位信號,這個處理后的復位信號能夠異步復位電路中的觸發器,又不會存在撤離問題(因為經過了同步);這個異步復位同步釋放的處理電路和RTL代碼如下所示:

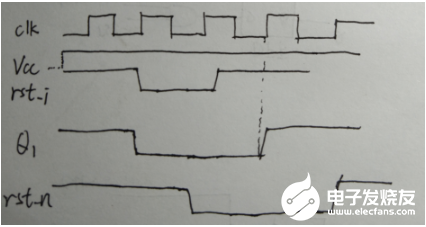

從圖中可以看到,這是用外部異步復位信號來復位一對觸發器,這對觸發器異步地驅動主復位信號,也就是這對觸發器產生電路需要的復位信號,這些復位信號再到達各個觸發器,然后進行復位,理想的異步復位同步釋放的時序如下所示:

上圖中,在理想的情況下,復位信號在兩級D觸發器上面的撤離時間可能不一樣,這個和復位信號傳輸到的觸發器位置和觸發器的時鐘沿有關。理想情況下的復位信號傳輸到目標觸發器都能夠同時撤離,并且不在時鐘有效沿附近。

實際情況一般不是那么理想的,當不是理想的情況下,也就是說復位信號到達目標寄存器存在時鐘偏移,并且復位信號有可能在時鐘有效沿附近撤離,這個時候復位器出現的問題就有三種:第一級OK,第二級出現問題;第一級出現問題,第二級OK;兩級都出現問題。下面我們就來看看這三種情況下產生的復位信號是什么情況:

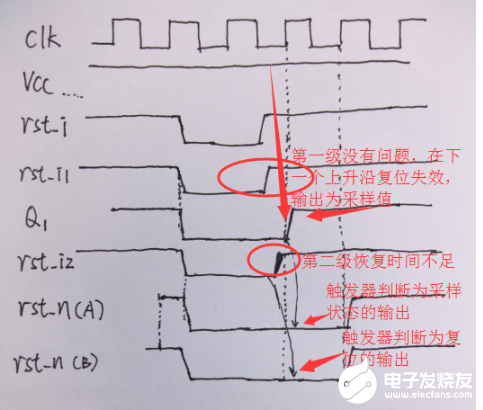

第一級的撤離沒有問題,第二級的撤離出現在時鐘的有效沿附近,也就是說第二級的D觸發器的撤離時間不滿足復位恢復時間或者去除時間,這時候的時序圖如下所示:

我們可以看到無論是觸發器判斷此刻是復位還是不復位,輸出都是一樣的,也就是說,輸出rst_n不是亞穩態,而是確定的值。

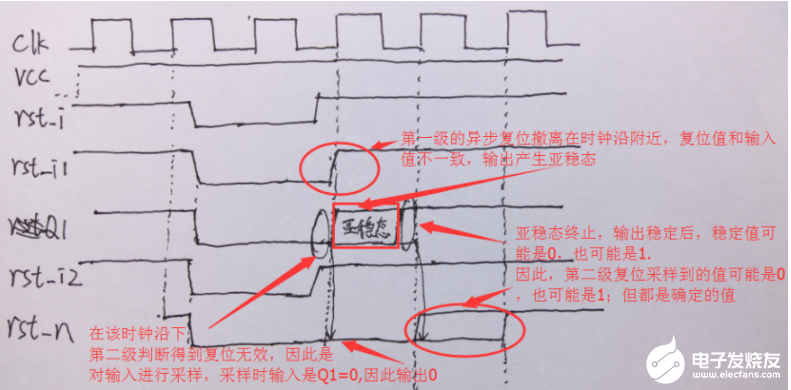

第一級的撤離出現問題,第二級的撤離沒有問題,這時候的時序圖如下所示:

我們可以看到,第一級觸發器雖然產生了亞穩態,但是由于第二級觸發器的存在,亞穩態并沒有傳播下去,得到的復位信號依然是干凈的,只不過這個復位信號可能延長多一個周期而已(這是因為亞穩態穩定后的可能態引起的)。

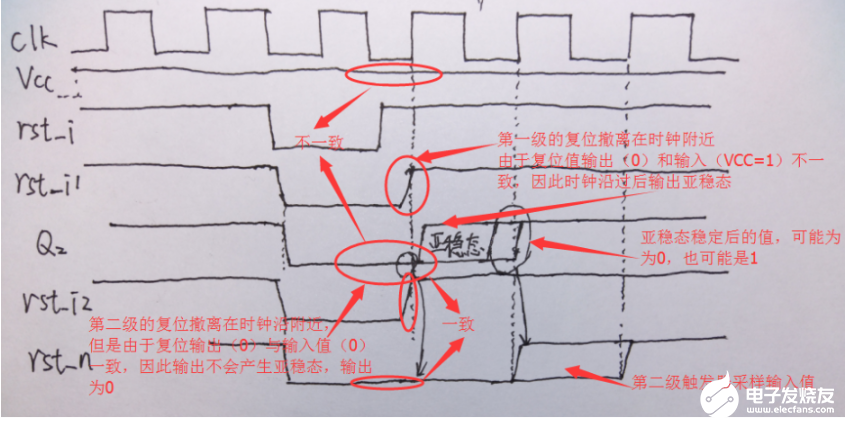

最極端的一種情況是,兩級的撤離都不滿足復位恢復時間或者去除時間,這時候的時序圖如下所示:

我們可以看到第一級觸發器產生了亞穩態,但是由于第二級觸發器的存在,亞穩態沒有傳播下去;雖然第二級觸發器的復位信號撤離也在時鐘有效沿附近,但是跟第一種情況一樣,第二級觸發器是不會產生亞穩態的。因此即使是極端狀態,輸出的復位信號也是干凈的。

由此我們可以看到,異步復位的同步撤離能夠有效地解決撤離導致的復位恢復時間或者去除時間不足的問題,同時把復位信號同步化,解決了復位撤離偏移的問題。

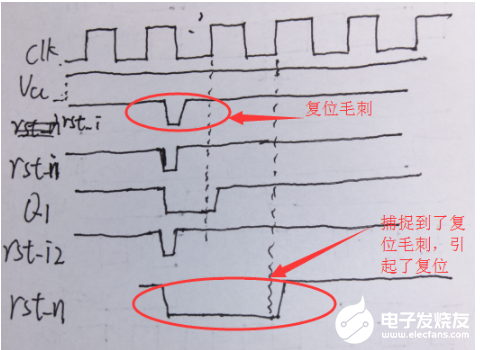

②異步復位的抖動問題

當外部輸入的異步復位信號產生毛刺時,任何滿足觸發器最小復位脈沖寬度的輸入都有可能引起觸發器復位,這問題是源頭上的問題,即使是使用上面的同步器,也還是有同樣的敏感問題,時序圖如下所示:

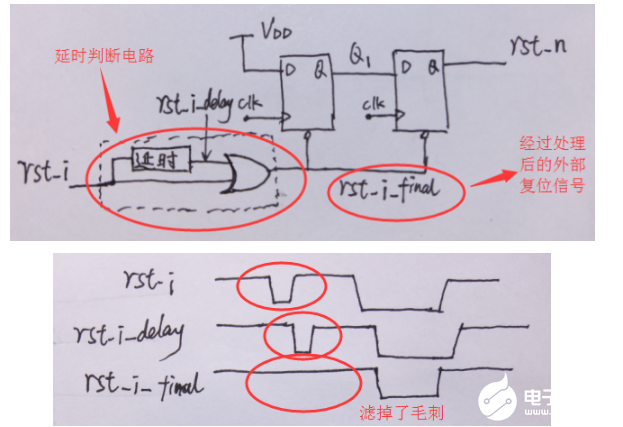

解決方法:一個是使用同步復位,另一個就是過濾毛刺了,過濾毛刺和消抖的思路有點像,主要就是經過一段延時之后,在經過邏輯門判斷產生外部來的是不是真正復位信號,加上過濾毛刺信號部分的同步撤離電路和時序如下所示:

在上圖中,我們可以看到,抖動問題得到了解決。然而這種方法還是有缺點的,主要就是這個延時電路的延時控制可能隨著環境而變化,而且延時的時間要合適長才行,絕對不能太短。

③DFT的問題

在DFT的時候,如果異步復位信號不能直接被I/O引腳驅動,就必須將異步復位線和后面的的被驅動電路斷開,用來保證DFT掃描和測試能夠正確進行。總之異步復位增加了DFT的復雜性。

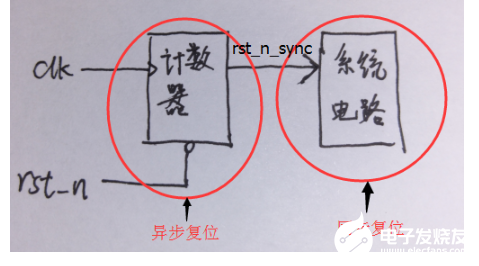

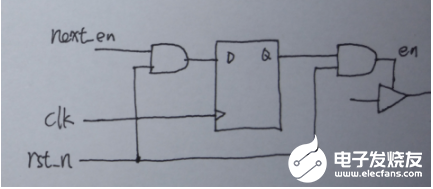

4.復位策略——復位網絡

在數字電路里面,復位信號驅動了很多觸發器,僅次于時鐘,因此復位也往往形成或者使用復位網絡。復位網絡的設計也是有值得斟酌的地方,例如,由于復位的扇出太大,全部的復位不能僅僅由一個端口驅動,也就是不能像下面一樣:

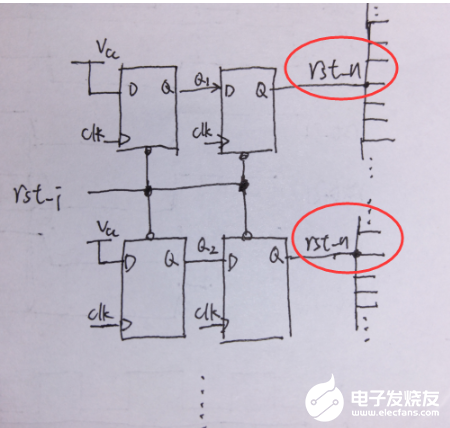

既然上面的不行,那就改成下面的唄,也就是使用多各“并聯”的同步釋放,分擔一下負載壓力:

然而這種方案還是有問題的,這是第一級的撤離出現問題,第二級的撤離沒有問題的時候,亞穩態穩定后的狀態可能不一樣,導致rst_n的復位不一致,有的復位可能會快/慢一個周期。

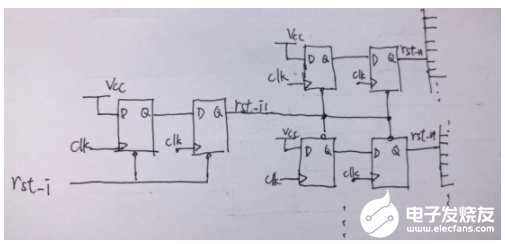

最后的方案是,先進行同步釋放之后,同步后的復位信號又當做各個部分的異步信號,然后進行同步釋放,如下所示:

這樣先經過前級的同步釋放之后,就不存在亞穩態穩定好導致的輸出rst_n不一致的問題了。

最后說一下多時鐘域的復位:在多時鐘域復位中,外部的異步復位信號的同步釋放應該各自的時鐘進行同步,比如異步FIFO中,寫時鐘域就用寫時鐘進行同步釋放;讀時鐘域就用讀時鐘進行同步釋放。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601809 -

電路設計

+關注

關注

6665文章

2426瀏覽量

203300 -

D觸發器

+關注

關注

3文章

164瀏覽量

47862 -

復位電路

+關注

關注

13文章

322瀏覽量

44536 -

復位信號

+關注

關注

0文章

53瀏覽量

6299

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

Xilinx FPGA的同步復位和異步復位

復位電路的同步復位和異步復位講解

同步復位電路和異步復位電路區別分析

同步復位電路和異步復位電路區別分析

評論