EDA 是芯片之母是IC 設計最上游、最高端的產業。也是中國集成電路產業最薄弱的環節。為向集成電路專業師生和從業者中系統介紹EDA技術的前沿進展,芯人類將分多期全文引入《電子報》EDA前沿技術專欄。專欄特邀行業多位專家,全面系統地介紹國內外EDA 的狀況和國產EDA 的發展。本文為電子報授權發表。包含混合SOC的設計,驗證和實現的方法流程三方面內容,并重點介紹了驗證所需要了解的仿真器原理,和行為級建模相關的知識。共分三次發表。

Table Model

有點類似于大數據的概念。既然傳統的Model和硅工藝聯系不怎么緊了,那么直接把Silicon測試出來的數據都列舉出來,建立一個數據庫(溫度、電壓和Silicon數值)表格,仿真器用的時候直接查表就行了。你只要關心輸入什么值,能輸出來什么值就行了,一表在手,有input有output。

放棄對因果關系的過分渴求,取而代之去關注“相關關系”,只是根據實際測試到的silicon的數值,直接做一個數據庫,當外界加什么電壓、有什么溫度時候,就來什么對應的輸出電流等。這就類似于大數據的概念,不關心為什么,只在乎是什么。對于不在table里面的數據,仿真器需要插入數值(interpolate)或者外推推斷數值(extrapolate)。短板是離散數據的連續性和光滑性差,需要Analog仿真器做些處理。

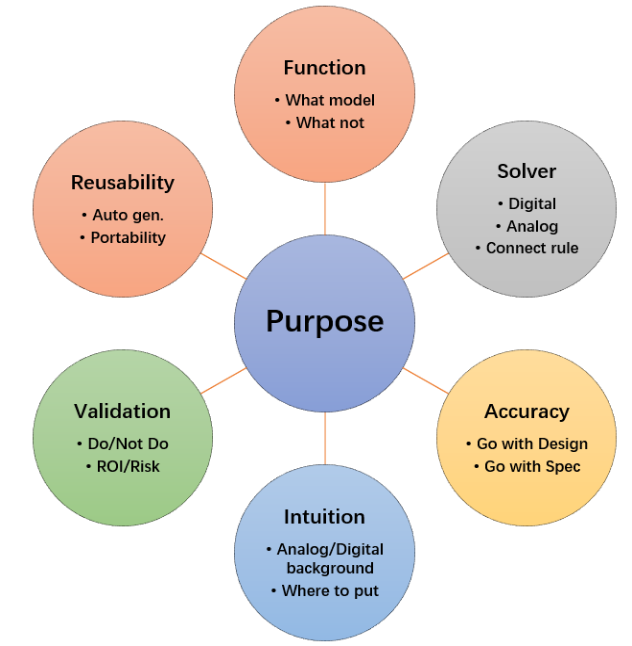

建模前要plan!Plan!plan!

在做Model之前,一定要想清楚做Model的目的是什么。

建模需要考慮的因素

Model是否需要統一的規范?因為驗證本身希望能夠Reuse。但是一旦想統一規范,可能就需要花費更長的時間和精力,項目是否有時間/值得付出不?哪些Model不要是需要放棄建模的?例如對于非線性(Non-linear)的因素, 是否可以轉化為線性。對于弱相關因子(weak dependencies)是否可以忽略;如果進入一個Model的input control/signal不符合Model里面的預期,需要有Assertion來要報錯。

Model到底是讓Analog Background的人來寫?還是Digital的工程師?放在電路的哪個層級?

對于Model要不要做Validation?怎么做Validation?對Model的驗證,包括利用相同的Test Bench,對于Model和Schematic出來的結果的驗證。驗證Model和電路類似,有Block級Schematic和Model的吻合,還有Sub-System能夠能通暢的利用Model仿真、以及Model和Sub-System的吻合,更有Model和整個Top的吻合度。為了提高項目效率,是不是可以跳過某些層級?

總之就是做Model也是一門藝術,需要在服務其目的的情況下,做各種trade off。

與Model相關的工具

SMG-1

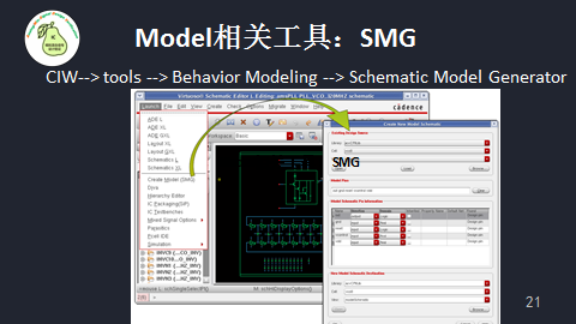

A、SMG

Schematic Model Generator的工具在Virtuoso里面,只要用圖形的界面填寫一下pin的性質,IO代碼就自動生成。

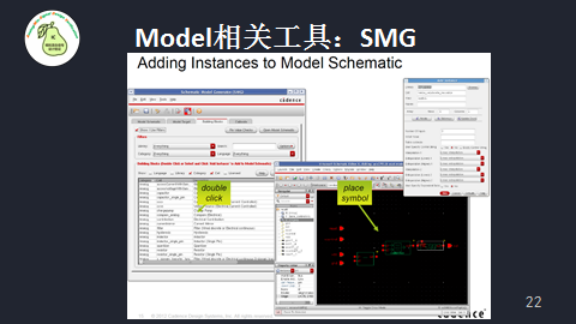

SMG-2

很多內置的小模塊BBT(Building Block Text),提供了例示的code,你根據自己的schematic,去搭建設計。

在Model自動化的道路上,設計者和EDA工具開發者需要進一步努力,例如電路設計時候的合理Partition,和考慮標準化Model的電路分層等。

SMG-3

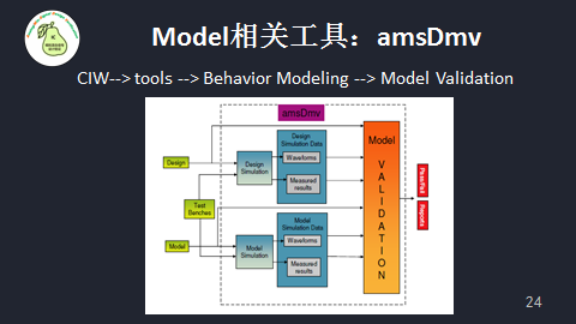

B、amsDmv

Model要和Schematic吻合,amsDmv(AMS Design and Model Validation)提供Model的驗證功能。

amsDmv

它利用ADE的結果按一定的誤差精度(Tolerance),對比schematic和Model仿真的波形,也可以做最基本的Pin check,以及設置不需要對比的參數(exclude)等信息。

C、Xmodel

有一個xmodel的工具,集成于Cadence Virtuoso環境,有Python和Skill的接口,也是方便做Model的小工具,生成SV語言的Model。

數模混合芯片的物理實現

物理實現將電路轉換成芯片物理版圖,稱之為Tape Out(TO)。數字設計把相同的節距和高度標準單元,通過綜合工具得到門級網表,再通過自動布局布線工具(P&R)實現版圖。模擬設計將自動生成的參數化的MOS管搭建Pcell。Pcell搭建模塊,模塊組成定制單元模塊,自動鄰接、器件走線、虛擬單元并插入阱單元。模擬版圖一般是定制的。

對于復雜的數模混合SOC,芯片布局至關重要。在物理實現的初始要自上而下的大局觀,定制單元和數字單元同時考慮。自上而下設計中,各模塊的面積和擺放位置需要預估,信號流方向和電源布線需要考慮,端口需要優化。在自下而上的Layout中,首先實現包括電阻電容和MOS管的基本器件的版圖,然后在考慮其擺放和連線,從而形成一個版圖單元;再與其他模塊聯合。對于低功耗設計,由于輸入電源數目不斷增加,所以需要自上而下設計。對于較小設計或者可以復用的AMS IP,一般用自下而上的流程。當然目前越來越多的在混合使用兩種流程。版圖的IP包括硬模塊和軟模塊兩類。

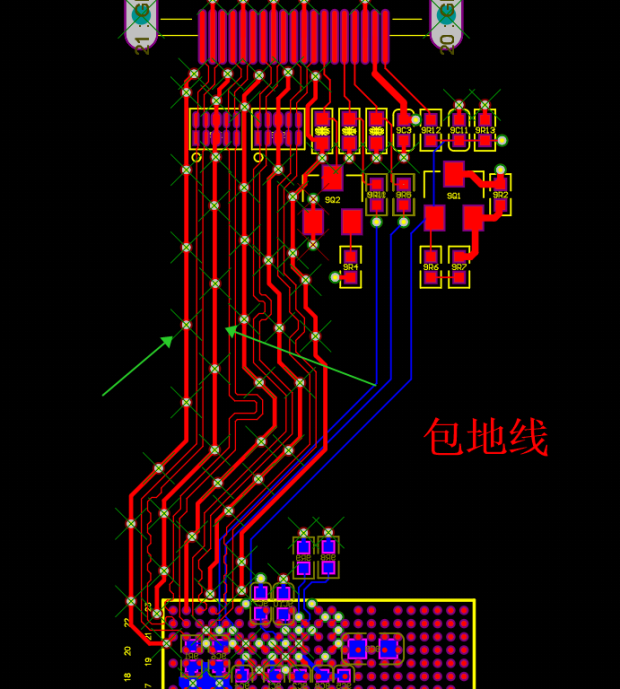

基于約束(Constraints)的方法學,正在用于模擬和數字物理實現。約束可以捕捉設計者的意圖,并將其傳遞給掩模版工程師,從而知道和驗證版圖是否和符合要求。常見模擬約束有:匹配器件,敏感信號的標記和處理,高電壓或高功耗信號,保護環和其他隔離結構。數字IC中,設計定義時序約束,從而進行門級網表綜合。布線結束后,會抽取線上寄生,進行靜態時序分析STA,來檢查物理實現是否符合要求。

物理實現之后,需要進行后仿真。模擬IC常見的抽取方法有只提取電容C,只提取電阻R,電阻電容都提取(RC),電阻電容電感(RCL)提取。數字IC,將線延遲轉換到標準延遲格式(Standard Delay Format)SDF當中,從而進行后仿真,獲知寄生對電路性能的影響。

到真正流片之前,還要做設計規則檢查DRC(Design Rule Check);電學規則檢查ERC(Electrical Rule Check);版圖對照電路檢查LVS(Layout Versus Schematic)來保證版圖符合電路的連接關系;和針對制造的設計檢查DFM(Design For Manufacture)來發現影響制造質量與良率的因素。

電學特性感知設計(Electrically Aware Design)EAD代表了范式轉移的方法,將電學特性分析和驗證前饋到設計過程中。

例如,考慮先進工藝引入的鄰阱效應(Well Proximity Effect, WPE);淺溝隔離效應(Shallow Trench Isolation, STI),和電遷移效應。為數模混合驗證提供電學特性感知設計的解決方案以及方法學的優化將是一場持久戰。

作者簡介

邵亞利,模擬混合信號設計驗證專家。浙江大學本碩,“模擬混合信號設計驗證”公眾號(yaliDV)創始人。曾就職于德州儀器(TI),現就職于亞德諾(ADI)半導體公司。ADI(Analog Devices) 是全球領先的高性能模擬技術公司,憑借杰出的檢測、測量、電源、連接和解譯技術,搭建連接現實模擬世界和數字世界的智能化橋梁。

責任編輯:pj

-

芯片

+關注

關注

454文章

50460瀏覽量

421980 -

電路

+關注

關注

172文章

5852瀏覽量

171945 -

Model

+關注

關注

0文章

338瀏覽量

25041

發布評論請先 登錄

相關推薦

IBIS文件中的Series Model簡介及設計仿真實例

鴻蒙生態發布統一互聯技術標準

LMK04832配置時鐘輸出時,IDL和ODL怎么配置?有沒有統一的做法?

知識分享 | 建模規范:建立優質模型的關鍵

統一多云管理平臺怎么用?

請問Scene Server Model的state值應該怎樣設置?

龍芯CPU統一系統架構規范及參考設計下載

OpenHarmony設備統一互聯技術規范發布

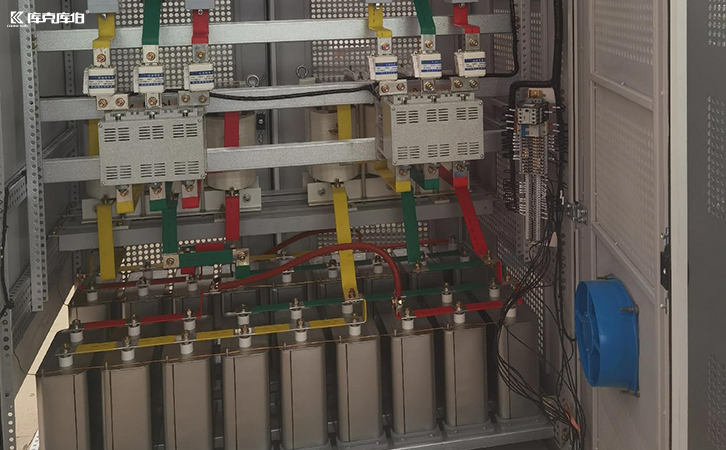

電容器缺相后是否需要立即斷開

Model是否需要統一的規范?

Model是否需要統一的規范?

評論