隨著三星Exynos 990和麒麟990移動平臺的問世,一種名為“7nm+EUV”的全新工藝登上了歷史舞臺。

與此同時,F(xiàn)inFET晶體管技術(shù)也已有望被GAAFET所取代,未來的SoC芯片將因這兩種新技術(shù)而出現(xiàn)翻天覆地的變化。

摩爾定律遇阻

自1965年英特爾創(chuàng)始人之一的戈登·摩爾提出摩爾定律以來,半導體領(lǐng)域就一直在遵循著“當價格不變時,集成電路上可容納的元器件的數(shù)目,約每隔18個~24個月便會增加一倍,性能也將提升一倍”這個規(guī)律前行。

然而,摩爾定律引領(lǐng)的工藝革新節(jié)奏在2013年便出現(xiàn)了放緩的現(xiàn)象,這一點從英特爾14nm制程工藝從2015年誕生并將沿用到2020年就很能說明問題。

看到這里,不少用戶可能會產(chǎn)生疑問:摩爾定律失效就失效唄,反正以現(xiàn)有工藝生產(chǎn)的芯片也不是不能用。

工藝升級的必要性

處理器、內(nèi)存、閃存、各種電源管理和控制類的芯片,都是摩爾定律的受益者。

以處理器為例,其主要構(gòu)成就是晶體管,晶體管數(shù)量越多性能越強,而更先進的制程工藝意味著在有限的面積內(nèi)可以塞進更多的晶體管。

此外,制程工藝的升級,還能降低功耗,并在提升性能的同時大幅縮小芯片的封裝面積。

還是以英特爾為例,其在45nm時期封裝面積為100平方毫米的處理器芯片,32nm工藝時期就可將芯片面積縮小到62平方毫米,在22nm、14nm和10nm上更是能進一步壓縮到38.4平方毫米、17.7平方毫米和7.6平方毫米。

以此同時,在最新10nm工藝節(jié)點上,每平方毫米的晶體管數(shù)量也能超過1億個!

如今無論是PC還是手機都在堅持“瘦身”,更小封裝面積的芯片,可以讓這些電子設(shè)備變得更輕更薄,還能大幅降低生產(chǎn)芯片的成本——在一張晶圓上可以切割出更多的芯片。

請不小小看這個變化,生產(chǎn)芯片的重要原料是從沙子中提取的硅,而符合半導體工業(yè)要求的沙子也并非沙漠、海灘中隨處可見的細沙,而是需要直徑足夠大的“砂礫”。

前不久網(wǎng)上流傳的“造芯片的沙子不夠用”的文章就已經(jīng)指出,隨著建筑工業(yè)用砂資源的緊缺,相關(guān)產(chǎn)業(yè)的成本將面臨極大的壓力。

在這個大環(huán)境下,生產(chǎn)工藝的革新恰好可以對沖生產(chǎn)原料緊張的風險,摩爾定律“重啟”的重要性不言而喻。

那么,如何才能讓摩爾定律重回正軌?除了砷化銦鎵(InGaAs)及磷化銦(InP)等三五族半導體材料以外,EUV和GAAFET技術(shù)就是最近幾年內(nèi)最為關(guān)鍵的核心技術(shù)。

淺析EUV光刻機

在芯片制造業(yè)中,“光刻機”是科技含量最高,也是最為核心的設(shè)備之一,它涉及到系統(tǒng)集成、精密光學、精密運動、精密物料傳輸、高精度微環(huán)境控制等多項先進技術(shù)。

光刻機的原理

光刻機的工作原理是把芯片的電路設(shè)計圖案縮小后,以納米級別的精度,通過一系列的光源能量、形狀控制手段,將光束透射過畫著線路圖的掩模,映射并蝕刻到半導體材料(晶圓硅片)上,然后再使用化學方法顯影,最終得到刻在硅片上的電路圖。

我們可以將這個過程理解為傳統(tǒng)的膠片相機,讓光線通過鏡頭投射到膠卷實現(xiàn)曝光,再經(jīng)過顯影液浸泡得到清晰的,還原了鏡頭前景色的照片。只是,光刻機鏡頭前的景色變成了芯片電路設(shè)計圖,而最終“洗”出來的照片,則是硅晶片成品。

總之,光刻機就是使用光線蝕刻的方式制造芯片,所謂的更先進工藝(如7nm相較與10nm),就是需要在晶圓硅片上蝕刻出更精細(降低晶體管間距)的電路,此時光源將扮演至關(guān)重要的角色。

光源的意義

歷史上,光刻機曾使用過采用汞燈產(chǎn)生的436nm和365nm波長的光作為蝕刻光源,用于生產(chǎn)0.8μm~0.35μm(微米,注意不是納米,1微米=1000納米)的芯片。

隨后,光刻機進入了193nm波長的準分子激光時代,可以生產(chǎn)7nm以上制程工藝的芯片。目前主流的光刻設(shè)備都采用了DUV(深紫外光刻,包含ArF和KrF光源)技術(shù),也就是我們熟悉的DUV光刻機。

問題來了,由于DUV光刻機使用光源的波長較長,需要多重光罩/曝光才能實現(xiàn)7nm制程(造成成本上升及生產(chǎn)周期延長),而且更小的晶體管間距也將面臨一定的漏電問題,無法完美發(fā)揮出7nm工藝應(yīng)有的電氣性能。

臺積電第一代7nm工藝(驍龍855、麒麟980)本質(zhì)上就屬于7nm+DUV工藝,屬于7nm時代的“半成品”。當然,7nm+DUV的性能也足以完勝臺積電和三星早期的10nm,只是不夠完美而已。

DUV光刻機生產(chǎn)7nm就已經(jīng)達到極限,自然沒法滿足下一代5nm制程工藝的需要。如果不想辦法加以解決,摩爾定律在7nm→5nm節(jié)點的升級中又將遭遇延期。

EUV光刻機顯威

EUV(極紫外光刻)技術(shù)就是為了解決上述問題而誕生的,它采用了波長為13.5nm的極紫外光,波長僅有DUV光刻設(shè)備193nm光源的1/15,能夠在硅晶片上刻下更小的溝道,只需1次光罩/曝光就能搞定最新的7nm制程,大幅降低了生產(chǎn)成本和生產(chǎn)周期。

目前,臺積電和三星都已經(jīng)實現(xiàn)了7nm+EUV制程工藝的量產(chǎn),并分別用在了麒麟990 5G版和Exynos 9825/990身上。以麒麟990 5G版為例,它在7nm+EUV的加持下首次在移動SoC身上實現(xiàn)了集成多達103億個晶體管的歷史性突破,但其芯片面積卻僅與上代麒麟980基本持平,板級面積還縮小了36%。

可以說,當光刻機進入EUV時代后,有望重新解鎖摩爾定律,讓5nm和3nm走上既定的軌道。

EUV光刻機的局限性

極紫外光刻技術(shù)概念早在上世紀九十年代就已經(jīng)出現(xiàn),來自荷蘭的ASML公司于1999年就展開了EUV光刻機的研發(fā),但直到2016年才實現(xiàn)對下游客戶的供貨,而EUV光刻機被用于生產(chǎn)我們常見的7nm制程的處理器則被進一步拖延到了2019年。

導致EUV光刻機商業(yè)化延誤的原因有很多,比如成本太高——最先進的EUV光刻機售價高達1億美元一臺,是DUV光刻機價格2倍多,采購以后還需要多臺747飛機才能運輸整套系統(tǒng)。

此外,EUV光刻機必須在超潔凈環(huán)境中才能運行,一小點灰塵落到光罩上就會帶來嚴重的良品率問題,并對材料技術(shù)、流程控制、缺陷檢驗等環(huán)節(jié)都提出了更高的要求。

最關(guān)鍵的是,EUV光刻機還極度耗電,它需要消耗電力把整個環(huán)境都抽成真空(避免灰塵),通過更高的功率也彌補自身能源轉(zhuǎn)換效率低下的問題,設(shè)備運行后每小時就需要耗費至少150度的電力。

當然,這些都不是咱們消費者需要考慮的問題,我們只需知道,只有引入EUV技術(shù)的7nm才是真正的7nm,而這項技術(shù)也將伴隨未來的5nm和3nm一路前行。

換句話說,未來在購買電子設(shè)備時,采用EUV技術(shù)生產(chǎn)的CPU等芯片會更具競爭力。

淺析GAAFET技術(shù)

英特爾自22nm,三星和臺積電分別從14nm和16nm制程節(jié)點時期引入了FinFET立體晶體管技術(shù),為更先進的芯片設(shè)計奠定了基礎(chǔ)。

然而,當制程工藝跨過7nm進入5nm制程節(jié)點后,F(xiàn)inFET也將遭遇物理極限,此時只有GAAFET技術(shù)的引入才能讓摩爾定律繼續(xù)前行。

FinFET成就3D晶體管

芯片內(nèi)部是由無數(shù)晶體管組成,在單位面積里晶體管數(shù)量越多性能越強,前文我們提到的DUV和EUV光刻機,其意義就是在單位面積中進一步縮短晶體管間距,增加晶體管密度(數(shù)量)。

但是,晶體管密度越高,漏電問題越嚴重,造成芯片發(fā)熱增加和性能下降。

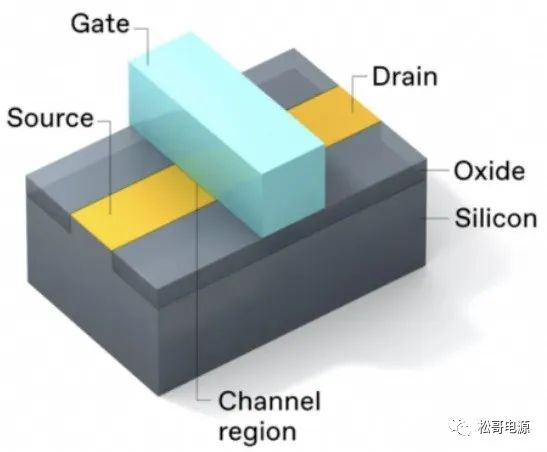

在2011年以前,傳統(tǒng)晶體管結(jié)構(gòu)都是平面的,只能在閘門的一側(cè)控制電路的接通與斷開。

為了解決漏電問題,英特爾在22nm處理器時期帶來了FinFET(鰭式場效應(yīng)晶體管)架構(gòu),這種晶體管的特色是將傳統(tǒng)平面、越來越薄的絕緣層改變?yōu)榱Ⅲw的狀態(tài),閘門被設(shè)計成類似魚鰭的叉狀3D架構(gòu),可于電路的兩側(cè)控制電路的接通與斷開,通過大幅度提升源極和柵極的接觸面積,使得晶體管在控制漏電電流方面得到改善。

需要注意的是,都是FinFET,背后的技術(shù)原理和實際性能也可能存在較大的差異。

比如英特爾在最新10nm工藝上帶來了第三代FinFET立體晶體管技術(shù),晶體管密度達到了每平方毫米1.008億個,遠遠高于三星10nm工藝的晶體管密度(約5510萬個),甚至可以媲美三星和臺積電的7nm工藝,并在最小柵極間距和最小金屬間距方面也有著巨大的優(yōu)勢。

GAAFET為未來掃清障礙

目前我們所看到的所有小于16nm工藝的芯片都采用了FinFET立體晶體管,但就好像DUV光刻機一樣,F(xiàn)inFET雖然可以勉強達到設(shè)計和生產(chǎn)5nm制程工藝的最低要求,但要想100%發(fā)揮5nm的全部潛力,漏電問題依舊是無法繞過的檻。

好消息是,主流芯片廠商都已經(jīng)為此做好了準備,并提出了名為“GAAFET”(Gate-All-Around,環(huán)繞式柵極技術(shù))的橫向晶體管技術(shù)。

和FinFET相比,GAAFET實現(xiàn)了柵極對溝道的四面包裹,利用線狀或者平板狀、片狀等多個源極和漏極橫向垂直于柵極分布。

從物理結(jié)構(gòu)來看,GAAFET是一種比FinFET更加立體和復雜的3D晶體管。

需要注意的是,三星在GAAFET的基礎(chǔ)上還提出了變體的“MBCFET(多橋通道FET)”專利技術(shù),它使用通道結(jié)構(gòu)來排列nm片,增加了柵極和溝道之間的接觸面積,并實現(xiàn)了電流的增加。

目前,英特爾、三星和臺積電都已經(jīng)對GAAFET技術(shù)開始試產(chǎn),而它的首次商業(yè)化亮相應(yīng)該就在不遠的5nm時代,而GAAFET能否成為更先進工藝的最佳搭檔,還得等時間來驗證。

總之,當摩爾定律遇到22nm以下的制程工藝節(jié)點后可謂寸步難行,很多常見的物理定律都會失去作用。為了解決微縮尺度所帶來的各種不確定性,我們看到了High-K、特種金屬、SOI、FinFET、EUV和GAAFET在內(nèi)的各種增強技術(shù)。

作為普通用戶,站在最佳消費體驗的角度來看,我們自然是希望摩爾定律永遠有效,讓我們新買的各種電子設(shè)備不斷變強。但是,與此同時,我們也應(yīng)該感謝為了維系這個定律繼續(xù)前行的科研工作者們。

-

集成電路

+關(guān)注

關(guān)注

5382文章

11396瀏覽量

360953 -

摩爾定律

+關(guān)注

關(guān)注

4文章

632瀏覽量

78938 -

SoC芯片

+關(guān)注

關(guān)注

1文章

608瀏覽量

34875

發(fā)布評論請先 登錄

相關(guān)推薦

解讀UL認證:了解440V變220V單相UL變壓器出口的必要性

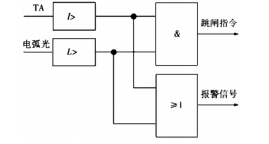

淺析中低壓系統(tǒng)母線裝設(shè)弧光保護的必要性及應(yīng)用

工業(yè)工程軟件在企業(yè)導入中的重要性與必要性

AD603輸入阻抗很小,輸入端用電容耦合的必要性在哪里?

智能開關(guān)柜一鍵順控的必要性有哪些?

行車記錄儀CCC認證的必要性分析

政府門戶網(wǎng)站IPv6升級改造的必要性及緊迫性

集成芯片的重要性和必要性

示波器測量交流電壓不能接地的原因和必要性

LED電路保護的必要性 LED損壞的原因 保護LED電路小絕招

防雷檢測認證服務(wù)的作用和必要性

工藝升級是否必要性,EUV和GAAFET技術(shù)解讀

工藝升級是否必要性,EUV和GAAFET技術(shù)解讀

評論