大家好:我是毛華望。目前在參加紫光同創(chuàng)PGL22G開發(fā)平臺試用。作為FPGA工程師開始對國產(chǎn)的FPGA進(jìn)行試用分析。主要使用的FPGA是2家的,inter和xilinx的,lattice的沒有使用過。據(jù)說lattice的也很便宜。

國產(chǎn)器件的價格優(yōu)勢不用說了,所以沒辦法用同等價位的器件進(jìn)行比較。先說說對于器件和軟件的看法吧。

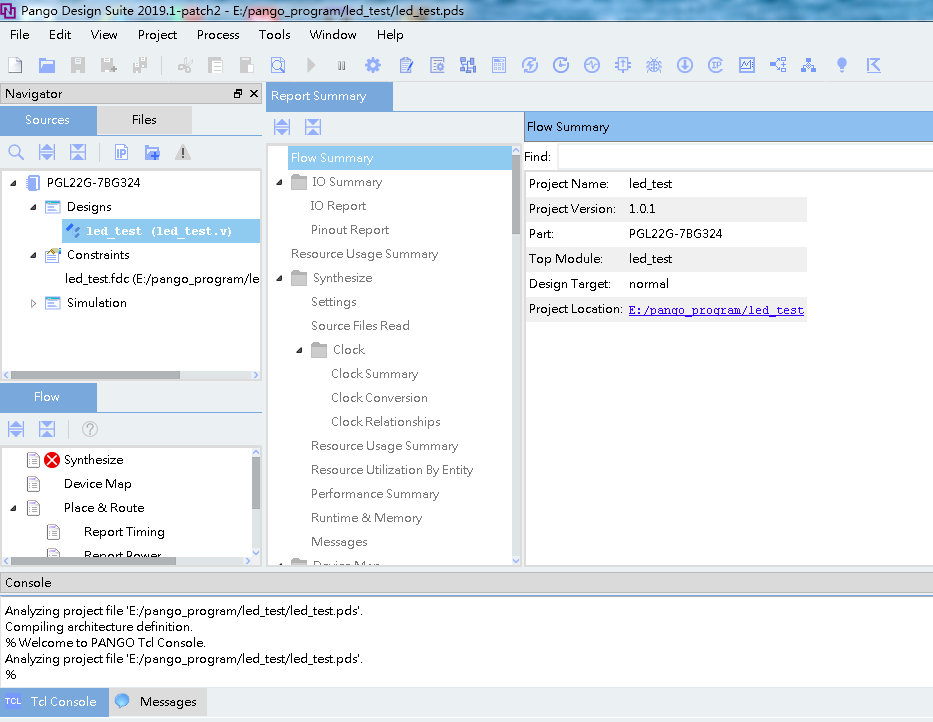

目前個人還在申請軟件Synplify許可。一會我說說明為何用紫光的軟件需要synplify的許可。軟件日期:Pango Design Suite 2019.1-patch2

器件對比:我常使用的器件為spartan 6 系列的 16k或者25k的資源。符合平時我的使用要求。

問題1:為何紫光的器件用的是lut5. 而altera和xilinx的用的lut4呢??答:居然是為了避免專利碰撞。

問題2:lut5的個數(shù)能不能完全劃等號等效1.2個lut4呢?? 答:不能。在我們寫程序過程中。經(jīng)常是reg [7:0] a; 就說明a占用了2個LUT4。如果是紫光的LUT5結(jié)構(gòu),我們也需要用2個,剩余的3條線,可能就會剩下了。在我們使用過程中,最多的數(shù)字都是2的倍數(shù)。所以,使用lut5的時候,并不能充分的用滿。剩下的就看軟件是不是能很好的布局布線了。也可以寫程序的時候,認(rèn)為的寫成reg【9:0】 a。充分利用。

硬件上增加了APM,ADC。至于HSST和HMEMC是是啥我還不知道。哈哈。在透露一個消息。pango,是有內(nèi)部再帶SDRAM的。

已經(jīng)可以支持到DDR3的800M。內(nèi)部頻率150M---200M,可以很好的運行。硬件部分和國外的中低端的產(chǎn)品相比已經(jīng)可以了。也符合大眾使用情況了。那開始說說軟件了。

整個界面的內(nèi)容基本上是和altera和xilinx的是一樣的,上手就很容易了。

關(guān)于這里synthesize報錯和為何要申請Synplify許可。從我問到的情況來說,軟件的編譯是需要synplify的。紫光的軟件并沒有編譯能力,編譯的部分是交給第三方軟件synplify的。所以,這里在沒有synplify的許可的情況下,沒辦法編譯過的。

當(dāng)然了,據(jù)說是已經(jīng)有了synplify的永久授權(quán)。就和華為有arm構(gòu)架的永久授權(quán)一樣。

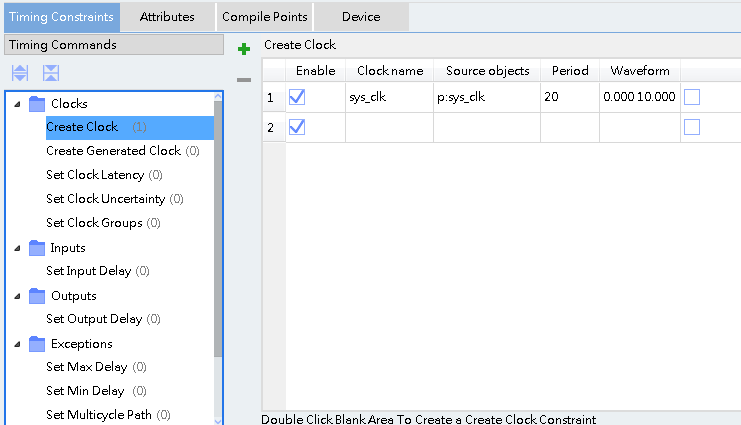

時序分析。

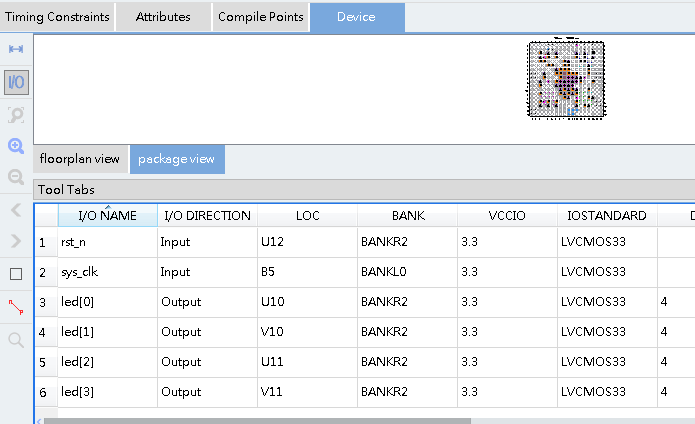

管腳分配

至于里面器件規(guī)劃,在線邏輯分析,能量消耗分析啊,國外器件有的功能。紫光軟件也大體上都有。本人能力有限也就是過過眼,差不多就行了。對比的能力就沒有了。

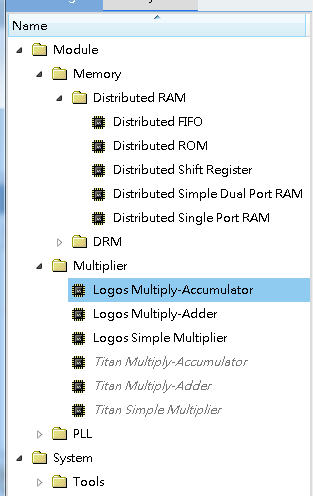

關(guān)于IP核。內(nèi)容就少很多了。常用的ram所有的功能很齊全。 計算單元好像少一些了。另外還有一個比較重要的是SDRAM和DDR的ip核居然沒有???難道ddr3外邊器件的時序需要自己寫??

像我這種低端用戶。差不多行了。要一個ddr3 的模板程序的話,可以了。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602043 -

ARM

+關(guān)注

關(guān)注

134文章

9057瀏覽量

366882 -

軟件

+關(guān)注

關(guān)注

69文章

4799瀏覽量

87178

原文標(biāo)題:紫光同創(chuàng)PGL22G開發(fā)平臺試用連載(1)---軟件和器件

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

紫光同創(chuàng)PGL22G開發(fā)平臺試用---軟件和器件

紫光同創(chuàng)PGL22G開發(fā)平臺試用---軟件和器件

評論