除了元器件的選擇和電路設(shè)計之外,良好的印制電路板(PCB)設(shè)計在電磁兼容性中也是一個非常重要的因素。PCB EMC設(shè)計的關(guān)鍵,是盡可能減小回流面積,讓回流路徑按照設(shè)計的方向流動。

最常見返回電流問題來自于參考平面的裂縫、變換參考平面層、以及流經(jīng)連接器的信號。跨接電容器或是去耦合電容器可能可以解決一些問題,但是必需要考慮到電容器、過孔、焊盤以及布線的總體阻抗。

今天將從PCB的分層策略、布局技巧和布線規(guī)則三個方面,聊聊EMC的PCB設(shè)計技術(shù)。

01 PCB分層策略

電路板設(shè)計中厚度、過孔制程和電路板的層數(shù)不是解決問題的關(guān)鍵,優(yōu)良的分層堆疊是保證電源匯流排的旁路和去耦、使電源層或接地層上的瞬態(tài)電壓最小并將信號和電源的電磁場屏蔽起來的關(guān)鍵。

從信號走線來看,好的分層策略應(yīng)該是把所有的信號走線放在一層或若干層,這些層緊挨著電源層或接地層。

對于電源,好的分層策略應(yīng)該是電源層與接地層相鄰,且電源層與接地層的距離盡可能小,這就是我們所講的“分層”策略。下面我們將具體談?wù)剝?yōu)良的PCB分層策略。

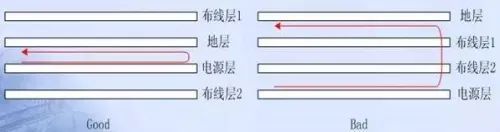

1、布線層的投影平面應(yīng)該在其回流平面層區(qū)域內(nèi)。布線層如果不在其回流平面層地投影區(qū)域內(nèi),在布線時將會有信號線在投影區(qū)域外,導(dǎo)致“邊緣輻射”問題,并且還會導(dǎo)致信號回路面積地增大,導(dǎo)致差模輻射增大。

2、盡量避免布線層相鄰的設(shè)置。因為相鄰布線層上的平行信號走線會導(dǎo)致信號串?dāng)_,所以如果無法避免布線層相鄰,應(yīng)該適當(dāng)拉大兩布線層之間的層間距,縮小布線層與其信號回路之間的層間距。

3、相鄰平面層應(yīng)避免其投影平面重疊。因為投影重疊時,層與層之間的耦合電容會導(dǎo)致各層之間的噪聲互相耦合。

02 多層板設(shè)計

時鐘頻率超過5MHz,或信號上升時間小于5ns時,為了使信號回路面積能夠得到很好的控制,一般需要使用多層板設(shè)計。在設(shè)計多層板時應(yīng)注意如下幾點原則:

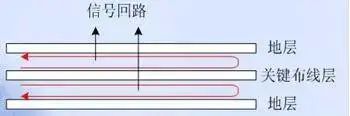

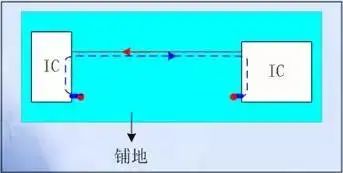

1、關(guān)鍵布線層(時鐘線、總線、接口信號線、射頻線、復(fù)位信號線、片選信號線以及各種控制信號線等所在層)應(yīng)與完整地平面相鄰,優(yōu)選兩地平面之間,如圖1所示。關(guān)鍵信號線一般都是強輻射或極其敏感的信號線,靠近地平面布線能夠使其信號回路面積減小,減小其輻射強度或提高抗干擾能力。

圖1 關(guān)鍵布線層在兩地平面之間

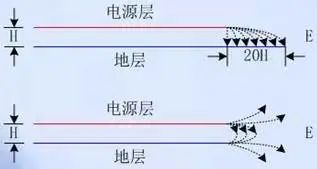

2、電源平面應(yīng)相對于其相鄰地平面內(nèi)縮(建議值5H~20H)。電源平面相對于其回流地平面內(nèi)縮可以有效抑制“邊緣輻射”問題,如圖2所示。

圖2電源平面應(yīng)相對于其相鄰地平面內(nèi)縮

此外,單板主工作電源平面(使用最廣泛的電源平面)應(yīng)與其地平面緊鄰,以有效地減小電源電流的回路面積,如圖3所示。

圖3 電源平面應(yīng)與其地平面緊鄰

3、單板TOP、BOTTOM層是否無≥50MHz的信號線。如有,最好將高頻信號走在兩個平面層之間,以抑制其對空間的輻射。

03 單層板和雙層板設(shè)計

對于單層板和雙層板的設(shè)計,主要應(yīng)注意關(guān)鍵信號線和電源線的設(shè)計。電源走線附近必須有地線與其緊鄰、平行走線,以減小電源電流回路面積。

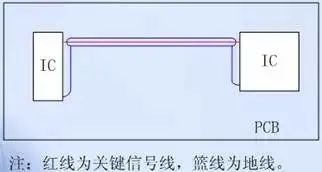

單層板的關(guān)鍵信號線兩側(cè)應(yīng)該布“Guide Ground Line”,如圖4所示。雙層板的關(guān)鍵信號線地投影平面上應(yīng)有大面積鋪地,或者同單層板地處理辦法,設(shè)計“Guide Ground Line”,如圖5所示。

關(guān)鍵信號線兩側(cè)地“保衛(wèi)地線”一方面可以減小信號回路面積,另外,還可以防止信號線與其他信號線之間地串?dāng)_。

圖4單層板的關(guān)鍵信號線兩側(cè)布“Guide Ground Line”

圖5 雙層板的關(guān)鍵信號線地投影平面上大面積鋪地

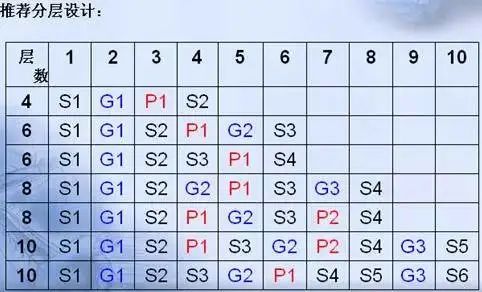

總的來說,PCB板的分層可以依據(jù)下表來設(shè)計。

04 PCB布局技巧

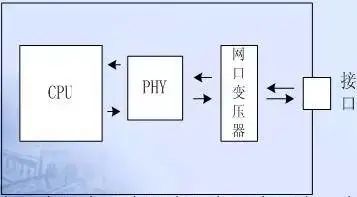

PCB布局設(shè)計時,應(yīng)充分遵守沿信號流向直線放置的設(shè)計原則,盡量避免來回環(huán)繞,如圖6所示。這樣可以避免信號直接耦合,影響信號質(zhì)量。

此外,為了防止電路之間、電子元器置和元器件的布局應(yīng)遵從如下原則:

圖 6 電路模塊沿信號流向直線放置

1、單板上如果設(shè)計了接口“干凈地”,則濾波、隔離器件應(yīng)放置在“干凈地”和工作地之間的隔離帶上。這樣可以避免濾波或隔離器件通過平面層互相耦合,削弱效果。此外,“干凈地”上,除了濾波和防護器件之外,不能放置任何其他器件。

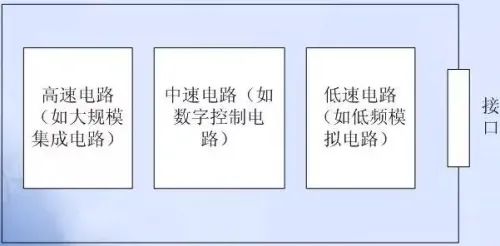

2、多種模塊電路在同一PCB上放置時,數(shù)字電路與模擬電路、高速與低速電路應(yīng)分開布局,以避免數(shù)字電路、模擬電路、高速電路以及低速電路之間的互相干擾。另外,當(dāng)線路板上同時存在高、中、低速電路時,為了避免高頻電路噪聲通過接口向外輻射,應(yīng)該遵從圖7中的布局原則。

圖7 高、中、低速電路布局原則

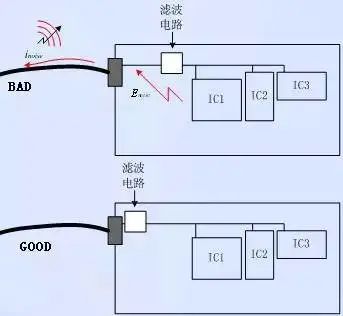

3、線路板電源輸入口的濾波電路應(yīng)應(yīng)靠近接口放置,避免已經(jīng)經(jīng)過了濾波的線路被再次耦合。

圖8 電源輸入口的濾波電路應(yīng)應(yīng)靠近接口放置

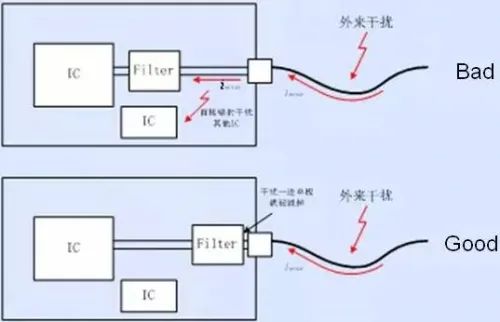

4、接口電路的濾波、防護以及隔離器件靠近接口放置,如圖9所示,可以有效的實現(xiàn)防護、濾波和隔離的效果。如果接口處既有濾波又有防護電路,應(yīng)該遵從先防護后濾波的原則。

因為防護電路是用來進行外來過壓和過流抑制的,如果將防護電路放置在濾波電路之后,濾波電路會被過壓和過流損壞。

此外,由于電路的輸入輸出走線相互耦合時會削弱濾波、隔離或防護效果,布局時要保證濾波電路(濾波器)、隔離以及防護電路的輸入輸出線不要相互耦合。

圖9接口電路的濾波、防護以及隔離器件靠近接口放置

5、敏感電路或器件(如復(fù)位電路等)遠離單板各邊緣特別是單板接口側(cè)邊緣至少1000mil。

6、存在較大電流變化的單元電路或器件(如電源模塊的輸入輸出端、風(fēng)扇及繼電器)附近應(yīng)放置儲能和高頻濾波電容,以減小大電流回路的回路面積。

7、濾波器件需并排放置,以防止濾波后的電路被再次干擾。

8、晶體、晶振、繼電器、開關(guān)電源等強輻射器件遠離單板接口連接器至少1000mil。這樣可將干擾直接向外輻射或在外出電纜上耦合出電流來向外輻射。

05 PCB布線規(guī)則

除了元器件的選擇和電路設(shè)計之外,良好的印制電路板(PCB)布線在電磁兼容性中也是一個非常重要的因素。既然PCB是系統(tǒng)的固有成分,在PCB布線中增強電磁兼容性不會給產(chǎn)品的最終完成帶來附加費用。

任何人都應(yīng)記住一個拙劣的PCB布線能導(dǎo)致更多的電磁兼容問題,而不是消除這些問題,在很多例子中,就算加上濾波器和元器件也不能解決這些問題。到最后,不得不對整個板子重新布線。

因此,在開始時養(yǎng)成良好的PCB布線習(xí)慣是最省錢的辦法。下面將對PCB布線的一些普遍規(guī)則和電源線、地線及信號線的設(shè)計策略進行介紹,最后,根據(jù)這些規(guī)則,對空氣調(diào)節(jié)器的典型印制電路板電路提出改進措施。

1、 布線分離

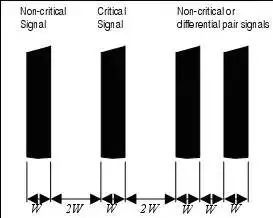

布線分離的作用是將PCB同一層內(nèi)相鄰線路之間的串?dāng)_和噪聲耦合最小化。3W規(guī)范表明所有的信號(時鐘,視頻,音頻,復(fù)位等等)都必須象圖10所示那樣,在線與線,邊沿到邊沿間予以隔離。

為了進一步的減小磁耦合,將基準地布放在關(guān)鍵信號附近以隔離其他信號線上產(chǎn)生的耦合噪聲。

圖10 線跡隔離

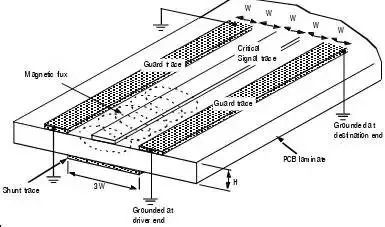

2、保護與分流線路

設(shè)置分流和保護線路是對關(guān)鍵信號,比如對在一個充滿噪聲的環(huán)境中的系統(tǒng)時鐘信號進行隔離和保護的非常有效的方法。在圖21中,PCB內(nèi)的并聯(lián)或者保護線路是沿著關(guān)鍵信號的線路布放。

保護線路不僅隔離了由其他信號線上產(chǎn)生的耦合磁通,而且也將關(guān)鍵信號從與其他信號線的耦合中隔離開來。分流線路和保護線路之間的不同之處在于分流線路不必被端接(與地連接),但是保護線路的兩端都必須連接到地。為了進一步的減少耦合,多層PCB中的保護線路可以每隔一段就加上到地的通路。

圖11 分流和保護線路

3、電源線設(shè)計

根據(jù)印制線路板電流的大小,盡量加粗電源線寬度,減少環(huán)路電阻。同時、使電源線、地線的走向和數(shù)據(jù)傳遞的方向一致,這樣有助于增強抗噪聲能力。在單面板或雙面板中,如果電源線走線很長,應(yīng)每隔3000mil對地加去耦合電容,電容取值為10uF+1000pF。

4、地線設(shè)計(底線設(shè)計原則)

(1)數(shù)字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應(yīng)使它們盡量分開。低頻電路的地應(yīng)盡量采用單點并聯(lián)接地,實際布線有困難時可部分串聯(lián)后再并聯(lián)接地。高頻電路宜采用多點串聯(lián)接地,地線應(yīng)短而租,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應(yīng)盡量加粗。若接地線用很紉的線條,則接地電位隨電流的變化而變化,使抗噪性能降低。因此應(yīng)將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應(yīng)在2~3mm以上。

(3)接地線構(gòu)成閉環(huán)路。只由數(shù)字電路組成的印制板,其接地電路布成團環(huán)路大多能提高抗噪聲能力。

5、信號線設(shè)計

對于關(guān)鍵信號線,如果單板有內(nèi)部信號走線層,則時鐘等關(guān)鍵信號線布在內(nèi)層,優(yōu)先考慮優(yōu)選布線層。另外,關(guān)鍵信號線一定不能跨分割區(qū)走線,包括過孔、焊盤導(dǎo)致的參考平面間隙,否則會導(dǎo)致信號回路面積的增大。而且關(guān)鍵信號線應(yīng)距參考平面邊沿≥3H(H為線距離參考平面的高度),以抑制邊緣輻射效應(yīng)。

對于時鐘線、總線、射頻線等強輻射信號線和復(fù)位信號線、片選信號線、系統(tǒng)控制信號等敏感信號線,應(yīng)遠離接口外出信號線。從而避免強輻射信號線上的干擾耦合到外出信號線上,向外輻射;也避免接口外出信號線帶進來的外來干擾耦合到敏感信號線上,導(dǎo)致系統(tǒng)誤操作。

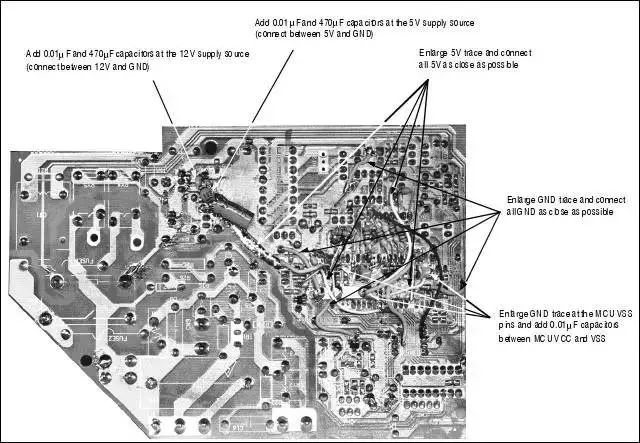

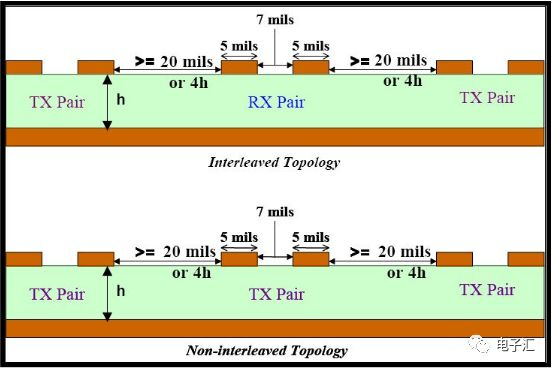

對于差分信號線應(yīng)同層、等長、并行走線,保持阻抗一致,差分線間無其它走線。因為保證差分線對的共模阻抗相等,可以提高其抗干擾能力。根據(jù)以上布線規(guī)則,對空氣調(diào)節(jié)器的典型印制電路板電路進行改進優(yōu)化,如圖12所示。

圖12改進空氣調(diào)節(jié)器的典型印制電路板電路

總體來說,PCB設(shè)計對EMC的改善是:在布線之前,先研究好回流路徑的設(shè)計方案,就有最好的成功機會,可以達成降低EMI輻射的目標(biāo)。

而且在還沒有動手實際布線之前,變更布線層等都不必花費任何錢,是改善EMC最便宜的做法。

-

電容器

+關(guān)注

關(guān)注

64文章

6204瀏覽量

99319 -

元器件

+關(guān)注

關(guān)注

112文章

4692瀏覽量

92013 -

印制電路板

+關(guān)注

關(guān)注

14文章

952瀏覽量

40706 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3493瀏覽量

4378

原文標(biāo)題:必須收入囊中的 PCB EMC 設(shè)計關(guān)鍵因素

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

了解TI基于PCB布線規(guī)則的DDR時序規(guī)范

非常實用的PCB布局布線規(guī)則,畫出美而高性能的板子

PCB設(shè)計的EMC有哪些注意事項

高速pcb布線規(guī)則有哪些

pcb電源布線規(guī)則分享 PCB電源布線的六大技巧

PCB設(shè)計優(yōu)化丨布線布局必須掌握的檢查項

pcb設(shè)計布局布線原則及規(guī)則

為什么說元器件布線布局很重要?PCB設(shè)計元器件放置指南

EMC之PCB設(shè)計技巧

EMC/EMI模擬仿真的薄弱環(huán)節(jié)PCB設(shè)計過程實例詳解

PCB設(shè)計成敗應(yīng)該要注意的問題分享

布局技巧和布線規(guī)則三個方面,聊聊EMC的PCB設(shè)計技術(shù)

布局技巧和布線規(guī)則三個方面,聊聊EMC的PCB設(shè)計技術(shù)

評論