能源與環境是當今全球性熱點問題之一。天然氣作為城市清潔能源,對我國的能源節約、環境保護、人民生活水平的提高和社會經濟的發展有著重要的促進作用。天然氣在我國的應用越來越廣泛,城市燃氣不會局限于以居民生活用氣為主,而是在居民用氣普及率提高的同時,拓展在車輛、采暖、制冷、商業和工業領域的應用。未來幾年內,我國天然氣需求將快于煤炭和石油需求,天然氣市場在全國范圍內將得到較大發展。目前,我國天然氣輸送管道所到之處,可以說是發展天然氣終端市場的大好之地。高速增長的市場必然帶來無限的商機。

天然氣在輸送、分配和使用過程中,需要對天然氣的輸送量、分配量和用戶用量進行計量。在天然氣流量的實用計量中,通常用某一段時間間隔內通過天然氣管道輸送的天然氣總量來表示,即天然氣的體積總量。天然氣總量的計量對象類型很多,氣源售出計量、城市購入計量、區域供氣計量和用戶用氣計量等。目前國內天然氣大都使用體積計量的方法,但由于天然氣在不同的溫度和壓力下,氣體體積有較為明顯的變化,采用簡單的體積計量,明顯不符合公平交易的原則。如何將工況下的天然氣體積通過溫度、壓力和壓縮系數進行修正,從而得到標準狀況下的體積,是保證天然氣貿易結算公平的關鍵所在。信息技術的不斷發展、計算機技術在計量系統中的廣泛應用將會提高天然氣的計量精度,加快測量數據的傳遞速度。

1 儀表總體設計

天然氣體積修正儀主要完成天然氣流量的自動修正,適于安裝在工廠、住宅等環境,實時反映天然氣的流量計量情況,并可與上位機進行通信,為上位機管理軟件提供數據支持。

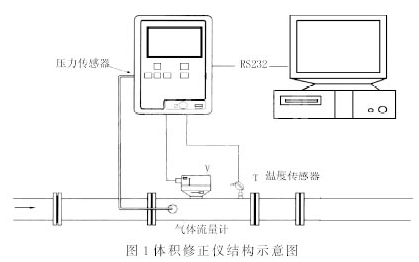

體積修正儀通過壓力傳感器和溫度傳感器采集壓力和溫度信息,結合氣體流量計采集的流量脈沖信號進行天然氣流量的自動修正,并通過RS232標準進行串口數據傳送。圖1是體積修正儀的結構示意圖。

天然氣體積修正儀根據功能設計如下5個模塊:數據采集模塊、體積修正模塊、液晶顯示模塊、按鍵模塊以及與上位機通信模塊。幾個功能模塊采用低功耗FPGA器件,以Nios Ⅱ嵌入式處理器為核心,利用SoPC技術完成嵌入式開發。

2 數據采集模塊設計

在天然氣體積修正儀設計中,數據采集模塊是保證測量和計算精度的首要模塊。分為輸入檢測和數據處理兩部分。

2.1 輸入檢測

天然氣體積修正儀前端測量中涉及2個模擬量:溫度和壓力信號。根據溫度和壓力值可計算出天然氣的壓縮因子,從而校正天然氣的體積。

2.1.1 溫度檢測

照顧到民用和商用的范圍,設計采用Pt100陶瓷高性能鉑熱電阻溫度計作為測溫元件,鉑在氧化性介質中,甚至在高溫下的物理、化學性質都很穩定。另外,Pt100溫度傳感器還具有抗振動、穩定性好、準確度高、耐高壓等優點。

本設計氣體溫度范圍為:-30 ℃~70 ℃。經放大電路放大后電壓變化范圍在0V~4.5 V之間。

2.1.2 壓力檢測

由于工作壓力范圍為0~10 MPa,經過選型,采用CGYL-202壓力變送器,其三線制輸出電壓范圍為0 V~5 V,配合溫度信號,方便后續模數轉換。壓力變送器采用硅杯壓阻傳感器為敏感元件,具有體積小、質量輕、結構簡單和穩定性好的優點,精度也較高。且具有本安防爆認證,防震性能好。

2.2 A/D轉換及數據處理

經采集的溫度壓力信號在參與壓縮因子計算前必須經過模數轉換。

本設計采用12位4通道、高速低功耗A/D轉換芯片AD7864。AD7864是美國ADI公司生產的逐次逼近式并行輸出的A/D轉換器,片內由12位ADC、時鐘電路、5 V高精度參考電壓源和比較器組成,無需任何外部電路即可完成整個A/D轉換的過程。該轉換器自身帶有4路采樣/保持電路,可同時進行采樣轉換,這樣就節省了系統的硬件電路空間。該器件最快轉換時間可達1.65μs,信號輸入范圍可為0 V~5 V、±5 V或±10 V。

AD7864的控制狀態引腳主要有:

(1)轉換啟動信號CONVST,下降沿觸發一次四通道轉換;

(2)工作狀態忙信號輸出BUSY,高為忙;

(3)讀轉換結果控制信號RD,低電平有效;

(4)片選信號CS,低電平有效;

(5)轉換結束狀態輸出信號EOC,低電平有效;

(6)通道選擇信號線SL1~SL4;

(7)硬件/軟件通道選擇方式H/S SEL;

(8)第1個數據輸出狀態信號FRSTDATA,第1通道轉換結束數據可讀觸發為高,第2通道轉換結束變為低。

本系統采用EP1C12Q240型FPGA,其足夠的引腳資源完全能夠滿足需求。

2.2.1 數據采集模塊總體設計

為了讓CPU專注于處理其他任務,專門在FPGA內部設計一個A/D硬件控制器,負責對A/D的采樣控制,并將采樣數據進行濾波處理。該控制器還可以根據CPU的輸出控制字改變采樣的頻率。

頻譜分析的誤差很大程度來自采樣窗口和實際波形的同步不嚴格,造成頻譜泄漏。為消除頻譜泄漏引起的誤差,常用的方法有硬件同步和加窗處理。硬件同步的方法比較多,常用的主要有使用PLL電路進行同步。因此,按照GB/T14549-1993要求,用FPGA內部高精度的PLL產生采樣時鐘來實現嚴格的同步采樣,以保證窗口間無重疊和間隔,并能嚴格與被測信號頻率同步。

在本模塊中,所有時序控制均由FPGA完成,采用VHDL語言對FPGA進行配置,配置后的硬件功能包括對A/D轉換器的控制、12位并行數據的處理和數據的濾波。

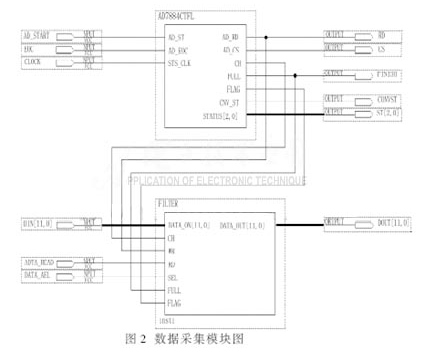

設計2個控制器完成上述功能:A/D控制器和濾波器。A/D控制器用來控制A/D時序,完成A/D轉換功能。濾波模塊完成數據的后續處理。設計模塊圖如圖2所示。

2.2.2 A/D控制器設計

AD7864的工作時序圖如圖3所示。當CONVST信號為下降沿時啟動一次四通道的A/D轉換,因此采樣頻率決定于CONVST信號的頻率,在第一通道開始轉換之后BUSY信號為高,四通道轉換全部結束后變為低,EOC為高表明正在轉換,為低表示一次轉換結束,可讀取結果,此時將片選置為低,同時將讀信號RD置低即可從數據線上將數據讀出。為了便于控制采樣頻率,設置AD_START和CLOCK信號分別作為外部控制A/D開始轉換信號和時鐘信號。

本文采用硬件選擇通道方式,SL1、SL2置高,兩通道依次按順序轉換。由于兩通道采樣數據使用同一路數據總線依次讀出,采用有限狀態機(FSM)實現各通道數據的采集。狀態機是邏輯設計中最重要的設計內容之一,通過狀態轉移圖設計手段可以將復雜的控制時序圖形化表示,分解為狀態之間的轉換關系,將問題簡化。VHDL流水線設計方法可以提高系統的工作頻率,采用VHDL語言編寫控制程序。

狀態機的狀態轉移圖如圖4所示,共分為6個工作狀態:零狀態(idle)、等待狀態(STAND_BY)、轉換第一通道數據(CH0_CONVST)、讀第一通道數據(CH0_RD)、轉換第二通道數據(CH1_CONVST)以及讀第二通道數據(CH1_RD)。

FSM結構體定義信號類型ST和count。ST為狀態,且初始狀態為零狀態;count用于讀數據的計數,用于濾波。

為了實現快速狀態轉換同時增強穩定性,避免出現毛刺現象,A/D轉換器的時序控制采用多進程有限狀態機來實現。

(1) 時序邏輯

時序邏輯進程STATE_TRANS負責狀態轉換,當時鐘信號SYS_CLK上升沿到來時,判斷轉換條件使狀態機轉入相應狀態。

(2) 組合邏輯

組合邏輯進程STATE_BEHV負責狀態輸出,當狀態變量ST發生變化時,產生對應此狀態的CNV_ST,AD_RD AD_CS,CH(0為第一通道,1為第二通道)及STATUS相應輸出。

(3) 計數邏輯

定義P0進程,敏感參數為CNV_ST,當一組數據采樣結束(CNV_ST信號由0變為1),如果已經采集10組數據,則置位FULL信號,表示采樣過程已經結束。

2.2.3 濾波器設計

A/D轉換后的數據還不能立即送入處理器中處理,為了提高數據的準確性,設計濾波單元對數據進行處理。濾波濾波器設計實現經A/D轉換后的數據濾波處理及數據的輸出。

數字濾波模塊的濾波算法采用中位值平均濾波法,相當于“中位值濾波法”+“算術平無度濾波法”,該方法計算簡單、速度快,還可消除由于脈沖干擾所引起的采樣值偏差,使得經濾波后的輸出信號為“干凈”信號,可直接用于工業控制。中位值平均濾波法的時域差分方程是:

本系統設計10組數據進行濾波處理,取N=8。為了節約FPGA內部資源,濾波器的設計中采用移位寄存器代替除法器來實現平均濾波部分的算法。濾波模塊的設計從采樣數據的輸入、數值累加、去極值、求平均值到數字量的輸出共5個處理步驟,并且整個數據處理是“單流向”的,前一步驟的輸出是下一步驟的輸入,符合流水線設計要求。采用流水線設計方法可以提高系統的工作頻率,從宏觀上看數字濾波模塊不占用額外的處理時間,對于超高速A/D轉換控制中顯得格外重要。從VHDL語言的角度看,流水線操作是用面積換速度思想的具體體現[3]。

定義濾波器端口類型見表2所示。

從仿真圖中可以看出,當時鐘處于上升沿,AD_START變為高電平時,啟動A/D轉換,依次讀2個通道的數據。當讀滿10組時,進行濾波處理。當CPU發出讀信號時,數據讀出。可見,設計的A/D控制器和濾波器完全符合設計要求。

對設計程序進行編譯,可以看出,EP1C12Q240C8總的邏輯元數目為12 060,本控制模塊只占用了227個,完全達到數據采集及濾波處理功能,極大地減輕了CPU的負擔,可以讓CPU專注于其他的任務。是一種可行且值得推廣的方法。

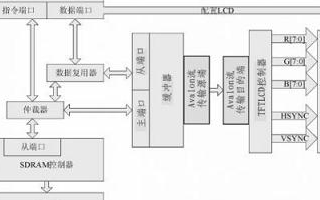

3 總體功能仿真及編譯結果

設計完成,生成頂層模塊。該模塊可直接加入到體積修正儀的SOPC設計中。其總體功能仿真如圖5所示。

從仿真圖中可以看出,當時鐘處于上升沿,AD_START變為高電平時,啟動A/D轉換,依次讀2個通道的數據。當讀滿10組時,進行濾波處理。當CPU發出讀信號時,數據讀出。可見,設計的A/D控制器和濾波器完全符合設計要求。

對設計程序進行編譯,可以看出,EP1C12Q240C8總的邏輯元數目為12 060,本控制模塊只占用了227個,完全達到數據采集及濾波處理功能,極大地減輕了CPU的負擔,可以讓CPU專注于其他的任務。是一種可行且值得推廣的方法。

責任編輯:gt

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752048 -

處理器

+關注

關注

68文章

19169瀏覽量

229158 -

嵌入式

+關注

關注

5069文章

19021瀏覽量

303380

發布評論請先 登錄

相關推薦

采用nios和μClinux實現嵌入式系統設計

如何實現天然氣體積修正儀的系統設計?

Nios II入門起步-創建一個嵌入式處理器系統

基于Chirp函數的Nios Ⅱ嵌入式實現

介紹如何用Nios II 軟核處理器來開發FPGA嵌入式系統軟件

基于NiosⅡ處理器的嵌入式平臺上實現μC/GUI的移植設計

FPGA Nios嵌入式處理器的軟件開發

FPGA Nios嵌入式處理器的軟件開發

基于Nios Ⅱ嵌入式處理器實現天然氣體積修正儀的系統設計

基于Nios Ⅱ嵌入式處理器實現天然氣體積修正儀的系統設計

評論