數(shù)字電路作為一門專業(yè)基礎(chǔ)課,除了介紹數(shù)字電路的理論知識(shí)外,更需要通過(guò)配套的實(shí)驗(yàn)平臺(tái)將理論知識(shí)和實(shí)踐環(huán)節(jié)相結(jié)合,培養(yǎng)學(xué)生的動(dòng)手能力和實(shí)踐創(chuàng)新能力。為此,自主開發(fā)了基于 FPGA 的數(shù)字電路“口袋實(shí)驗(yàn)室”。該“口袋實(shí)驗(yàn)室”基于目前流行的FPGA 芯片開發(fā),已經(jīng)實(shí)際應(yīng)用于數(shù)字電路教學(xué)實(shí)踐中。

1總體設(shè)計(jì)

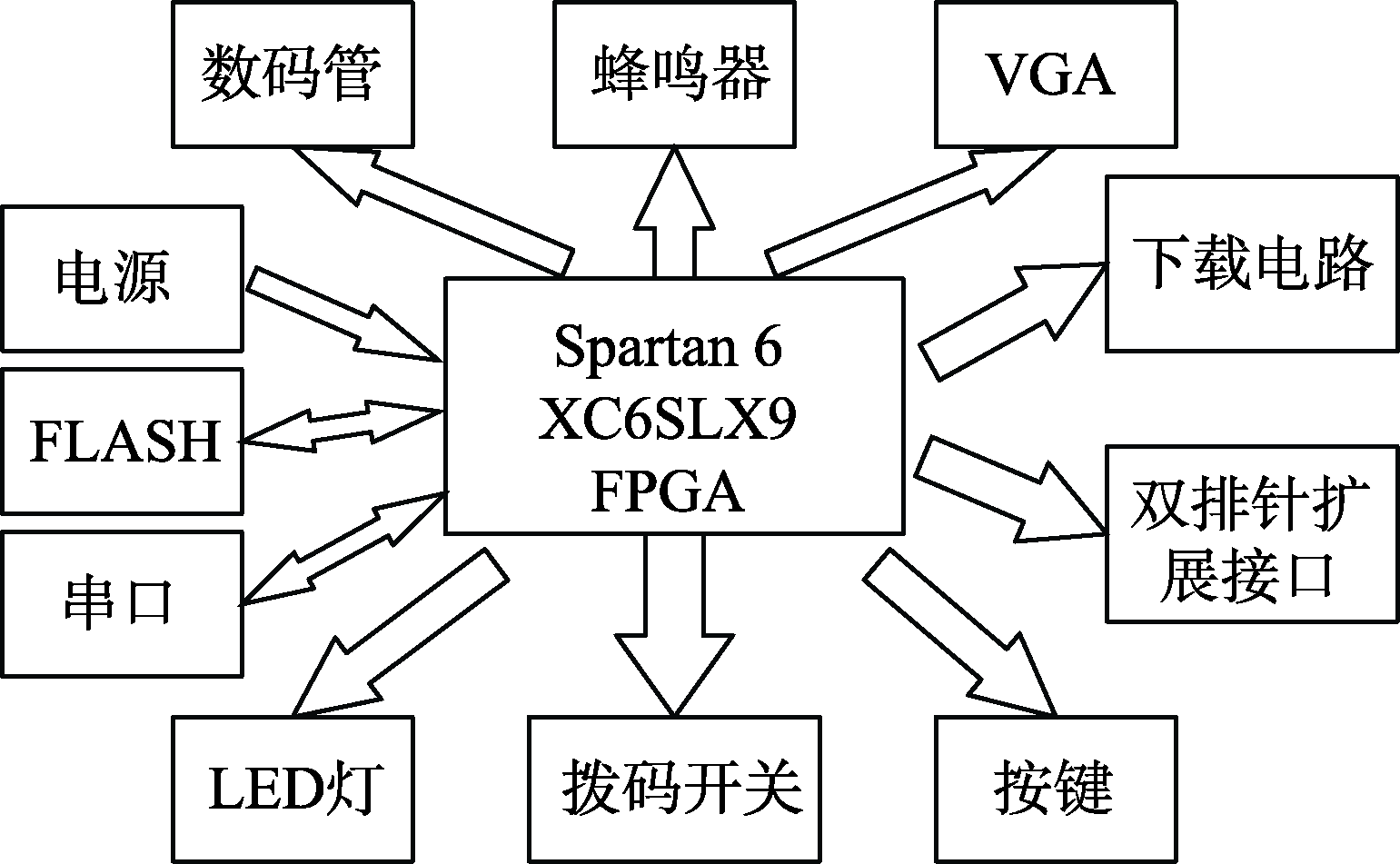

“口袋實(shí)驗(yàn)室”的電路包括電源、FPGA、下載電路、數(shù)碼管、VGA 接口、撥碼開關(guān)、按鍵、LED 燈和雙排針擴(kuò)展接口。其總體框圖見圖 1,實(shí)物圖見圖 2。

圖 1 系統(tǒng)總體框圖

圖 2 系統(tǒng)實(shí)物圖

XC6SLX9 是 Xilinx 公司的 Spartan 系列 FPGA, 采用 45 nm 工藝,共有 9 152 個(gè) Logic Cells、1 430 個(gè)Slices、90 kB 分布式 RAM,共有 144 個(gè)引腳,其中102 個(gè)是通用 I/O 口,資源相對(duì)豐富。XC6SLX9 內(nèi)核供電電壓為 1.2 V;I/O 口的電平可以設(shè)置為 LVTTL、LVCMOS、LVDS 等多種電壓標(biāo)準(zhǔn);內(nèi)置高性能的時(shí)鐘管理模塊,1 個(gè) CMT 包含 1 個(gè) PLL 和 2 個(gè) DCM, 能進(jìn)行分頻、倍頻;XC6SLX9 支持主動(dòng)模式和被動(dòng)模式,以及 SPI、BPI、JTAG 等多種配置方式。

設(shè)計(jì)中預(yù)留了 30 個(gè)擴(kuò)展接口,由雙排針引出,其中 24 個(gè)是 FPGA 的通用 I/O,3 個(gè) 3.3 V 引腳和 3 個(gè)地引腳。串行通信采用 CH340G 串口芯片,用于 FPGA 和 PC 機(jī)之間的通信。“口袋實(shí)驗(yàn)室”擁有 2 個(gè) 4 位共陽(yáng)極數(shù)碼管、1 個(gè)無(wú)源蜂鳴器、1 個(gè)八位撥碼開關(guān)、1 個(gè) VGA 接口以及 10 顆 LED 燈和 6 個(gè)按鍵,可以滿足數(shù)字電路基本的實(shí)驗(yàn)需要。

2.1電源電路

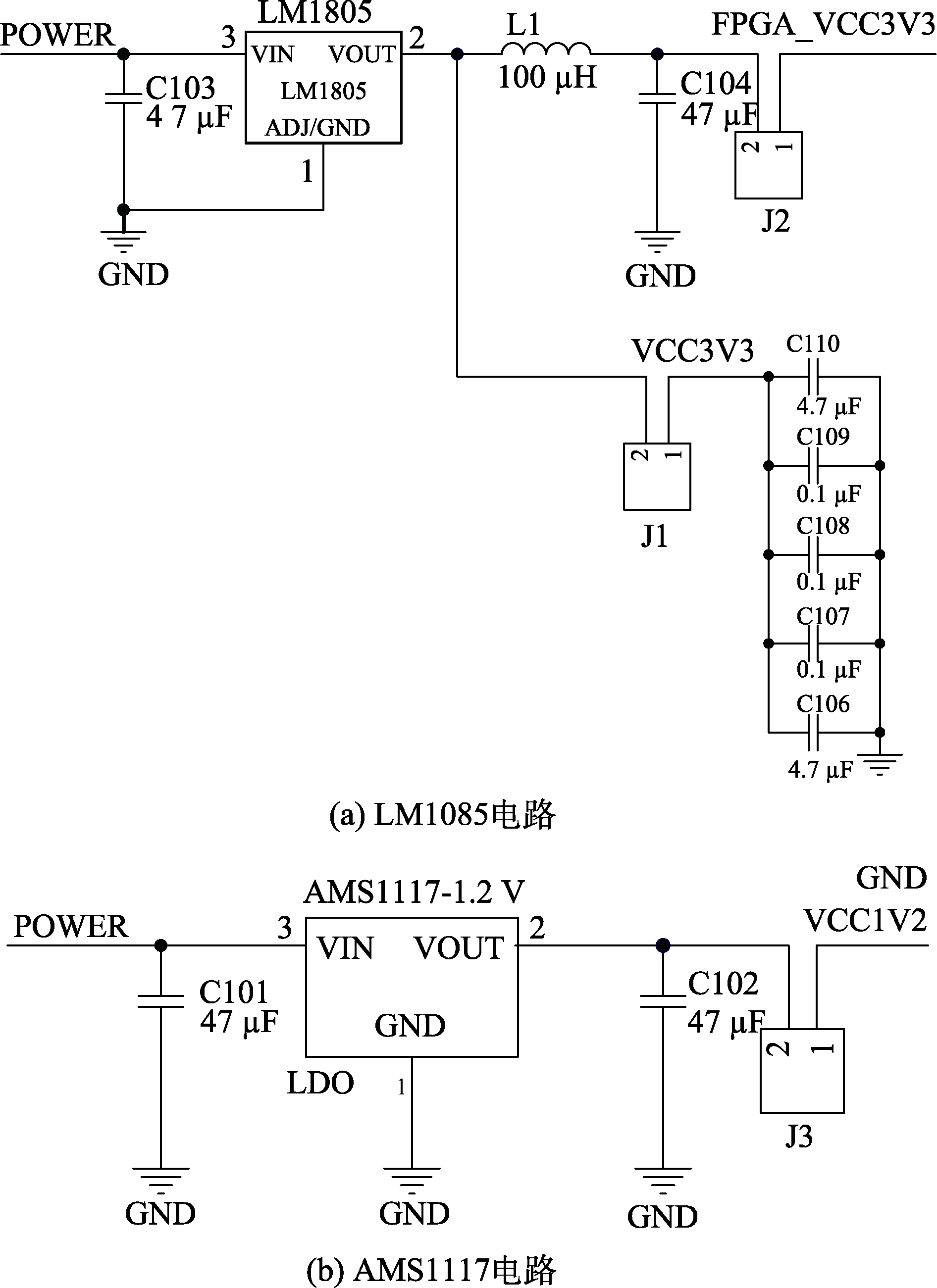

電源系統(tǒng)為整個(gè)系統(tǒng)提供能量,是系統(tǒng)的基礎(chǔ)。采用 LM1085 芯片提供 3.3 V 電壓,采用 AMS1117 芯片提供 1.2 V 電壓。

考慮到XC6SLX9 的 3.3 V 電源和其他外設(shè)共用一個(gè)電源芯片,為保證其他外設(shè)電流突變時(shí)不影響XC6SLX9 的正常供電, 使用一個(gè)功率電感以隔離FPGA 和外設(shè)的電源。具體電路設(shè)計(jì)見圖 3。

圖 3 LM1085 電路和 AMS1117 電路

XC6SLX9 對(duì)電源的要求較高,電源引腳附近需要多個(gè)去耦電容,以減小電源瞬變,保證電源完整性。電源部分還設(shè)計(jì)有 1 顆LED 燈用于指示FPGA 電源是否正常。

2.2配置電路設(shè)計(jì)

配置電路一個(gè)是使用 JTAG 配置的電路,另一個(gè)是使用 FLASH 的主動(dòng) SPI 配置電路。

2.2.1JTAG 配置電路

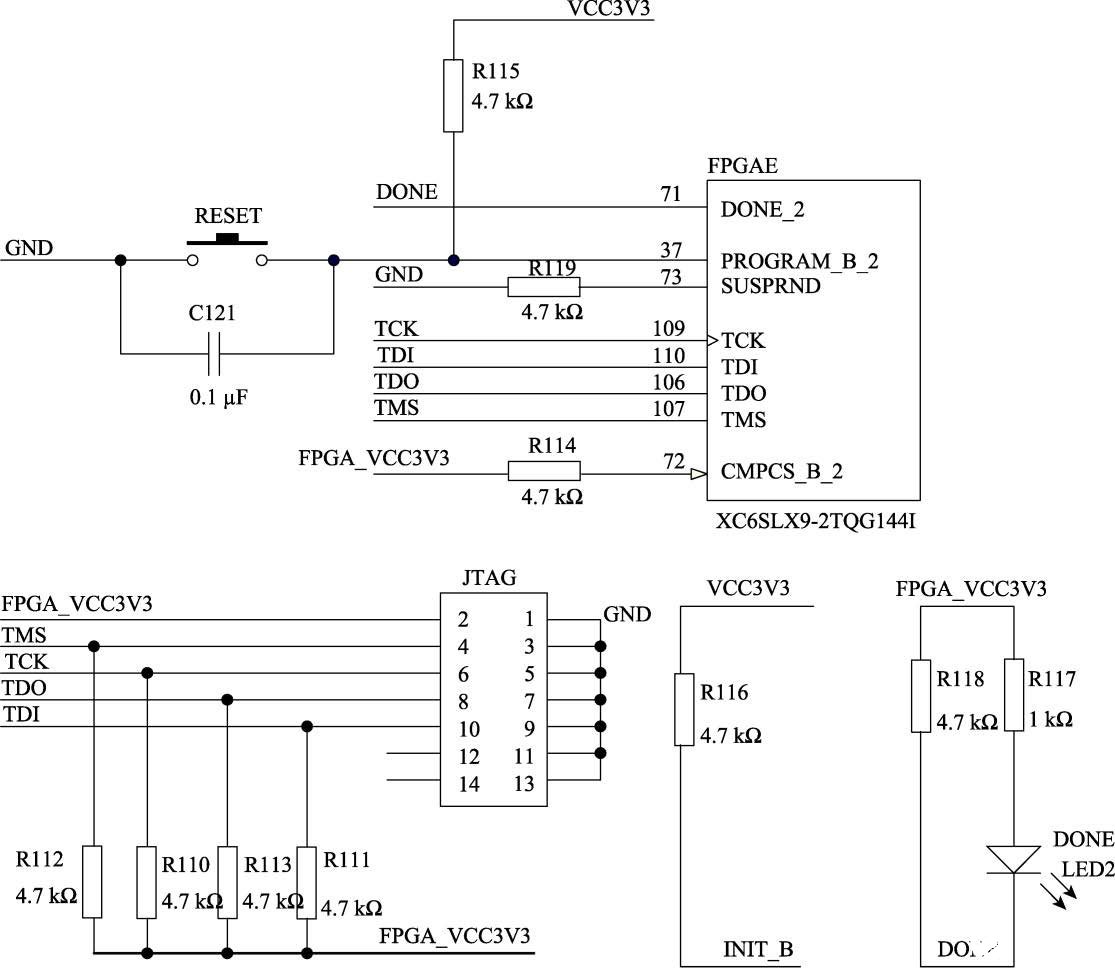

JTAG 配置電路見圖 4。

圖 4 JTAG 配置電路

JTAG 的主要引腳 TMS、TCK、TDI、TDO 經(jīng) 4.7 kΩ

電阻上拉,以保護(hù)電路。JTAG 引腳在印刷電路板(PCB)上通過(guò) 14 針 2.0 mm 間距的簡(jiǎn)易牛角座引出。簡(jiǎn)易牛角座采用防反插設(shè)計(jì),以保證 JTAG 連接正確。

PROGRAM_B 引腳默認(rèn)上拉,通過(guò)按鍵接地,可以用于 FPGA 的軟復(fù)位。DONE 引腳上拉,且有 LED 指示 FPGA 是否配置完成。

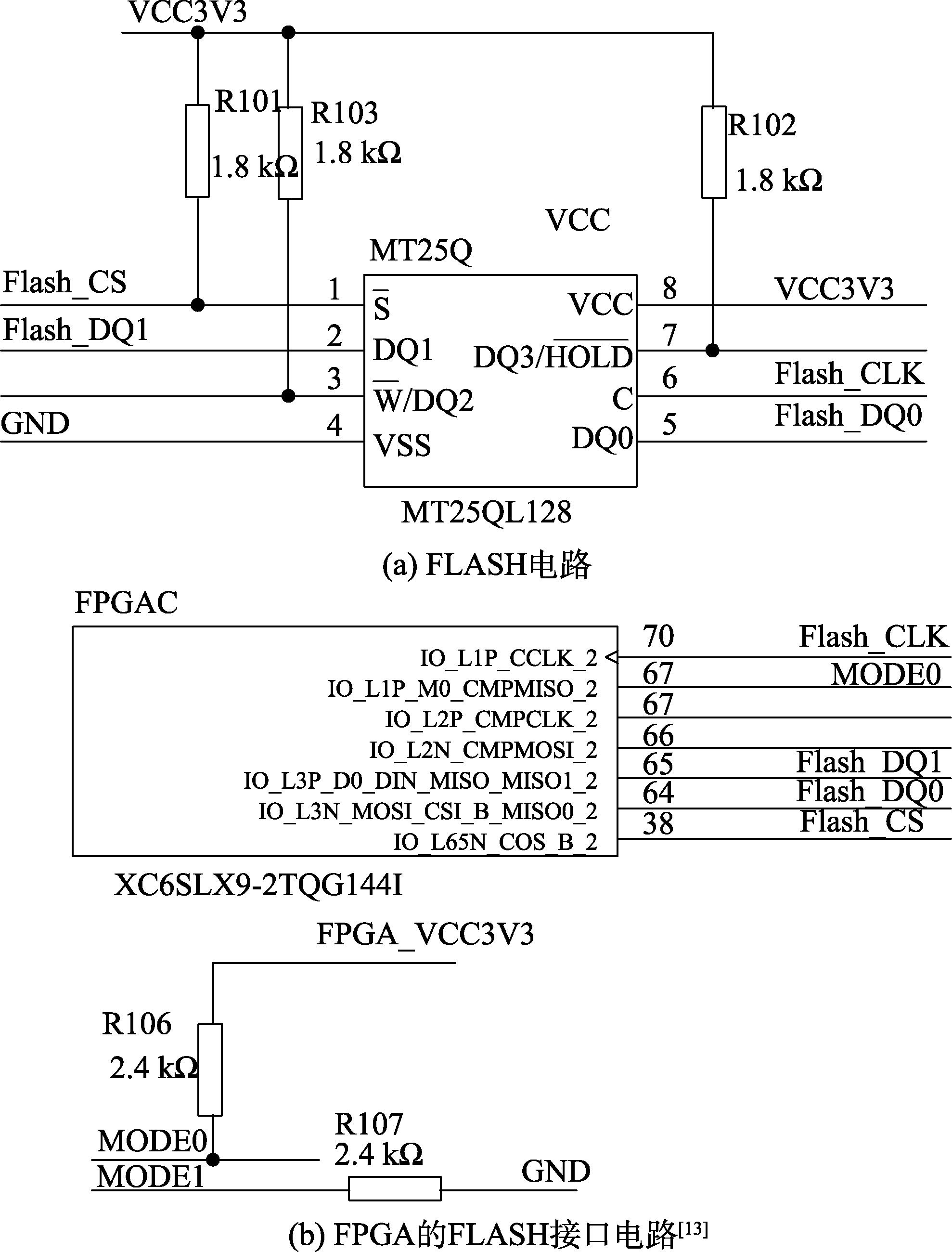

2.2.2FLASH 電路

設(shè)計(jì)所選用的 FPGA 基于 SRAM 工藝,掉電后不能保存數(shù)據(jù),因此在重新上電之后必須從外部的配置存儲(chǔ)器加載配置。FLASH 電路見圖 5(a)。MODE0 和MODE1 的電平?jīng)Q定了 FPGA 的配置方式,當(dāng) MODE0 拉高以及 MODE1 拉低時(shí),F(xiàn)PGA 使用主動(dòng) SPI 配置模式。接口電路見圖 5(b)。

圖 5 FLASH 電路和 FPGA 的 FLASH 接口電路

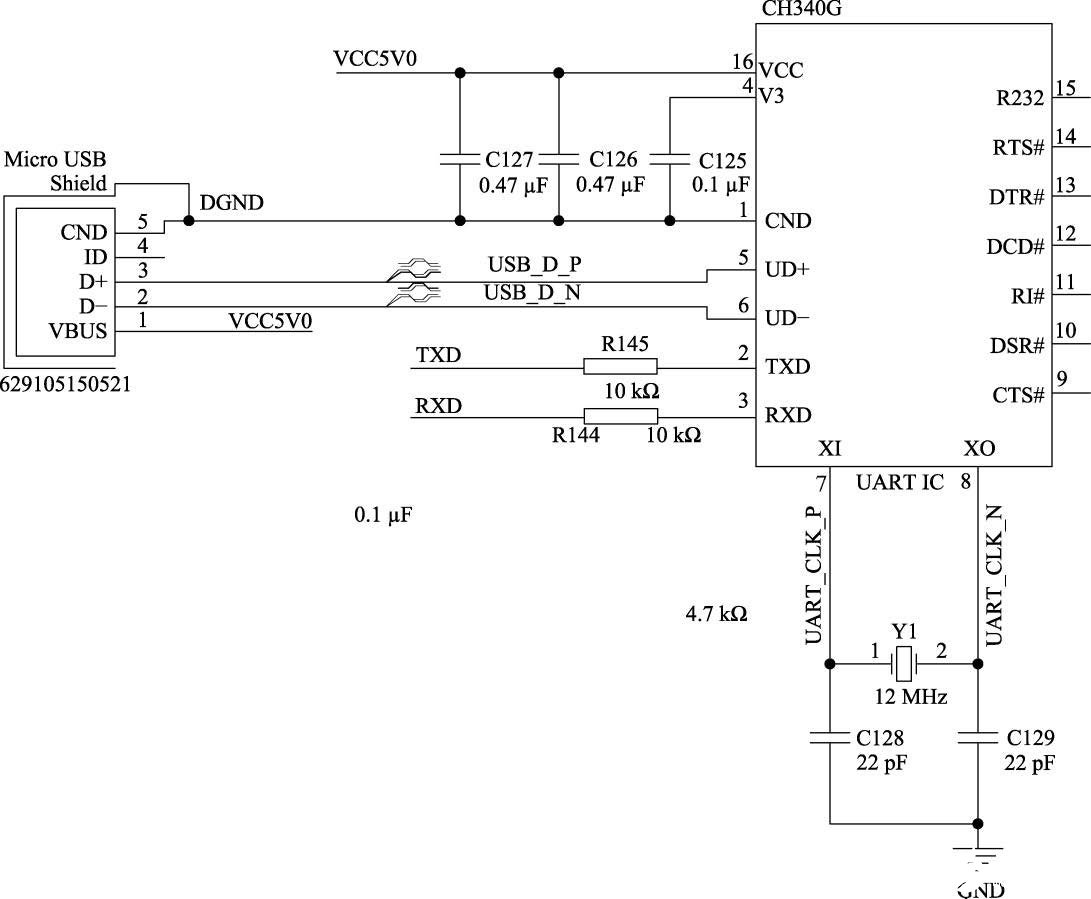

2.3串口通信設(shè)計(jì)

選用 CH340G 作為 FPGA 和 PC 機(jī)之間通信的轉(zhuǎn)換芯片。CH340G 是常用的USB 轉(zhuǎn)串口的芯片,兼容 5 V 系統(tǒng)和 3.3 V 系統(tǒng),由于本設(shè)計(jì)中選用的 XC6SLX9 屬于 3.3 V 系統(tǒng),因此 CH340G 的供電電壓設(shè)置為3.3 V,如果供電電壓調(diào)整為 5 V,則串口通信將發(fā)生故障,數(shù)據(jù)不能通過(guò)串口發(fā)送至 PC 機(jī)。串口部分電路見圖 6。

圖 6 串口通信部分電路

2.4 擴(kuò)展接口設(shè)計(jì)

為保證“口袋實(shí)驗(yàn)室”的擴(kuò)展能力,在設(shè)計(jì)時(shí)將FPGA 的 24 個(gè)通用 I/O 口通過(guò)雙排排針在 PCB 上引出,可供使用者外接電路。

為了防止 FPGA 的 I/O 接口接入過(guò)高的電壓或者通過(guò)過(guò)大的電流而損壞 FPGA,設(shè)計(jì)中使用雙向電平轉(zhuǎn)換芯片 TXS0108E 對(duì) FPGA 的 I/O 口和外部接口進(jìn)行隔離,以保護(hù) FPGA 芯片。

3實(shí)踐教學(xué)實(shí)例

3.1數(shù)碼管顯示實(shí)驗(yàn)

實(shí)驗(yàn)要求使用數(shù)碼管顯示時(shí)間精度為 100 ms 的秒表,最低位數(shù)字每 100 ms 加 1。

3.1.1實(shí)驗(yàn)硬件電路

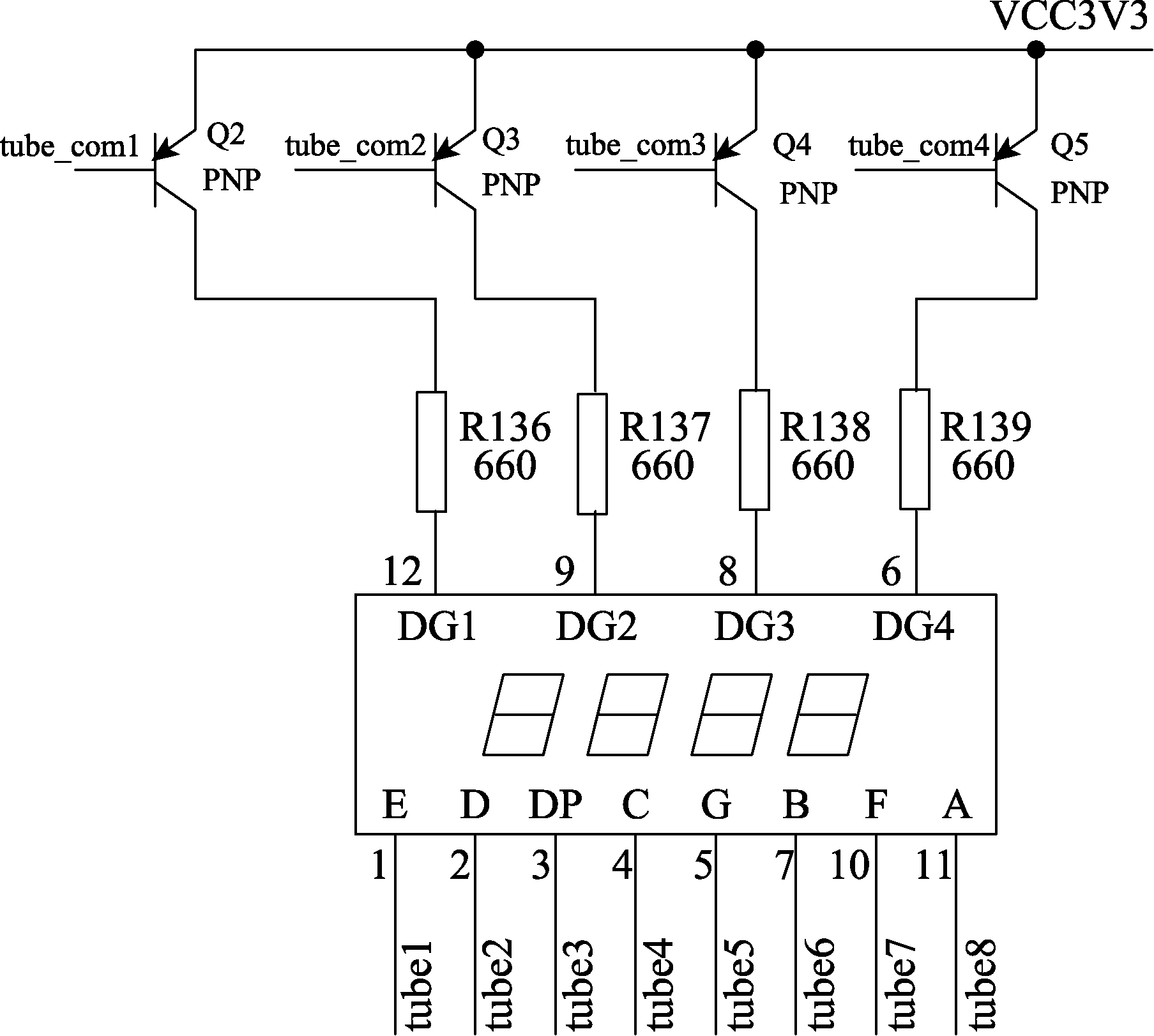

“口袋實(shí)驗(yàn)室”選用的數(shù)碼管是 4 位共陽(yáng)極數(shù)碼管,其中公共端使用三極管驅(qū)動(dòng),其余 A、B、C、D、E、F、G、DP 8 個(gè)引腳分別和 FPGA 的 I/O 口連接。電路如圖 7 所示。

圖 7 數(shù)碼管電路

3.1.2FPGA 代碼設(shè)計(jì)

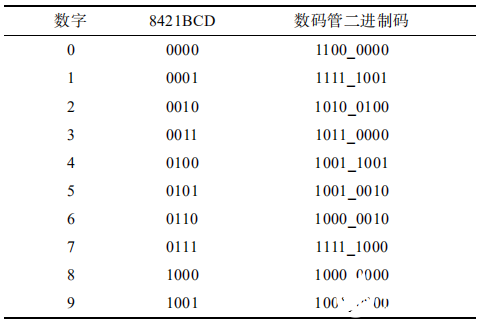

FPGA 代碼設(shè)計(jì)思路如下:將系統(tǒng)的 50 MHz 時(shí)鐘分頻為 50 Hz 的逐位掃描時(shí)鐘和 10 Hz 的計(jì)數(shù)時(shí)鐘,最低位通過(guò) 10 Hz 的時(shí)鐘進(jìn)行計(jì)數(shù),計(jì)數(shù)使用8421BCD 碼表示,并轉(zhuǎn)化為數(shù)碼管顯示的 8 位二進(jìn)制代碼輸出。由于是共陽(yáng)極數(shù)碼管,當(dāng)引腳公共端高電平,其他引腳為低電平時(shí),對(duì)應(yīng)的 LED 才會(huì)亮。數(shù)碼管二進(jìn)制碼的最高位為小數(shù)點(diǎn)位。實(shí)驗(yàn)仿真及實(shí)際運(yùn)行效果見圖 8。

圖 8 數(shù)碼管仿真時(shí)序圖與數(shù)碼管實(shí)驗(yàn)實(shí)際運(yùn)行圖

由于實(shí)際仿真時(shí)間過(guò)長(zhǎng), 因此在仿真時(shí)縮短了計(jì)數(shù)的時(shí)間。表 1 為 BCD 碼與數(shù)碼管二進(jìn)制碼對(duì)應(yīng)表。

表 1 數(shù)字的 BCD 碼與數(shù)碼管二進(jìn)制碼對(duì)應(yīng)表

3.2蜂鳴器控制實(shí)驗(yàn)

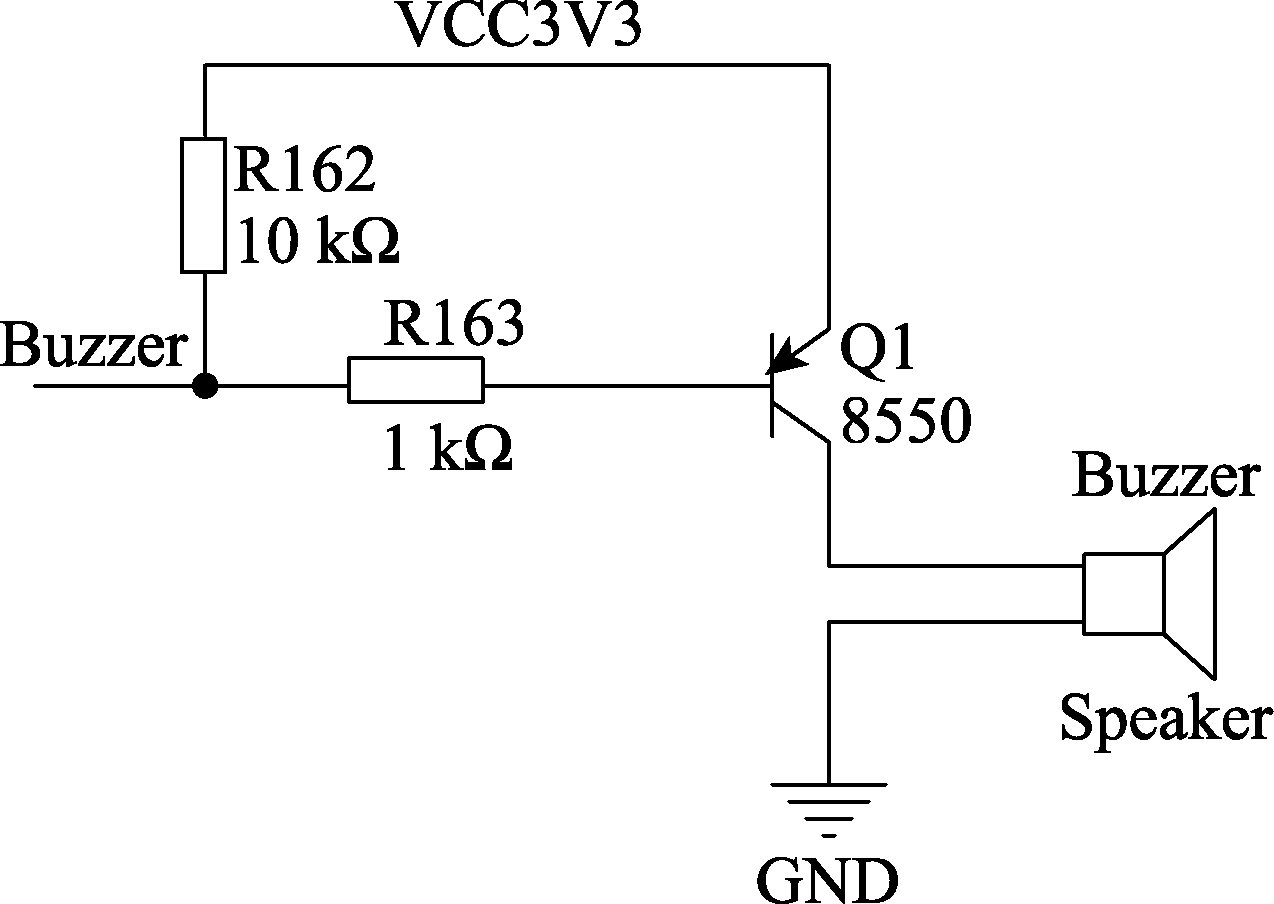

實(shí)驗(yàn)要求通過(guò)編程控制無(wú)源蜂鳴器,使之在輸入不同頻率的 PWM 波情況下,發(fā)出不同音調(diào)頻率的聲音。

3.2.1實(shí)驗(yàn)硬件電路

無(wú)源蜂鳴器的硬件電路設(shè)計(jì)見圖 9。

圖 9 蜂鳴器電路圖

3.2.2FPGA 代碼設(shè)計(jì)

無(wú)源蜂鳴器輸入不同頻率的 PWM 會(huì)發(fā)出不同頻率的聲音,頻率和音調(diào)對(duì)應(yīng)見表 2。

表 2 頻率和音調(diào)對(duì)應(yīng)表

通過(guò) ISE 的 Clock Wizard 將 50 MHz 的系統(tǒng)時(shí)鐘頻率分頻為 12 MHz,然后通過(guò)計(jì)數(shù)輸出不同的頻率, 計(jì)數(shù)的上限值由撥碼開關(guān)和按鍵控制,撥碼開關(guān)用于選擇 3 個(gè)音調(diào),按鍵用于選擇各個(gè)音調(diào)下的 7 個(gè)不同頻率,以此實(shí)現(xiàn)輸出不同音調(diào)頻率的聲音。圖 10 為蜂鳴器控制仿真圖。

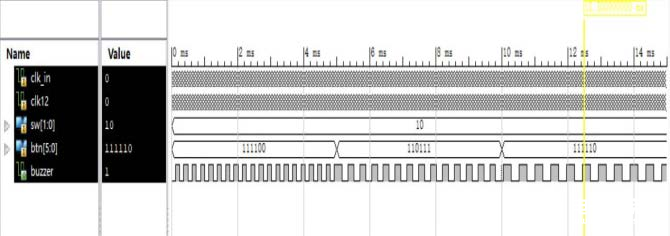

圖 10 蜂鳴器控制仿真圖

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602019 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1601瀏覽量

80511

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路中二極管的角色與應(yīng)用

數(shù)字電路可以處理模擬信號(hào)嗎

數(shù)字電路是對(duì)什么信號(hào)進(jìn)行傳輸?shù)?/a>

數(shù)字電路中的亞穩(wěn)態(tài)是什么

數(shù)字電路和模擬電路的區(qū)別與聯(lián)系

數(shù)字電路仿真元件符號(hào)是什么

數(shù)字電路與邏輯設(shè)計(jì)

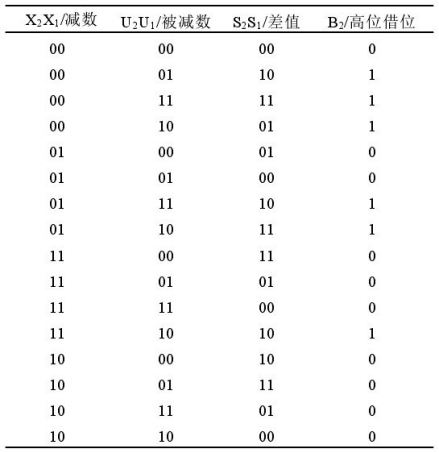

兩位格雷碼減法器數(shù)字電路設(shè)計(jì)

數(shù)字電路中的邏輯門電路分類

與模擬電路比數(shù)字電路的優(yōu)點(diǎn)

數(shù)字電路和模擬電路的區(qū)別

數(shù)字電路設(shè)計(jì)有哪些仿真驗(yàn)證流程

對(duì)話國(guó)產(chǎn)EDA和IP廠商,如何攻克大規(guī)模數(shù)字電路設(shè)計(jì)挑戰(zhàn)?

EDA+IP,攻克大規(guī)模數(shù)字電路設(shè)計(jì)挑戰(zhàn)的“不二法門”

基于FPGA的數(shù)字電路設(shè)計(jì)

基于FPGA的數(shù)字電路設(shè)計(jì)

評(píng)論