1 引言

短波通信是通過電離層反射來實現遠程信息傳輸,因而其通信受地形限制小;其次通信成本低,靈活性強。但它也存在一些缺點,如:信息傳輸的可靠性差,存在深衰落和多徑時延失真等。在一般在短波信道中傳輸數據,信息的誤碼率通常在10-2-10-3的數量級,這些嚴重的衰落以及多徑效應造成的碼間串擾,限制了通信質量的進一步提高。近年來,由于在短波數據通信系統中,采用了各種有效的抗衰落和抗多徑的措施,使系統的誤碼率差不多提高了兩個數量級。其中,時頻組合調制技術(即FTSK)是目前廣泛采用的抗衰落和抗多徑技術之一。針對這種情況,本文提出采用DSP(數字信號處理器)實現4FTSK調制,并取得較好的效果。

2 4FTSK調制方式

在一個或一組二進制符號的持續時間內,用若干個調制頻率的組合來傳送原二進制數據流,每一個調制頻率在不同的時隙內有不同的頻率,這種由不同時隙和不同頻率所構成的信號,稱為“時頻調制信號”;在某種意義上又可看成是一種時頻編碼調制,組成的系統稱頻率分集接收系統,即按一定的規則在數據符號的不同時隙發射不同頻率信號來實現信號傳輸的調制方式。FTSK又可分為幾種調制方式,包括二時二頻制,二進制四時四頻制,四進制四時四頻制、八進制四時四頻制以及十六進制相位調制等。

FTSK碼組的編碼原則是,所編碼組既具有強的抗衰落和抗干擾能力,又容易實現同步,也就是要求編出能從信息序列中提取同步信息的正交碼組。首先,為了提高抗衰落能力,要求每一個碼組的不同時隙中應含有不同的頻率。這樣,二時二頻基本上具有二重頻率分集的效果,而四時四頻基本上具有四重頻率分集的效果;其次,為了加強抗干擾性,任何兩個碼組的碼距應最大,所以首先要選用正交碼,即要求所有的碼組在同一時隙內含有不同的頻率,對于四時四頻制而言,在表示四進制信息時,很容易形成正交碼,但表示八進制信息時,只能形成部分正交的碼組;最后,在碼組配置時還應考慮從碼組本身能提取同步信息,即要求編碼方式是非循環碼,且任何兩個碼組都沒有相同的二聯碼或三聯碼。

表1 各種調制方式性能比較

由表1可以看出,從性能而言,“四進制四時四頻制”是最好的。對于4FTSK調制,我們選用正交編碼方式,如表2所示

表2 4FTSK編碼方式

3 系統的實現

由于本設計的主要目的是利用軟件及簡單的硬件實現4FTSK調制,并且力求產生的信號精確,故系統選用了當今比較流行的數字信號處理器(TI公司的TMS320C5402)和一片D/A(CA3338)轉換芯片,用匯編語言編程實現調制信號輸出。

3.1 TMS320C5402特點

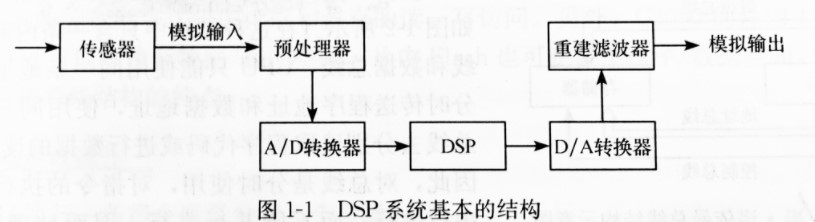

TMS320C5402是TI公司TMS320家族的定點DSP(數字信號處理器)芯片。DSP可廣泛應用于雷達信號處理,無線通信,語音信號處理等。實際上,DSP技術在工程應用中,就是要用數字信號處理的方式實現系統的功能。

DSP器件采用了與傳統微處理器系統不同的總線結構,同時增加了硬件運算單元,把軟件計算變為硬件計算處理,因此極大地提高了系統的數字處理速度。

C5402的CPU通過使用改進的哈佛結構,實現了高度的并行運算能力。同時,多種尋址模式和完善的指令提高了整個系統的性能。C5402主要有以下特點:

增強的哈佛結構,四條地址總線和四條數據總線。

高度并行的先進CPU設計,性能更好的面向應用的硬件邏輯。

為快速算法和高級語言優化設計的專用指令集。

標準化的模塊結構,適于快速開發。

3.2 CA3338芯片性能

CA3338是HARRIS公司推出采用CMOS工藝制成的高速數模轉換器,最高工作頻率可達50M。它可以采用單電源+5V供電,并且能產生“軌對軌”的輸出。

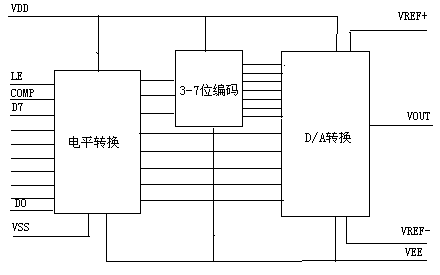

CA3338內部采用改進的R-2R梯形電阻網絡,對高三位進行3位-7位的線性熱編碼來驅動7位加權電阻,這樣,減少了由于輸出電壓值的改變產生的寄生電壓。其內部功能框圖如圖1所示:

圖1 CA3338功能框圖

LE是片選信號,低電平有效。

D0-D7是數字信號輸入端;COMP控制是否對輸入信號的電平取反,高電平有效。

VREF+及VREF-是參考電壓。

VDD接+5V電源,VSS是數字地,VEE可以接模擬地也可以接負電壓。電平轉換部分就是將輸入電壓范圍在VDD和VSS之間的數字信號轉

換到電壓范圍為VDD和VEE之間。

VOUT是輸出的模擬信號。

3.3系統的硬件組成

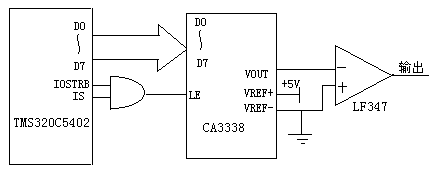

系統的硬件電路框圖如圖2所示。TMS320C5402的IOSTRB和IS相或后作為CA3338的片選信號,通過數據總線將數據送到CA3338中,D/A轉換后的模擬信號經過運算放大器后輸出。

圖2 硬件框圖

3.4系統的軟件設計

3.4.1一個周期的正弦波的產生

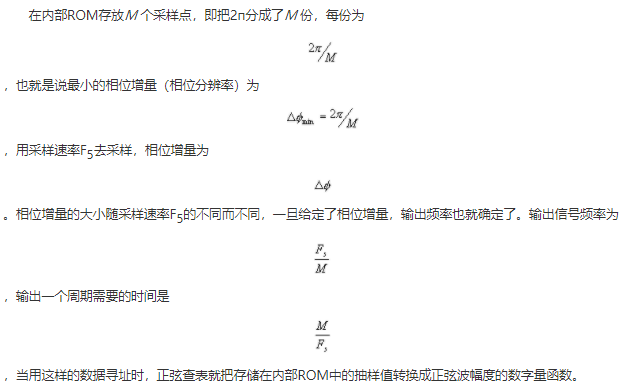

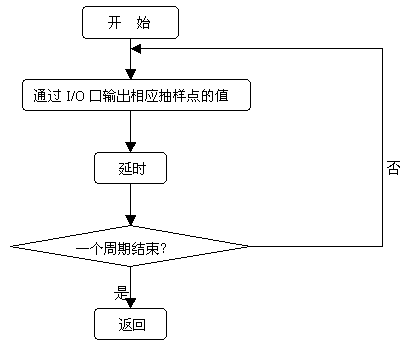

首先,在DSP內部ROM開辟一段存儲空間作為一個周期的正弦波抽樣點存儲器。通過軟件對該存儲器進行相位-幅值的轉換,從而在給定的時間確定相應的輸出幅值。流程圖如圖3所示,具體是這樣實現的:

上面討論可以看出,可以產生的頻率范圍受采樣率和存儲器內采樣點的個數的影響。在這里,采樣率是軟件設計的,即利用不同的延時程序實現不同的采樣率。根據奈魁斯特抽樣定理,一個頻譜受限信號要想從抽樣信號中無失真的恢復出原連續信號,抽樣間隔必須不大于1/2Fm(Fm為最高頻率,在這里Fm即為正弦波的頻率F)或者說,最低抽樣頻率為2F。因此,M應該》=2。但M越大,得到的波形越好。通常情況,為了得到比較好的波形,我們取M》=8。在M一定的情況下,提高F5可以提高輸出的最高頻率。

圖3 發送一個頻率的正弦波流程圖

3.4.2 4FTSK信號的產生及輸出

4FTSK信號包含4個頻率的波形,因此先根據不同的頻率,計算出相應的采樣率,編寫產生這四個頻率正弦波的子程序。在主程序中,判斷要調制的碼元,決定發送的4個頻率的順序。信號最終是通過I/O口輸出到D/A轉換芯片中實現從數字量到模擬量的轉換。

4 結論

本文采用DSP和DA轉換芯片實現4FTSK的調制。由于DSP的運算速度很高,采樣率Fs有很寬的動態范圍,因此它可以在很寬的頻率范圍內輸出幅度平坦的信號。同時,該系統易于集成、易于調整,輸出不同的頻率只需要軟件設置不同的采樣率。這種方式在相對帶寬、頻率轉換時間、相位連續性以及集成化等一系列性能指標方面具有較高的水平,為系統提供了優于模擬信號源的性能。該系統不僅可以實現FTSK調制,也可以通過預置相位累加器的初始值,精確地控制合成信號的相位,實現其他數字調制方式,如DPSK調制等。

責任編輯:gt

-

dsp

+關注

關注

552文章

7962瀏覽量

348269 -

芯片

+關注

關注

453文章

50406瀏覽量

421843 -

無線

+關注

關注

31文章

5430瀏覽量

173084

發布評論請先 登錄

相關推薦

數字信號處理器(DSP)簡介

基于數字信號處理器和和DA轉換芯片實現4FTSK調制

基于數字信號處理器和和DA轉換芯片實現4FTSK調制

評論