受益于集成器件保護,直接驅動GaN器件可實現更高的開關電源效率和更佳的系統級可靠性。

高電壓(600V)氮化鎵(GaN)高電子遷移率晶體管(HEMT)的開關特性可實現提高開關模式電源效率和密度的新型拓撲。GaN具有低寄生電容(Ciss、Coss、Crss)和無第三象限反向恢復的特點。這些特性可實現諸如圖騰柱無橋功率因數控制器(PFC)等較高頻率的硬開關拓撲。由于它們的高開關損耗,MOSFET和絕緣柵雙極晶體管(IGBT)實現此類拓撲。本文中,我們將重點介紹直接驅動GaN晶體管的優點,包括更低的開關損耗、更佳的壓擺率控制和改進的器件保護。

簡介

在設計開關模式電源時,主要品質因數(FOM)包括成本、尺寸和效率。[1]這三個FOM是耦合型,需要考慮諸多因素。例如,增加開關頻率可減小磁性元件的尺寸和成本,但會增加磁性元件的損耗和功率器件中的開關損耗。由于GaN的寄生電容低且沒有二極管反向恢復,因此與MOSFET和IGBT相比,GaN HEMT具有顯著降低損耗的潛力。

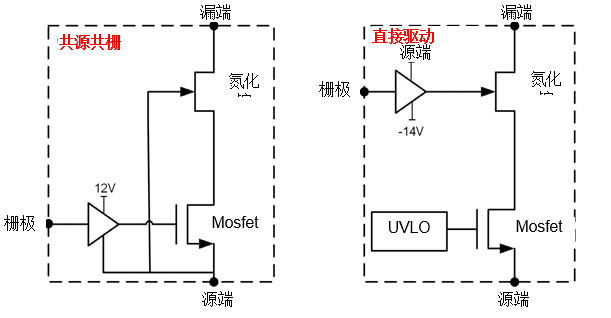

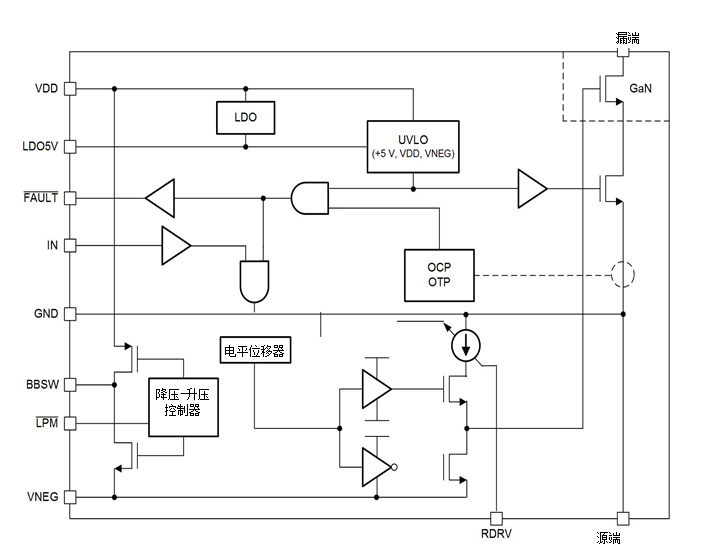

圖1:共源共柵驅動和直接驅動配置

通常來講,MOSFET/IGBT驅動提供合適的導通和關斷電流,以支持輸入電容。驅動輸出和設備柵極之間的外部電阻控制壓擺率,并抑制功率和柵極環路振鈴。隨著GaN壓擺率增加,外部組件增加了過多的寄生電感,無法控制開關。將驅動與GaN器件集成到封裝中可最大程度降低寄生電感、降低開關損耗并優化驅動控制。

直接驅動優點

漏端和漏端之間的GaN中存在本征二維電子氣層(2-DEG),使該器件在零柵極-漏端電壓下導電。出于安全原因,沒有偏置電源時,必須關閉開關電源中使用的電源器件,以將輸入與輸出斷開。為模擬增強模式器件,將低壓MOSFET與GaN源端串聯放置。圖1所示為實現此目的的兩種不同配置:共源共柵驅動和直接驅動。

現在,我們將對比功耗,并描述與每種方法相關的警告所涉及的問題。

在共源共柵配置中,GaN柵極接地,MOSFET柵極被驅動,以控制GaN器件。由于MOSFET是硅器件,因此許多柵極驅動可用。但由于在GaN器件關閉之前必須將GaN柵極至漏端電容(Cgs)和MOSFET Coss充電至GaN閾值電壓,因此該配置具有較高的組合Coss。

在直接驅動配置中,MOSFET是一個直接驅動配置,由柵極驅動器在接地和負電壓(VNEG)之間驅動的GaN柵極導通/關斷組合器件。此外,MOSFET Coss無需充電。關斷GaN Cgs的電流來自較低的偏壓電源。較低的電源電壓可提供相同的GaN柵極至漏端電荷(Qgs),從而可降低功耗。這些功率效率差異在更高的開關頻率下會進一步放大。

反向恢復Qrr損失對于共源共柵配置有效。這是因為在第三象限導通中,MOSFET關斷,并通過體二極管導通。

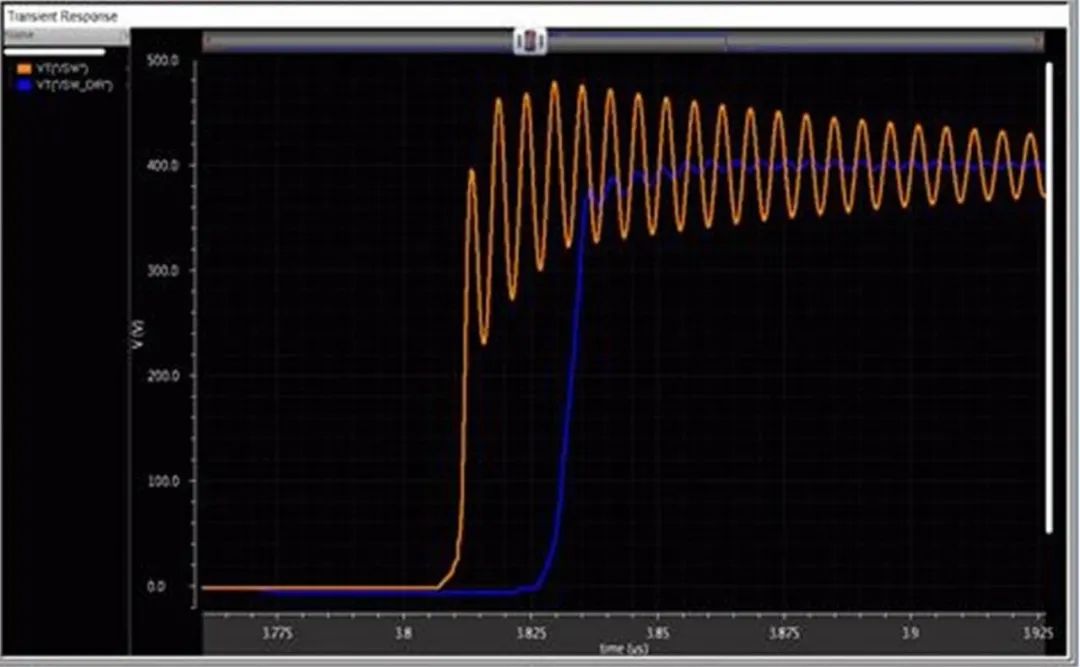

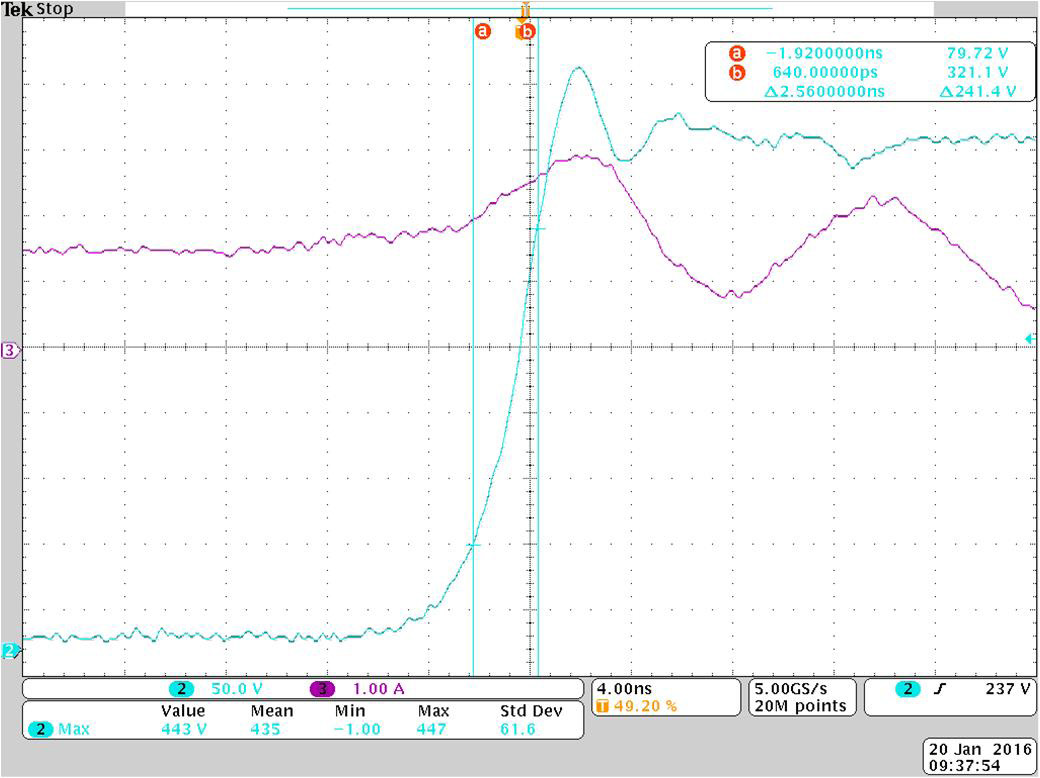

圖 2:硬切換操作導致過多振鈴

由于負載電流反向流動,因此MOSFET中存儲了電荷。克服反向恢復電荷的電流來自高電壓電源,這會導致大量電損失。但在直接驅動配置中,MOSFET始終處于導通狀態,且由于其RDSON低,其寄生二極管也不會導通。因此,最終在直接驅動配置中不會出現與Qrr相關的功率損耗。

在共源共柵配置中,由于GaN漏源電容高(Cds)[2,3],處于關斷模式的GaN和MOSFET之間的電壓分布會導致MOSFET雪崩。可在MOSFET的漏端和漏端之間并聯一個電容器[4]予以解決。但這僅適用于軟開關應用,并在硬開關應用中導致高功率損耗。

鑒于GaN柵極已連至MOSFET的漏端,因此無法控制共源共柵驅動中的開關壓擺率。在硬開關操作中,來自GaN Cgs、MOSFET Coss、MOSFET Qrr的有效Coss的增加,以及由于防止MOSFET崩潰而可能產生的一些電流導通,可能會在初始充電期間導致較高的漏端電流。較高的漏端電流會導致共源共柵驅動中的較高功率損耗。

在MOSFET的漏端充電至足以關閉GaN器件的程度后,從漏端觀察到Coss突然下降——加上流經功率環路電感的漏端電流較高——導致共源共柵中開關節點的過度振鈴組態。硬開關事件期間的開關波形如圖2所示(橙色軌線=共源共柵驅動;藍色跡線=直接驅動)。在此模擬中,即使直接驅動配置的壓擺率較低且振鈴較少(直接驅動在50 V/ns時為4.2 W,而共源共柵驅動在150 V/ns時為4.6 W,所有負載電流均為5A),直接驅動配置每次硬開關耗散的能量卻更少。

另一方面,直接驅動配置在開關操作期間直接驅動GaN器件的柵極。無偏置電源時,MOSFET柵極被拉至接地,并以與共源共柵配置相同的方式關閉GaN器件。一旦存在偏置電源,MOSFET保持導通狀態,其寄生電容和體二極管從電路中移出。直接驅動GaN柵極的優點在于可通過設置對GaN柵極充電的電流來控制壓擺率。

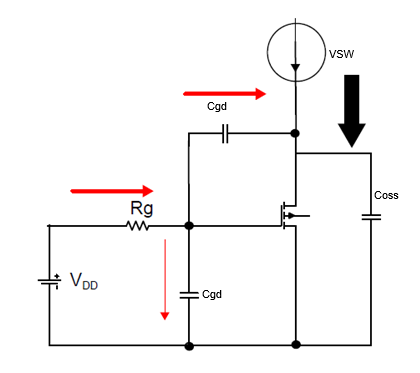

圖3:直接驅動配置的驅動路徑模型

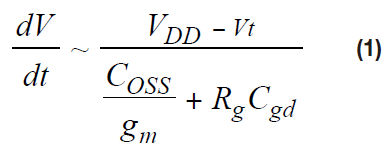

對于升壓轉換器,驅動電路的簡易模型如圖3所示。可使用該模型推導公式[1]。

等式1證明:當GaN器件具有足夠的柵漏電容(Cgd)時,可通過使用柵極電流通過米勒反饋來控制開關事件的壓擺率。對于低Cgd器件,將丟失反饋,且器件的跨導(gm)控制壓擺率。

直接驅動配置的另一個優點在于可在柵極環路中增加阻抗,以抑制其寄生諧振。抑制柵極環路還可減少電源環路中的振鈴。這降低了GaN器件上的電壓應力,并減少了硬開關期間的電磁干擾(EMI)問題。

圖2是一個模擬圖,顯示以功率和柵極環路寄生電感為模型的降壓轉換器中開關節點振鈴的差異。直接驅動配置具有受控的導通,且過沖很少。而共源共柵驅動由于較高的初始Coss、Qrr和較低的柵極環路阻抗而具有較大的振鈴和硬開關損耗。

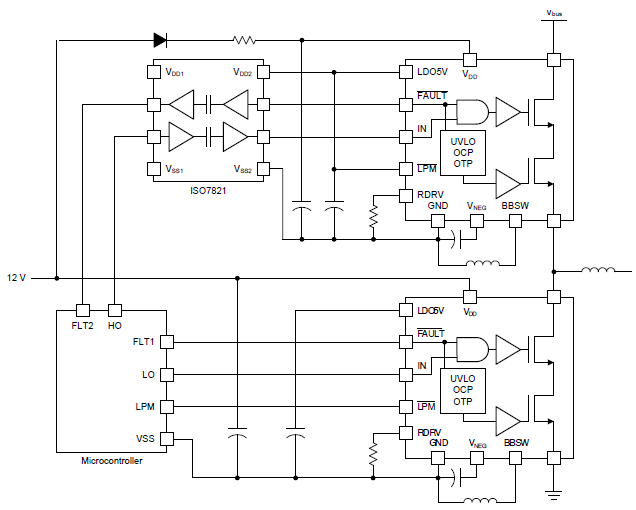

集成柵極驅動的75mΩGaN器件

TI的LMG341x系列600V GaN器件是業界領先的集成GaN FET外加驅動器和保護功能的器件。它是一個8mm x 8mm四方扁平無引線(QFN)多芯片模塊(MCM),包括一個GaN FET和具有集成20V串聯FET的驅動。RDSON 的總電阻為75mΩ。

該器件的框圖如圖4所示。柵極驅動器提供GaN FET的直接驅動能力,并具有內置的降壓-升壓轉換器,以產生關閉GaN FET所需的負電壓。柵極驅動使用12V單電源供電,并具有一個內部低壓差穩壓器(LDO),可產生一個5V電源,為驅動和其他控制電路供電。內部欠壓鎖定(UVLO)電路使安全FET保持關閉狀態,直至輸入電壓超過9.5V。一旦UVLO超過其自身閾值,降壓/升壓轉換器就會接通并對負電源軌(VNEG)充電。一旦VNEG電源電壓超過其自身的UVLO,驅動器便會啟用驅動。

與分立的GaN和驅動器相比,LMG341x系列的集成直接驅動實現具有諸多優勢。柵極驅動的一個重要方面是在硬開關事件期間控制壓擺率。LMG341x系列使用可編程電流源來驅動GaN柵極。

圖4:單通道600 V,76ΩGaN FET功率級的框圖

電流源來驅動GaN柵極。電流源提供阻抗以抑制柵極環路,并允許用戶以受控的方式對轉換率進行編程,轉換率從30 V/ns到100 V/ns,以解決電路板寄生和EMI問題。

通過將串聯FET集成到驅動集成電路(IC)中,感測FET和電流感測電路可為GaN FET提供過流保護。這是增強整體系統可靠性的關鍵功能。使用增強型GaN器件時,這種電流檢測方案無法實現。當大于40 A的電流流經GaN FET時,電流保護電路會跳閘。GaN FET在發生過流事件后的60 ns內關閉,從而防止裸片過熱。

通過將驅動芯片封裝在與GaN FET相同的裸片附著墊(DAP)上,驅動芯片處的引線框架可感測GaN器件的溫度。驅動可通過在過熱事件期間禁用GaN驅動來保護器件。集成的GaN器件還提供FAULT輸出,通知控制器由于故障事件而停止了開關。

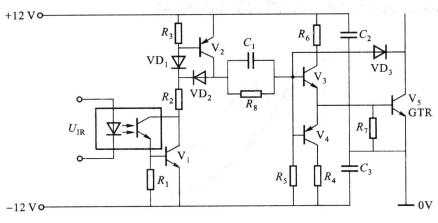

為使用直接驅動方法驗證操作,我們建立了一個半橋板,并將其配置為降壓轉換器(圖5)。此外,我們使用了ISO7831 雙向電平位移器來饋送高側驅動信號,并返回經過電平位移的FAULT信號。

圖 5:典型的半橋配置

圖6中,GaN半橋配置從480V總線、以1.5A的轉換速率轉換為100V/ns。藍色跡線是開關節點波形,紫色跡線是電感器電流。

硬開關導通穩定,具有約50 V的過沖。此波形使用1 Ghz示波器和探頭進行采集,可觀察到任何高頻振鈴。快速的導通時間,外加減小的寄生電容和缺反向恢復電荷,使得基于GaN的半橋配置即使在使用硬開關轉換器時也可高效開關。

圖 6:降壓開關波形示例

總結

GaN在減小寄生電容和無反向恢復方面所提供的優勢為使用硬開關拓撲結構同時保持高效率提供了可能。需要受控的高開關壓擺率來更大程度地發揮GaN的優勢,而這又需要優化的共封裝驅動器和精心的電路板布局技術。

共封裝驅動有助于更大程度地減少柵極環路寄生效應,以減少柵極振鈴。

利用精心布置的印刷電路板(PCB),優化的驅動器可使設計人員以更小的振鈴和EMI來控制開關事件的轉換速率。這得益于GaN器件的直接驅動配置而非級聯驅動配置。

LMG341x系列器件使設計人員能夠以30 V/ns至100 V/ns的壓擺率控制各類器件的開關。此外,驅動器還提供過流、過熱和欠壓保護。

-

晶體管

+關注

關注

77文章

9635瀏覽量

137858 -

GaN

+關注

關注

19文章

1919瀏覽量

73010 -

集成器件

+關注

關注

0文章

20瀏覽量

9157

原文標題:一文掌握 GaN 器件的直接驅動配置!

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶體管的輸出特性是什么

NMOS晶體管和PMOS晶體管的區別

CMOS晶體管和MOSFET晶體管的區別

晶體管的主要材料有哪些

GaN晶體管的應用場景有哪些

GaN晶體管和SiC晶體管有什么不同

GaN晶體管的基本結構和性能優勢

PNP晶體管符號和結構 晶體管測試儀電路圖

晶體管功率繼電器的基本介紹

電力晶體管的產品特點 電力晶體管的驅動保護

什么是達林頓晶體管?達林頓晶體管的基本電路

Si晶體管的類別介紹

直接驅動GaN晶體管的優點

直接驅動GaN晶體管的優點

評論