近期,英特爾舉辦了“架構(gòu)日”活動,發(fā)布了一系列重磅技術(shù)。在這次“架構(gòu)日”的活動中,英特爾六大技術(shù)支柱推出全面、實質(zhì)性的新進展,為英特爾構(gòu)造產(chǎn)業(yè)最具領(lǐng)導(dǎo)力的產(chǎn)品再添“利器”。

英特爾六大技術(shù)支柱指的是制程&封裝、架構(gòu)、內(nèi)存&存儲、互連、安全和軟件,依靠這六大技術(shù)支柱,英特爾的技術(shù)更具靈活性,并且能夠快速為客戶提供具備領(lǐng)導(dǎo)力的產(chǎn)品。英特爾中國研究院院長宋繼強在近期接受媒體的采訪中表示:“在目前的環(huán)境下,產(chǎn)品種類眾多,有云、邊緣計算、各類智能設(shè)備,并且要求快速給出方案,因此英特爾要依靠多個領(lǐng)域的技術(shù),即我們的六大技術(shù)支柱,組合起來形成產(chǎn)品的領(lǐng)導(dǎo)力,并能夠快速達到客戶需要的性能要求,增強客戶對我們的信心。”

圖注:英特爾六大技術(shù)支柱

對于英特爾來說,能夠為客戶快速提供具備領(lǐng)導(dǎo)力的產(chǎn)品是終極目標,而六大技術(shù)支柱是實現(xiàn)這樣目標的重要“根基”。在六大技術(shù)支柱中,每一個支柱都很關(guān)鍵,所發(fā)揮的作用都無可取代。

制程是基礎(chǔ),封裝在“異軍突起”

制程工藝是非常重要的基礎(chǔ)。在今年“架構(gòu)日”上,英特爾推出了創(chuàng)新的晶體管技術(shù)SuperFin。這項技術(shù)擁有行業(yè)顛覆意義,英特爾在底層晶體管設(shè)計上做了優(yōu)化,降低了電阻,提高了電流,同時在電容層級采用了Super MIM的大幅優(yōu)化技術(shù),電容量提高了5倍,同時降低了壓降。

與上一代10納米相比,SuperFin所帶來的性能提升超越了15%。 宋繼強表示:“我們14納米節(jié)點,每一次性能提升是5%左右,SuperFin所帶來的性能提升在以前是可以作為一次跨越節(jié)點提升的。”

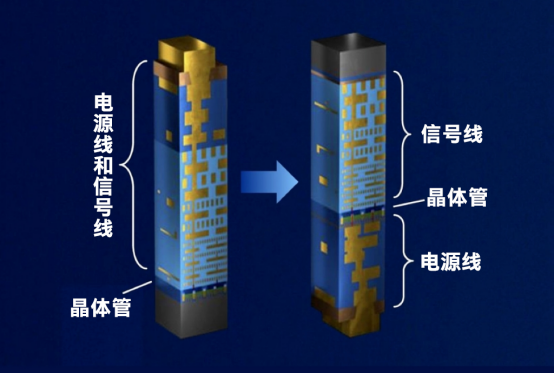

封裝技術(shù)也在“異軍突起”,英特爾在封裝領(lǐng)域有多種維度的先進封裝技術(shù),并且處于業(yè)界領(lǐng)先地位。英特爾有標準封裝、2.5D的EMIB、3D的Foveros以及在今年“架構(gòu)日”上推出的Hybrid Bonding(混合結(jié)合)技術(shù),可以把凸點間距降到10微米以下,帶來更高的互連密度、帶寬和更低的功率。這些封裝技術(shù)還可以相互疊加,疊加后能夠帶來更大的擴展性和靈活性。例如,Co-EMIB技術(shù)就是把2.5D的EMIB技術(shù)和3D的Foveros封裝技術(shù)進行整合。

“封裝技術(shù)的發(fā)展就像我們蓋房子,一開始蓋的是茅廬單間,然后蓋成四合院,最后到高樓大廈。以Foveros 3D來說,它所實現(xiàn)的就是在建高樓的時候能夠讓線路以低功率同時高速率地進行傳輸,” 宋繼強表示。“英特爾在封裝技術(shù)持續(xù)投資,因為它的優(yōu)勢在于我們可以更早地知道,未來這個房子會怎么搭,也就是說可以更好地對未來芯片進行設(shè)計。”

面向未來異構(gòu)計算的大趨勢,英特爾在今年的“架構(gòu)日”上推出了“分解設(shè)計”策略,這是一種結(jié)合新的設(shè)計方法,如晶片分解,以及先進的封裝技術(shù),將關(guān)鍵的架構(gòu)組件拆分為仍在統(tǒng)一封裝中單獨晶片的解決方案。宋繼強表示,分解設(shè)計就是把原先的整個SoC芯片由大變小,“化整為零”,先把它做成幾個大的部分,比如CPU、GPU、I/O,再將SoC的細粒度進一步提升,將以前按照功能性來組合的思路,轉(zhuǎn)變?yōu)榘凑站琁P來進行組合。這些分解開的小部件整合起來之后,速度快、帶寬足,同時還能實現(xiàn)低功耗,有很大的靈活性,將成為英特爾的一大差異性優(yōu)勢。

相對于以前的芯片整體設(shè)計思路,分解設(shè)計的好處在于,不僅能夠提升芯片設(shè)計的效率、降低產(chǎn)品化的時間,并且能夠有效減少此前復(fù)雜設(shè)計所帶來的Bug數(shù)量。“原來一定要放到一個晶片上做的方案,現(xiàn)在可以轉(zhuǎn)換成多晶片來做。另外,不僅可以利用英特爾的多節(jié)點制程工藝,也可以利用合作伙伴的工藝,”宋繼強解釋。“這樣可以給客戶更多選項,在每個選項下面可以選擇最好的不同部件的組合,不管是to C還是to B的需求,都可以快速開發(fā)多種不同產(chǎn)品方案給客戶,而不是說芯片都必須要在單一節(jié)點內(nèi)實現(xiàn)。”

XPU架構(gòu) & oneAPI軟件,真正釋放硬件潛能

在“萬物智能化”的時代下,數(shù)據(jù)量呈指數(shù)級增長,我們有大量的數(shù)據(jù)和處理需求,有的要實時,有的要稀疏,有的要并行,有的需要矩陣,所以說一個架構(gòu)“包打天下”的時代已經(jīng)過去,應(yīng)對不同的數(shù)據(jù)需要采用不同種類的芯片架構(gòu),因此英特爾提出了XPU架構(gòu),這個“X”指的是至少會包含CPU、GPU、專用加速器以及FPGA的混合架構(gòu),從而處理部署的標量、矢量、矩陣和空間架構(gòu)數(shù)據(jù)。

英特爾的GPU架構(gòu)也迎來重大更新,全新的Xe架構(gòu)最大的特點是高度可擴展。它同時擁有性能向上增長(Scale Up)以及向外拓展(Scale Out)的能力。性能向上增長指的是單個GPU構(gòu)造組件區(qū)塊(Tile)性能能夠提升,內(nèi)部也有多個EU執(zhí)行單元。向外拓展指的是可以構(gòu)建多個區(qū)塊(Tile),并根據(jù)不同的任務(wù)規(guī)模去組合,在架構(gòu)上充分體現(xiàn)了靈活性,以及可以在未來增加一些新的加速部件。

宋繼強認為,要真正獲得硬件異構(gòu)之后的超級性能提升,沒有好的軟件是不行的。如果軟件能夠根據(jù)不同領(lǐng)域的工作負載進行優(yōu)化,性能提升可以高達十倍甚至是百倍,而英特爾oneAPI就擔負了這樣艱巨的重任。作為跨XPU架構(gòu)統(tǒng)一編程模型,oneAPI是一個開放的產(chǎn)業(yè)聯(lián)盟,它包含工具鏈、性能庫、編譯器、調(diào)試、編程、程序移植等,可以幫助開發(fā)人員有效減少跨架構(gòu)程序開發(fā)時間和成本。

“架構(gòu)和軟件,這兩個是要搭配的,架構(gòu)要體現(xiàn)出不同的架構(gòu)都能玩的轉(zhuǎn),同時做出來的硬件還要能讓別人用軟件快速使用。如果新的架構(gòu)出來,沒有一個很好的軟件能夠把它生態(tài)化,那就還是起不來,” 宋繼強表示。“所以除了要有很好的架構(gòu)掌控能力,還需要軟件能夠把這些好處暴露出來,XPU & oneAPI未來會成為英特爾突出的特點。”

再“乘以”內(nèi)存和存儲、互連和安全,英特爾綜合實力爆棚

同時,作為計算不可或缺的部分,內(nèi)存和存儲,互連以及安全技術(shù)也是英特爾“六大技術(shù)支柱”的重要組成部分。

根據(jù)宋繼強的介紹,在原來三級存儲模式中,每一級之間的速度差是百倍,容量差別也是百倍到千倍,因此在高性能計算中,會造成很大的性能損失,因此要填補這個差距,通過內(nèi)存和存儲技術(shù)提升計算性能。英特爾最新發(fā)布的3D NAND已經(jīng)可以達到144層,當內(nèi)存使用的XPoint也從之前的2-Deck增長到了4-Deck,屬于國際領(lǐng)先的技術(shù)。

“互連”技術(shù)也是重要的技術(shù)之一。因為要把不同的設(shè)備連在一起,把不同的芯片連在一起,連接距離小到微米級,大到公里級,甚至是數(shù)百公里級,在客戶端產(chǎn)品以及數(shù)據(jù)中心產(chǎn)品都會涉及。英特爾最新的互連技術(shù)在提升帶寬的同時,還能夠減輕體積和降低功耗。在安全方面,英特爾的控制流強制技術(shù)(CET)為計算帶了更好地安全保護,避免通過控制流返回跳轉(zhuǎn)攻擊軟件漏洞。

“當我們把這些技術(shù)全部乘在一起的時候,英特爾就構(gòu)建出一個以XPU為上層架構(gòu),中間以各種級別的內(nèi)存作為支撐,底部是從云到端的完整產(chǎn)品布局,從而產(chǎn)生各種各樣快速創(chuàng)新的能力,并且能夠和產(chǎn)業(yè)界分享,” 宋繼強表示。

總結(jié)來看,英特爾六大技術(shù)支柱包含的內(nèi)容涉及到計算的各個方面,所帶來的綜合實力在業(yè)界內(nèi)獨樹一幟,具有其他廠商不可比擬的優(yōu)勢。在制程工藝逼近極限之際,未來半導(dǎo)體行業(yè)的比拼一定是綜合實力的比拼,制勝的關(guān)鍵點就在于能否為客戶又快又好地提供產(chǎn)品,解決在數(shù)據(jù)大爆發(fā)的現(xiàn)狀下,能否實現(xiàn)指數(shù)級增長的挑戰(zhàn)。英特爾的六大技術(shù)支柱已經(jīng)打下了非常堅實的基礎(chǔ),必將助力英特爾繼續(xù)行穩(wěn)致遠。

責任編輯:pj

-

芯片

+關(guān)注

關(guān)注

454文章

50438瀏覽量

421903 -

英特爾

+關(guān)注

關(guān)注

60文章

9891瀏覽量

171538 -

晶體管

+關(guān)注

關(guān)注

77文章

9637瀏覽量

137864

發(fā)布評論請先 登錄

相關(guān)推薦

技術(shù)前沿:“環(huán)抱”晶體管與“三明治”布線

英特爾是如何實現(xiàn)玻璃基板的?

英特爾推進面向未來節(jié)點的技術(shù)創(chuàng)新,在2025年后鞏固制程領(lǐng)先性

英特爾逐步停止Ponte Vecchio GPU生產(chǎn),專注于Gaudi 2/3產(chǎn)品

Ansys多物理場簽核解決方案獲得英特爾代工認證

借助英特爾DLB技術(shù)優(yōu)化網(wǎng)絡(luò)性能

英特爾押注18A制程,力爭重回技術(shù)領(lǐng)先地位

英特爾3D封裝工藝進入量產(chǎn),集成萬億晶體管

英特爾:2030年前實現(xiàn)單個封裝內(nèi)集成1萬億個晶體管

英特爾CEO基辛格:摩爾定律放緩,仍能制造萬億晶體

英特爾深度解析其芯片技術(shù)創(chuàng)新,引領(lǐng)全球芯片科技潮流

英特爾展示下一代晶體管微縮技術(shù)突破,將用于未來制程節(jié)點

英特爾宣布完成PowerVia背面供電技術(shù)的開發(fā)

英特爾采用Super MIM優(yōu)化技術(shù)推出晶體管技術(shù)SuperFin

英特爾采用Super MIM優(yōu)化技術(shù)推出晶體管技術(shù)SuperFin

評論