首先要解釋一下耦合,耦合就是互相影響,正如變壓器的原邊會影響副邊,同時副邊也會影響原邊。比如我們在做高速電路設計的時候,為什么要有那么多去耦電容?到底什么是去耦?到底需要多大的去耦電容呢?為什么是很多個小電容并聯而不是用一個大電容(值是一樣大的啊)?為什么說小電容要靠近電源管腳而大電容可以遠一些?這里的這些問題,涉及到很多信號完整性問題。

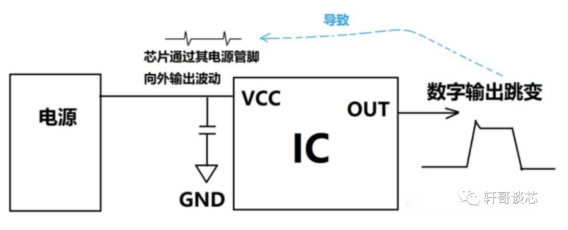

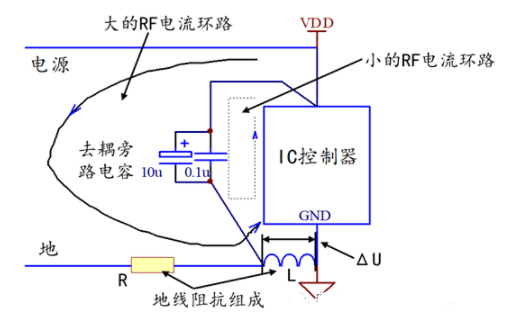

那么去耦,就是減少耦合,減少互相影響。其實這里的去耦電容跟濾波電容的意思是一樣的。但是為什么要另起一個名字呢?電源分布系統PDS的目標是為每個芯片的電源和地引腳提供恒定可靠范圍的工作電壓,通常噪聲預算的波動小于5%。由于PDS和具體的芯片之間會有許多過孔、封裝引線、不同的電源平面等,當高速電路時鐘沿到來變化,進行門電路切換等時,由于V=L*di/dt,由于門電路切換非常快,di/dt將會很大,即便是很小的回路電感也會感應出比較大的感應電壓,這個就是“地彈”。

另外,變化的電流經過PDS的互連線的阻抗時引起電壓降,這個就是“軌道塌陷”。有了這個理論基礎之后,我們就可以明確去耦的目的,去耦電容的目的就是為了盡量減小這兩種作用對電壓的影響。低頻時,添加低阻抗的電容來提供電荷補給。高頻時,回路電感影響會比較大,所以在電容的擺放位置,容值大小,ESL上的選擇要盡量使回路電感低。于爭博士在他的書和文章里曾經提到去耦的兩種解釋,我個人理解上,覺得這兩種解釋對應的分別是低頻和高頻兩種情況,但本質上都是希望減小PDN上的電壓突變,這就是去耦。

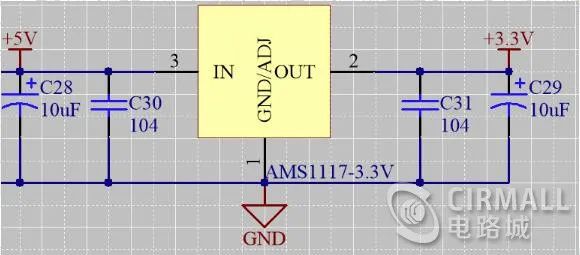

如上圖所示,一個LDO的輸入和輸出各加了兩個電容,分別是104和10uF。

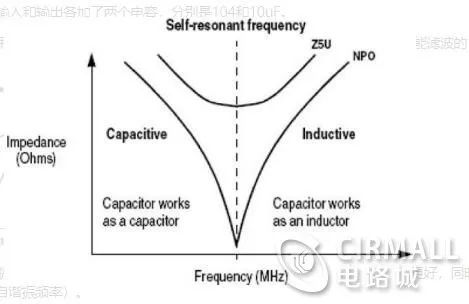

顯然電容是具有濾波的作用,但是這跟模電上的RC、LC、RLC濾波不一樣,只有一個C,這樣也能濾波的,濾波的頻率叫自諧振頻率。

上圖中,NPO電容的自諧振頻率呈V字形,而Z5V電容則呈U字形,說明了NPO電容的濾波特性更好,同時,也最容易濾掉虛線對應的頻率(就是自諧振頻率)。

此外,電容工作在虛線左邊的頻率范圍內,呈電容的特性,而虛線右邊,則呈電感的特性。

-

電壓

+關注

關注

45文章

5429瀏覽量

115131 -

PDS

+關注

關注

2文章

28瀏覽量

15223 -

去耦電容

+關注

關注

11文章

313瀏覽量

22259

原文標題:每日一練#去耦電容的作用

文章出處:【微信號:cirmall,微信公眾號:電路設計技能】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

去耦電容的擺放位置和作用

旁路電容和去耦電容在晶振電路中的作用

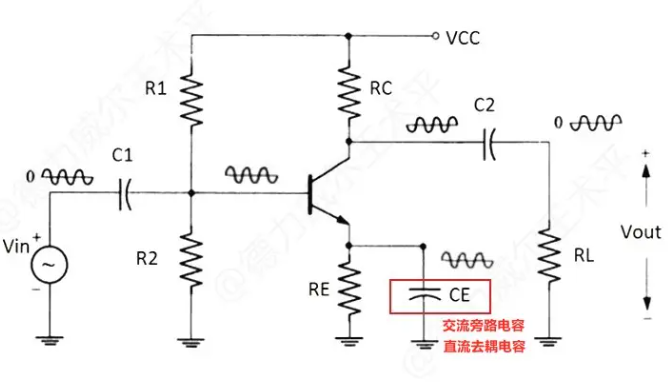

三極管放大電路中旁路(去耦)電容的作用

什么是去耦電容 有什么作用

去耦電容越大越好嗎,去耦電容值的選擇

分享PCB中的去耦電容設計

去耦電容的作用

去耦電容的作用

評論