在我與客戶交流時,常被問到這個問題。也許措辭并非完全如此,但大致是下面這樣:“為什么我要升級到 VersalACAP?現(xiàn)在是時候這樣做了嗎?” 這是一個很好的問題,而且答案也很簡單,那就是——“具體情況具體分析”。 好吧,也許這樣的答案根本不簡單!公正地說,有諸多因素需要考慮,包括設(shè)計要求/資源、設(shè)計能在多大程度上利用 Versal ACAP 中數(shù)量龐大的硬 IP、庫和軟 IP 可用性、芯片可用性、生產(chǎn)時限等。 因此,具體答案確實會隨著相關(guān)因素的變化而發(fā)生改變。我們將在今后的博文中探討這些主題,但今天,我想把重點放在“為什么升級到 Versal”這個問題上并提供具體的客戶示例。

認(rèn)識到所有硬 IP 的價值

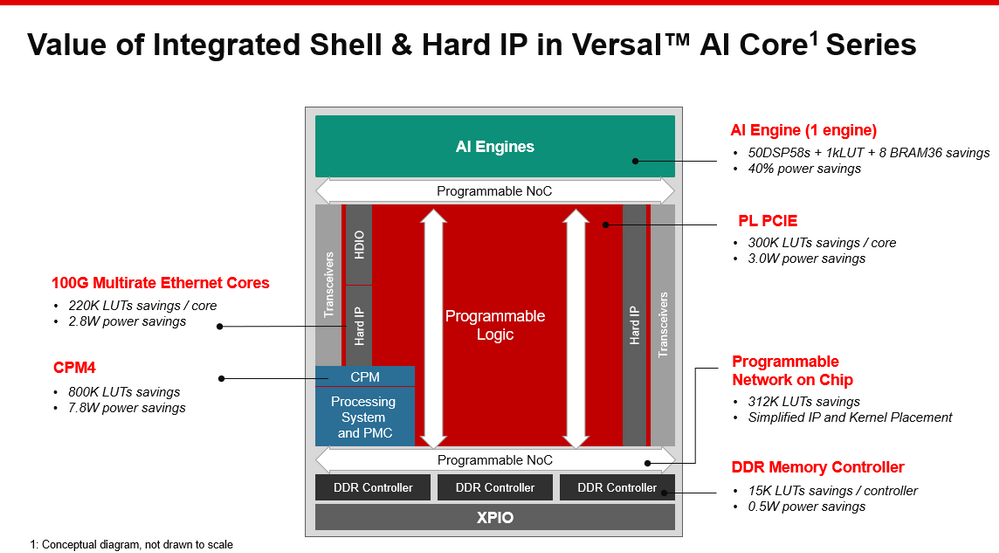

在探討為什么要升級到 Versal ACAP 時,必須首先認(rèn)識到所有硬 IP 的價值,包括存儲控制器、PCIe、多速率以太網(wǎng)和片上可編程網(wǎng)絡(luò)( NoC )等常用基礎(chǔ)設(shè)施的價值,它可以減少對靈活應(yīng)變的引擎或可編程邏輯的路由需求。

一些 Versal 系列還包含 AI引擎(一種非常適合高級信號處理和 ML 算法的新型矢量處理器)、高帶寬存儲器、直接 RF 和高速密鑰。賽靈思將這些 IP 全部硬化的主要原因之一在于,賽靈思在多年前就意識到摩爾定律即將走向終點,僅靠縮小晶體管難以為客戶在每個新的工藝節(jié)點上提供他們所期待的性能提升和功耗下降。

下圖所示的是 Versal AI Core 系列器件中硬 IP 的價值。可以看出,與我們大獲成功的 16nm UltraScale+產(chǎn)品相比,它擁有 LUT 占用大幅降低、功耗顯著下降等多項優(yōu)勢。在 Versal AI Core VC1902 器件中,有望省下多達 360 萬個 LUT。 當(dāng)然,大多數(shù)設(shè)計并不能用到所有硬 IP ,但如果將一個類似設(shè)計移植到 Versal ACAP,就會看到 LUT 占用和功耗的實質(zhì)性降低,而且還可以提供布局布線速度加快、日設(shè)計迭代次數(shù)增加等附加優(yōu)勢。

Versal AI Core 系列中集成外殼程序和硬 IP 的價值 借助 AI 引擎實現(xiàn)高級信號處理 今天我還想重點講解一下 AI 引擎。AI 引擎由數(shù)十個到數(shù)百個(在最大型的 AI Core 系列器件 VC1902 中多達 400 個)專為線性代數(shù)和矩陣數(shù)學(xué)等數(shù)學(xué)功能優(yōu)化的小型 VLIW SIMD 矢量處理器陣列構(gòu)成。當(dāng)人們聽到“AI 引擎”一詞時,往往會自然而然地想到人工智能。 然而,這些功能只是眾多高級信號處理算法(如波束成型和大規(guī)模 MIMO )和機器學(xué)習(xí)推斷算法(如用于圖像分類的卷積神經(jīng)網(wǎng)絡(luò)( CNN ))的基本構(gòu)建塊。有鑒于這一原因,無論是信號處理還是推斷,AI 引擎都能分別提供復(fù)數(shù)數(shù)據(jù)和實數(shù)數(shù)據(jù)支持。

AI 引擎的關(guān)鍵目標(biāo)應(yīng)用之一是 5G 無線系統(tǒng)信號處理。針對一個支持 200MHz 瞬時帶寬 2 的 64 天線系統(tǒng)的波束成型技術(shù),AI 引擎可為其提供 5 倍的計算密度并降低 50% 的功耗。這也引起了領(lǐng)先的 5G 測試測量設(shè)備提供商 Keysight 的關(guān)注。

此外,他們也十分注重開發(fā)生產(chǎn)力。誠然,他們擁有負責(zé)靈活應(yīng)變的引擎硬件編程的專家,但是相比硬件布局布線需要耗費數(shù)個小時, AI 引擎的編譯用時僅需要幾分鐘,這樣一來,他們的 5G 無線算法的設(shè)計與開發(fā)生產(chǎn)力就會顯著提高,每星期便能多完成幾次設(shè)計迭代。

然而,從他們的實現(xiàn)方案原理圖可以看出(參見下圖),Versal ACAP 的系統(tǒng)級價值可謂是決定性的,因為他們能將 AI 引擎的功耗及生產(chǎn)力與靈活應(yīng)變的引擎的靈活性相結(jié)合,創(chuàng)建出令人嘆服的 EVM 演示。

點擊查看大圖 EVM 測量 Tx/Rx 性能及其 IQ 級聯(lián)分析 這僅僅是客戶采用 Versal ACAP 架構(gòu)(特別是 AI 引擎)從而獲得重大效益的示例之一。還有眾多其他客戶在 VC1902 上為 AI 引擎編程,用于 5G、數(shù)據(jù)中心推斷、邊緣推斷原型設(shè)計、雷達、線纜接入等眾多應(yīng)用。

-

引擎

+關(guān)注

關(guān)注

1文章

360瀏覽量

22531 -

存儲控制器

+關(guān)注

關(guān)注

0文章

23瀏覽量

9139 -

Versal

+關(guān)注

關(guān)注

1文章

153瀏覽量

7645

原文標(biāo)題:是否采用 Versal?這是個問題……

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

將Non-OS SDK從1.3.0升級到1.4.0后,AT CWLAP命令將無法再找到我的AP,為什么?

升級到2.0.0后,調(diào)用smartconfig_start()出現(xiàn)Fatal exception重啟的原因?

esp8266怎樣才能正確的把更新的代碼升級到target上?

升級到SDK 2.0,esp8266只會向控制臺打印致命的異常,為什么?

把esp-idf4.3.1下寫的軟件升級到esp-idf5.1.0,編譯老是提示identifier \"xQueueHandle\" is undefined,為什么?

stm32cubemx升級到6.10.0后,不能打開以前版本的文件了,怎么解決?

如何將stm32f207的以太網(wǎng)庫中l(wèi)wip1.3.2升級到1.4.1?

STM32CubeMX版本升級由6.2.1升級到6.3.0后原工程重新編譯code文件變大什么原因?

【愛芯派 Pro 開發(fā)板試用體驗】關(guān)于升級到1.45版本后出現(xiàn)的問題反饋

GitHub底層數(shù)據(jù)庫無縫升級到MySQL 8.0的經(jīng)驗

為什么我要升級到Versal ACAP?

為什么我要升級到Versal ACAP?

評論