來源:半導(dǎo)體行業(yè)觀察

位于加利福尼亞州弗里蒙特的MRAM初創(chuàng)公司Spin Memory表示,它已經(jīng)開發(fā)出一種晶體管,可以大大縮小MRAM和電阻性RAM的尺寸。據(jù)該公司稱,該設(shè)備還可以克服DRAM中一個(gè)名為Row Hammer的頑固安全漏洞。

Spin Memory的垂直環(huán)繞柵晶體管可以縮小MRAM和RRAM存儲(chǔ)單元。

Spin Memory將設(shè)備稱為“通用選擇器”(Universal Selector)。在存儲(chǔ)器單元中,選擇器是用于訪問所述存儲(chǔ)器元件——MRAM中的一個(gè)磁隧道結(jié)。也是RRAM的一種電阻材料RRAM,也就是DRAM的電容器。這些通常內(nèi)置于硅的主體中,而存儲(chǔ)元件則構(gòu)造在其上方。使選擇器更小并簡化與選擇器接觸的互連的布局,可以使存儲(chǔ)單元更緊湊。

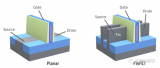

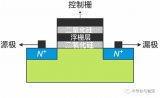

一般而言,晶體管是在硅平面的水平上構(gòu)建的。當(dāng)設(shè)備開啟時(shí),電流流過源極和漏極之間的溝道區(qū)域。通用選擇器使該幾何體傾斜90度。源極在底部與埋在硅中的導(dǎo)體相連,溝道區(qū)域是垂直的硅柱,漏極在頂部。柵極是器件中控制電荷流動(dòng)的部分,四周圍繞著溝道區(qū)離子。

“通用選擇器”就像普通的晶體管一樣,但是傾斜了90度。存儲(chǔ)元件(通常為MRAM)連接到設(shè)備上方的漏極。

這種垂直的gate-all-around 器件類似于用于制造當(dāng)今的多層NAND閃存存儲(chǔ)芯片的器件。但是Spin Memory的設(shè)備僅跨越一層,并且被調(diào)整為在低得多的電壓下運(yùn)行。

據(jù)該公司稱,這種垂直設(shè)備將使DRAM陣列密度提高20%至35%,并使制造商可以在同一區(qū)域內(nèi)將多達(dá)MRAM或RRAM存儲(chǔ)器的容量提高五倍。

選擇器是Spin Memory正在開發(fā)的三項(xiàng)發(fā)明中的一部分,以促進(jìn)MRAM的采用。另外兩個(gè)是改進(jìn)的磁隧道結(jié),以及一種電路設(shè)計(jì),這些都可以提高M(jìn)RAM的耐用性和讀寫速度,并消除錯(cuò)誤源。該公司產(chǎn)品開發(fā)高級副總裁Jeff Lewis表示,這種結(jié)合將使MRAM的性能達(dá)到與SRAM(當(dāng)今CPU和其他處理器中嵌入的超快存儲(chǔ)器)相當(dāng)?shù)乃健?/p>

使用“通用選擇器”可以實(shí)現(xiàn)更緊湊的存儲(chǔ)單元設(shè)計(jì)。

Lewis說:“由于其已知的猥瑣問題,將SRAM用作主要的片上存儲(chǔ)器正成為問題。” 由于MRAM只是一個(gè)晶體管和一個(gè)磁性隧道結(jié),因此有一天可以比由六個(gè)晶體管組成的SRAM具有更高的密度優(yōu)勢。更重要的是,與SRAM不同,即使在存儲(chǔ)單元沒有電源的情況下,MRAM也會(huì)保留其數(shù)據(jù)。但是,目前,MRAM單元比SRAM大得多。“我們的主要目標(biāo)之一是為MRAM設(shè)計(jì)一個(gè)較小的單元,以使其作為SRAM替代品具有更大的吸引力。”

有了DRAM(計(jì)算機(jī)選擇的主要內(nèi)存),通用選擇器具有一個(gè)有趣的副作用:它應(yīng)使內(nèi)存不受 Row Hammer的影響。當(dāng)一行DRAM單元快速充電和放電時(shí),會(huì)發(fā)生此漏洞。(基本上,以極高的速率翻轉(zhuǎn)位。)此操作產(chǎn)生的雜散電荷可以遷移到相鄰的單元格行,從而破壞該位的位。

Row Hammer是DRAM可靠性和安全性的主要問題之一,長期以來一直困擾著存儲(chǔ)器行業(yè)。作為DRAM長期以來的主要干擾問題,隨著單元的縮小, Row Hammer.只會(huì)成為一個(gè)更大的問題,” 思科系統(tǒng)公司設(shè)備可靠性專家Charles Slayman說。

而據(jù)劉易斯稱,由于晶體管通道位于硅主體之外,因此該新器件不受此問題的影響,因此它與漂移電荷隔離。他說:“這是排除Row Hammer的根本原因。”

為了在DRAM中使用,可能必須將設(shè)備縮小很多。但是改善MRAM是近期目標(biāo)。這將涉及優(yōu)化驅(qū)動(dòng)電流和設(shè)備其他方面的強(qiáng)度。

來源:半導(dǎo)體行業(yè)觀察

原文標(biāo)題:熱點(diǎn) | 取代SRAM,MRAM又走近了一步!

文章出處:【微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

sram

+關(guān)注

關(guān)注

6文章

764瀏覽量

114638 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

MRAM

+關(guān)注

關(guān)注

1文章

236瀏覽量

31705

原文標(biāo)題:熱點(diǎn) | ?取代SRAM,MRAM又走近了一步!

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

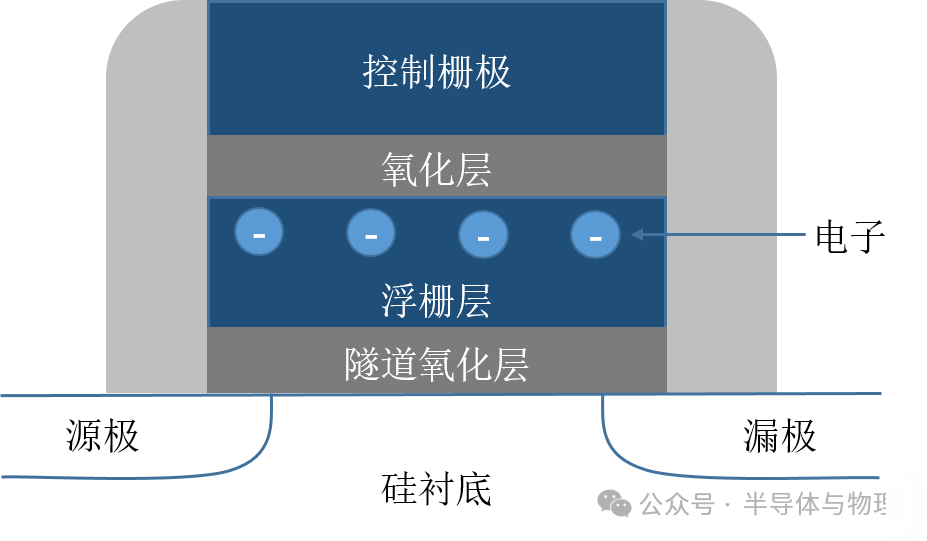

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

NMOS晶體管和PMOS晶體管的區(qū)別

存儲(chǔ)單元和磁盤有什么區(qū)別

存儲(chǔ)單元是指什么

eeprom存儲(chǔ)器為什么會(huì)重?zé)?/a>

降壓開關(guān)穩(wěn)壓器如何使用串聯(lián)晶體管

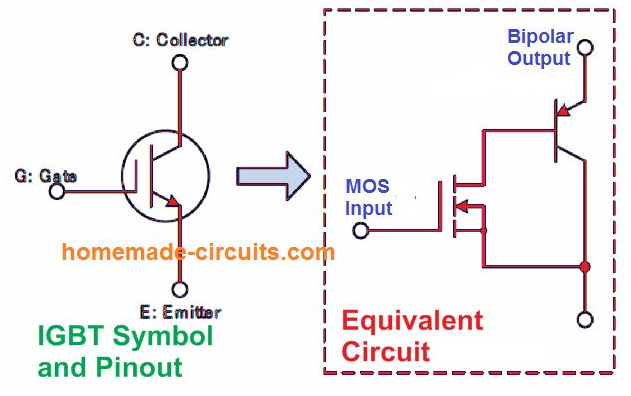

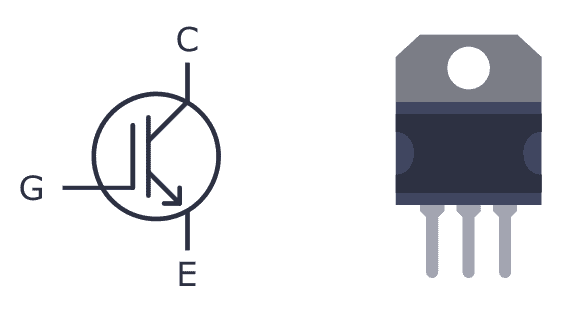

絕緣柵雙極晶體管的工作原理和結(jié)構(gòu)

絕緣柵雙極晶體管的實(shí)用指南

有什么方法可以提高晶體管的開關(guān)速度呢?

如何去識(shí)別IGBT絕緣柵雙極型晶體管呢?

MRAM(磁性只讀存儲(chǔ)器)和FRAM(鐵電RAM)有何區(qū)別

絕緣柵雙極型晶體管是什么

晶體管是怎么做得越來越小的?

探討晶體管尺寸縮小的原理

垂直環(huán)繞柵晶體管可縮小MRAM和RRAM存儲(chǔ)單元!

垂直環(huán)繞柵晶體管可縮小MRAM和RRAM存儲(chǔ)單元!

評論