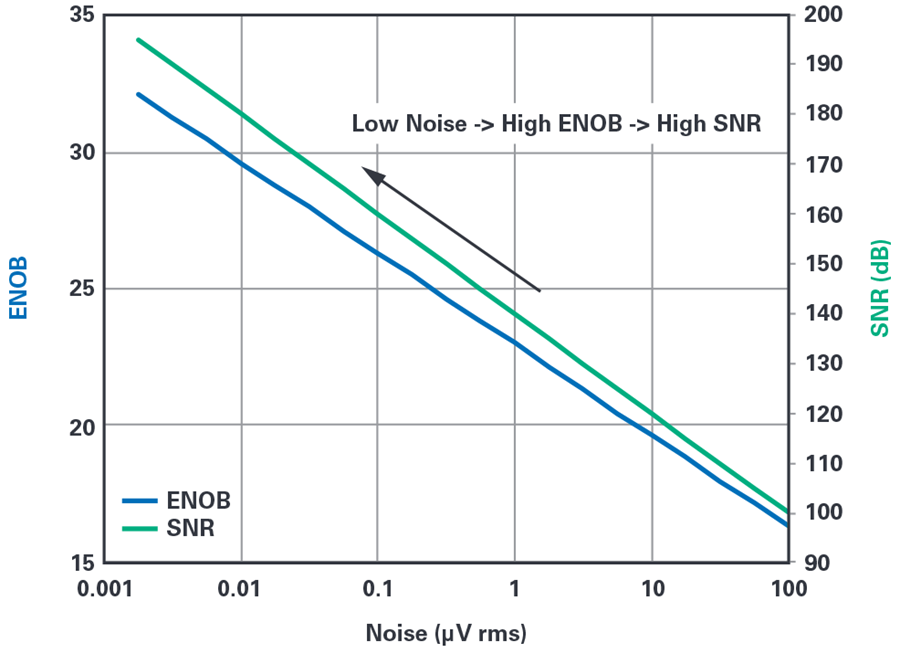

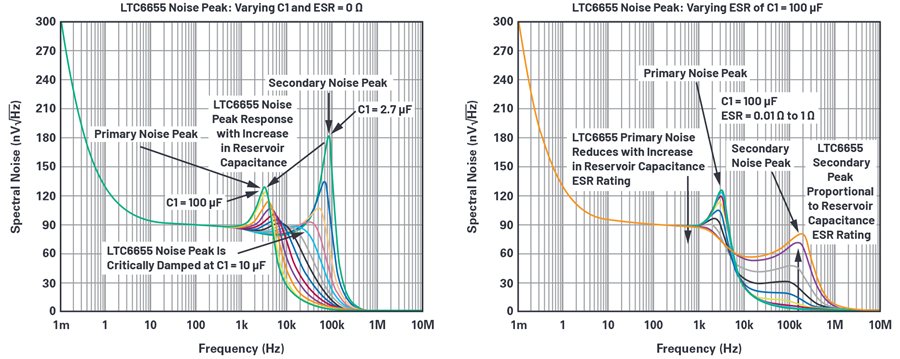

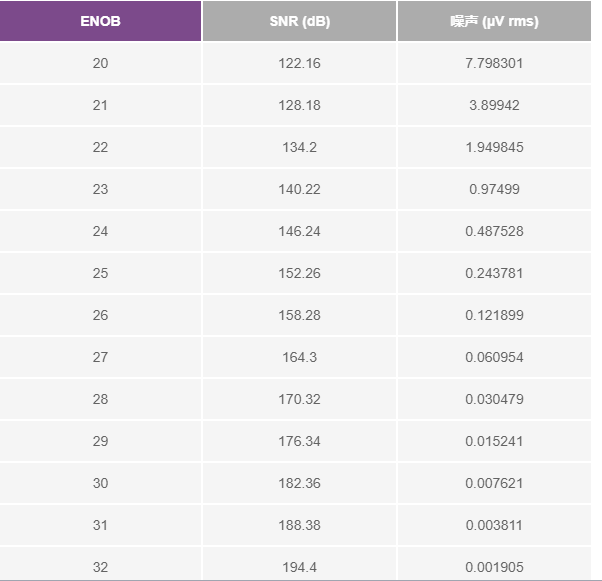

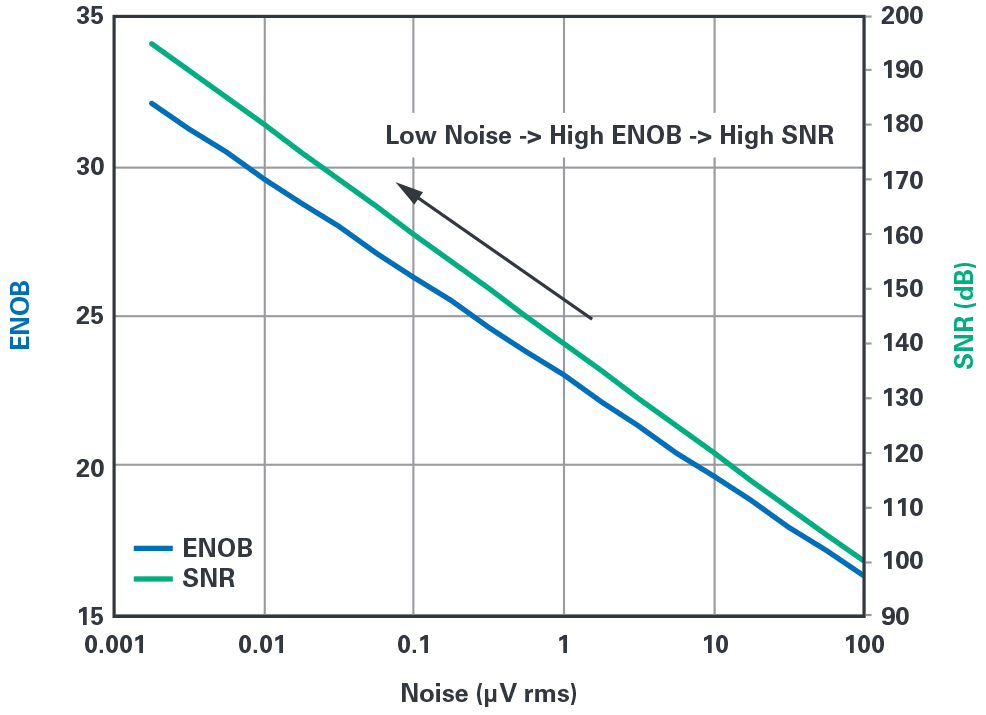

為了實現這種高分辨率,需要使用低噪聲信號鏈。圖1顯示噪聲與有效位數(ENOB)和信噪比(SNR)之間的關系。注意,噪聲是基于基準電壓(VREF) =5V,ADC輸入設置為滿量程范圍來計算的。舉例來講,要實現25位分辨率,或者152dB動態范圍,可允許的最大系統噪聲為0.2437μVrms。

圖1.噪聲與ENOB和SNR。

基準電壓設置輸入模擬信號的限值,ADC可以解析該信號。公式1是ADC的理想轉換函數,其中輸出數字碼(小數形式)通過模擬輸入信號VIN、基準電壓VREF和ADC位數N計算得出。

一般來說,ADC數據手冊中的分辨率是基于輸入短路技術得出,其中ADC輸入連接至GND,或者ADC差分輸入連接至共源極。ADC輸入短路技術有助于確定ADC分辨率的絕對限值特性,方法是忽略ADC輸入源噪聲,消除VREF噪聲的影響。結果確實如此,因為VIN設置為0V,使得VIN/VREF比也等于0V。

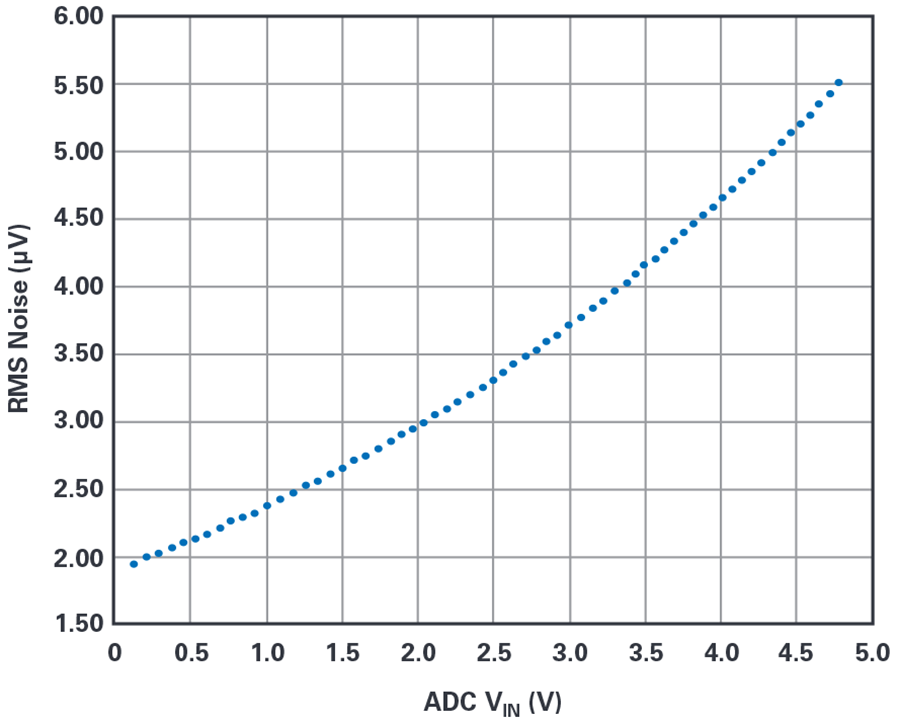

為了研究基準電壓噪聲對整體系統噪聲的影響,圖2顯示了總系統噪聲(rms)和ADC輸入直流源電壓之間的關系。實施本次測試期間,我們使用了AD7177-2 32位ADC,其VREF輸入連接至LTC6655-5(5V),ADC輸入則連接至低噪聲直流源。ADC輸出數據速率設置為10kSPS。注意,在整個ADC輸入電壓范圍內,ADC噪聲保持恒定(35nV/√Hz),但ADC直流輸入源噪聲增大(≤6nV/√Hz),與基準電壓噪聲(96nV/√Hz)相比,仍保持較低水平。如圖2所示,總體噪聲與ADC直流輸入電壓成正比。這是因為VIN(5V),ADC輸入則連接至低噪聲直流源。ADC輸出數據速率設置為10kSPS。注意,在整個ADC輸入電壓范圍內,ADC噪聲保持恒定(35nV/√Hz),但ADC直流輸入源噪聲增大(≤6nV/√Hz),與基準電壓噪聲(96nV/√Hz)相比,仍保持較低水平。如圖2所示,總體噪聲與ADC直流輸入電壓成正比。這是因為VIN/VREF比隨之增大,所以在ADC使用滿量程輸入時,VREF噪聲主導整體系統噪聲。信號鏈中各組件的噪聲會以和方根(RSS)的方式疊加,導致曲線形狀如圖2所示。

圖2.ADC VIN與rms系統噪聲之間的關系。VREF設置為LTC6655-5。

為了實現25位或以上的高測量分辨率,即使是市面上最好的獨立基準電壓(具備低噪聲規格)也需要獲取一些幫助來衰減其噪聲。添加外部電路(例如濾波器)可以幫助衰減噪聲,以達到所需的ADC動態范圍。

本文的其余部分介紹各種類型的低通濾波器,以及如何使用這些濾波器來衰減基準電壓噪聲。本文還會討論濾波器設計技術和與濾波器有關的取舍。本文將以衰減基準電壓噪聲為基礎,介紹兩種類型的低通濾波器,分別是簡單的無源RC低通濾波器(LPF)和基于有源信號流程圖(SFG)的低通濾波器。電路性能部分會展示系統評估結果,用Σ-ΔADC表示測試。

使用無源低通濾波器來降低噪聲

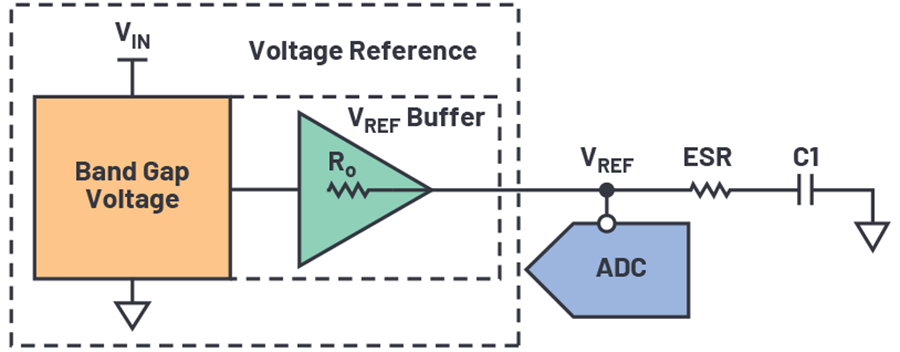

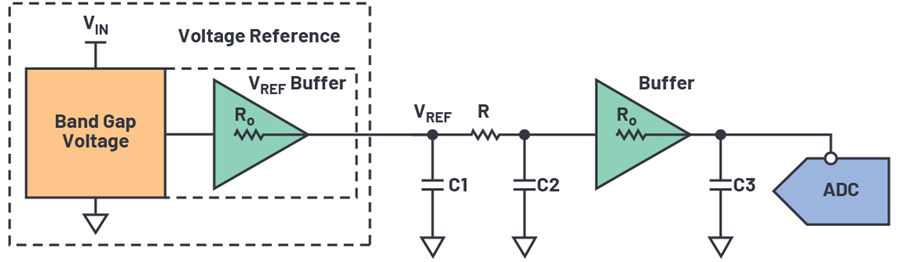

圖3顯示基準電壓通過低通濾波器驅動ADC,該濾波器采用了外部儲能電容C1、儲能電容的等效串聯電阻(ESR),以及基準電壓運算放大器(運放)的輸出阻抗。無源RC LPF截止頻率由以下公式確定

從公式可以看出,帶寬與電阻R和電容C成反比。

從公式可以看出,帶寬與電阻R和電容C成反比。

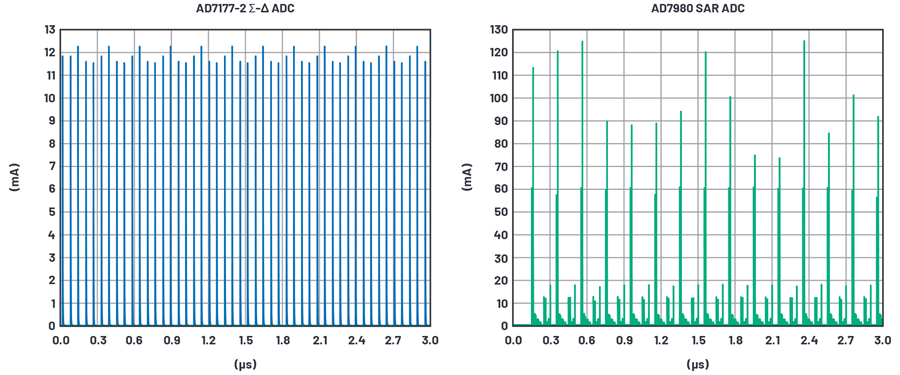

儲能電容C1也可以用作本地電源存儲器,用于補償ADC基準電壓電路突然要求負載電流發生變化時產生的電壓尖峰。圖4顯示Σ-ΔADC AD7177-2和SAR AD7980ADC動態基準電流響應。

圖4.AD7177-2和AD7980模擬動態基準電流響應。

用戶可以選擇C1電容的值來滿足LPF截止頻率要求,但是有些SAR ADC要求基準輸入端采用至少10μF電容,以保證正常運行。最小的10μF C1電容可以降低基準電壓源緩沖器的相位裕量。隨著相位裕量降低,緩沖器反饋不再為負。在單位增益交叉頻率附近的信號與輸入信號同相反饋。1這導致閉環響應在交叉頻率附近出現噪聲峰值。由于源自截止頻率(–3dB點)的帶寬最高達到16MHz,總集成噪聲(rms)由噪聲峰值主導。即使基準電壓儲能電容C1作為噪聲濾波器使用,并補償電壓尖峰,也需注意噪聲峰值。圖5顯示LTC6655基準電壓的噪聲峰值,該峰值因儲能電容C1引起。噪聲峰值幅度由儲能電容的值和其ESR額定值決定。

圖5.LTC6655基準電壓噪聲峰值密度。

大多數基準電壓都具備復雜的輸出級,以驅動適用于ADC基準電壓源電路的大型負載電容。例如,LTC6655輸出級設計用于采用設置為10μF的儲能電容來執行關鍵衰減。LTC6655的儲能電容設置為最小2.7μF、最大100μF時,會產生噪聲峰值。

VREF輸出儲能電容的等效串聯電阻會消除主要的噪聲峰值,但是會在100kHz和以上頻率時產生二次噪聲峰值。究其原因,可能是因為電容的ESR產生零噪聲,可以改善相位裕量和降低主要噪聲峰值。但是,這個零噪聲與LTC6655固有的零噪聲結合在一起,產生了二次噪聲峰值。注意,圖5所示的噪聲響應只適用于LTC6655基準電壓源。

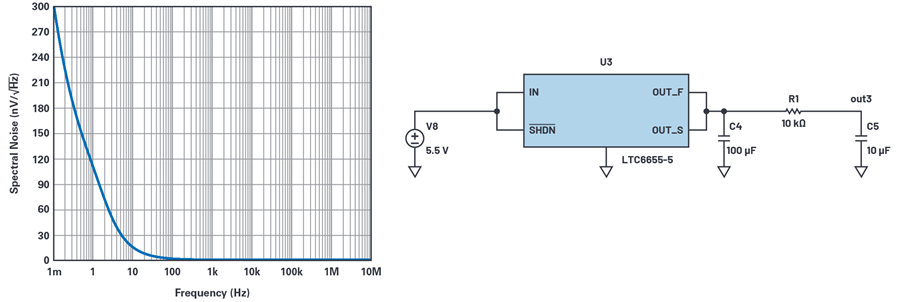

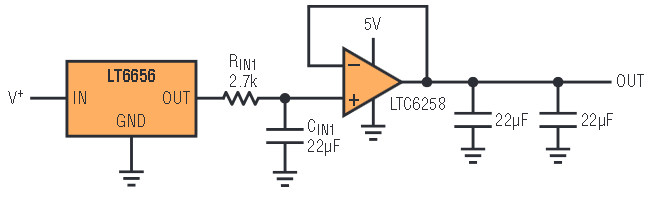

過濾基準電壓噪聲、消除噪聲峰值,以及合理驅動ADC的另一種解決方案是添加無源RC LPF,然后添加緩沖器。通過添加緩沖器,我們可以隔離LPF和ADC基準電壓源輸入電容之間的設計限制。參見圖6。

圖6.無源RC LPF,后接緩沖器。

將無源RC LPF截止頻率設置為遠低于單位增益交越頻率,不止可以降低寬帶和低頻率噪聲,還可以避免出現噪聲峰值。例如,圖7顯示LTC6655噪聲響應,其中C1=100μF(ESR=0Ω),后接無源LPF,其中R=10kΩ、C2=10μF(ESR=0Ω),在1.59Hz時產生極點。

增大低通濾波器電阻R可以幫助實現低截止頻率,但是也可能會降低精密基準電壓的直流精度。添加無源RC LPF時,用戶還必須考慮對負載調整和VREF緩沖器響應(τ=RC)的影響,在驅動ADC時,這會影響其瞬變性能。

要達到所需的瞬變性能,建議如圖6所示使用緩沖器。選擇緩沖器時,要考慮的關鍵規格包括超低噪聲、支持高負載電容的能力、低失真、出色的壓擺率,以及寬增益帶寬。建議采用的緩沖器為ADA4805-1和ADA48071。

圖7.LTC6655-5,后接無源RC LPF噪聲響應。

使用有源LPF降低噪聲

表1指明了所需的動態范圍和必須滿足的可允許最大系統噪聲要求,以實現所需的ENOB ADC分辨率。根據ADC帶寬,按20dB/10倍衰減的單極低通濾波器可能無法達到所需的寬帶噪聲消除。級聯無源低通濾波器構建一個階梯結構,可以生成更高階的濾波器,但每個部分的輸入阻抗將是前一部分的負載。這會降低精密基準電壓的直流精度。但是,基于有源組件設計更高階的LPF可以在輸入和輸出之間提供良好的隔離,最大限度避免基準電壓直流精度下降,并提供低輸出阻抗來驅動ADC的基準電壓源電路。

表1.條件:VREF= 5 V,ADC輸入設置為滿量程范圍

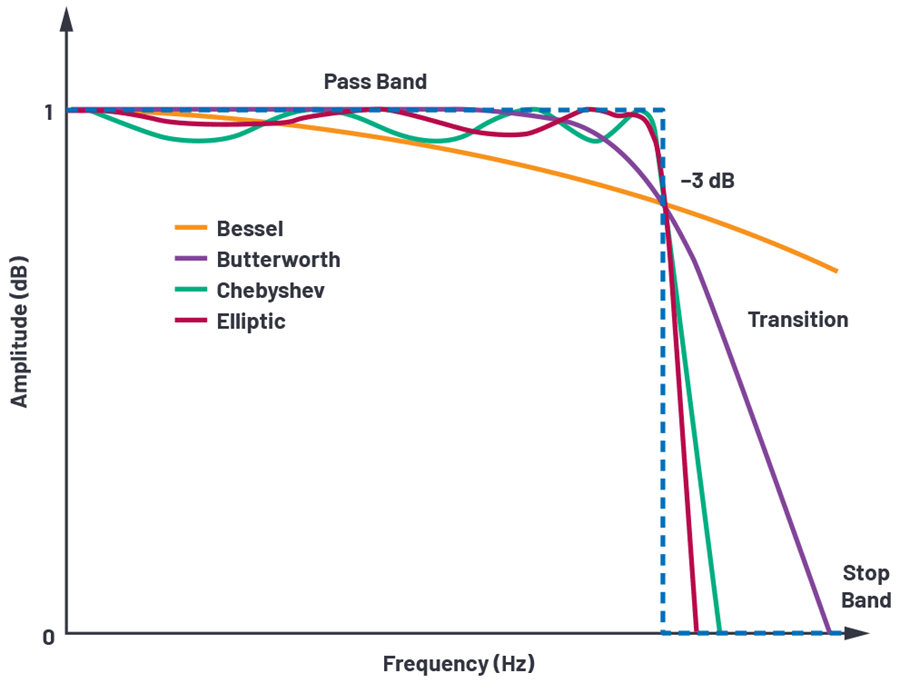

不同類型的有源低通濾波器,例如,Bessel、Butterworth、Chebyshev和elliptic,具體如圖8所示。采用平坦帶通或無紋波帶通,可以最大限度地避免降低精密基準電壓的直流精度。在所有濾波器類型中,基于Butterworth拓撲的LPF設計可以實現平坦的帶通和陡峭的衰減。

圖8.濾波器振幅響應示例。

有源低通濾波器設計技巧

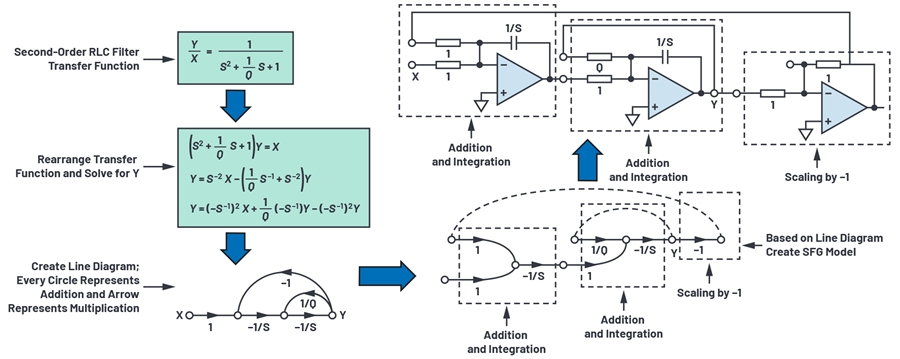

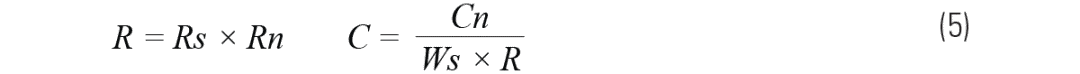

信號流程圖是用圖形表示源自一系列線性公式的系統。SFG用于連接轉換函數和對應的系統電路拓撲。該理論可用于基于有源電路設計模擬濾波器。SFG濾波器設計方法的主要優點在于:衰減系數Q和截止頻率都可以單獨控制。SFG LPF可以幫助衰減噪聲和提高信噪比,但會導致物料成本(BOM)、PCB區域和功率增加。此外,SFG LPF可以影響基準輸出電壓與溫度,導致產生微小PPM誤差,造成直流精度下降。圖9所示為二階低通濾波器示例,該濾波器采用SFG方法,從轉換函數轉換至電路塊。擴展電阻(R)和電容(C)針對截止頻率實施配置(請參見公式5)。

圖9.基于SFG方法實施有源RC低通濾波器。

有關信號流程圖理論的更多信息,請參考Addison-Wesley出版的Feedback Control of Dynamic Systems(《動態系統反饋控制》)。

其中

Rs表示比例因子

Cn表示比例因子

Ws表示截止頻率(Rad/s)

以下是一個計算示例,用于說明如何設計二階0.5Hz截止頻率SFG低通Butterworth濾波器:

-

為了保持簡明,選擇Rs=1Ω,Cn=1F。

-

選擇Fs=0.5Hz,以最大化寬帶噪聲抑制效果。Ws=2×π×0.5=3.141rad.

-

設置衰減因子Q=0.71。選擇此值可實現平坦的帶通和陡峭的衰減,以反映Butterworth拓撲。

-

R、C和Rq值基于迭代流程選擇,以實現較低熱噪聲和可用于表面貼裝的組件值。

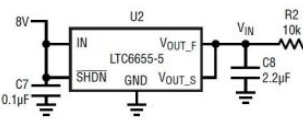

LTC6655LN簡介

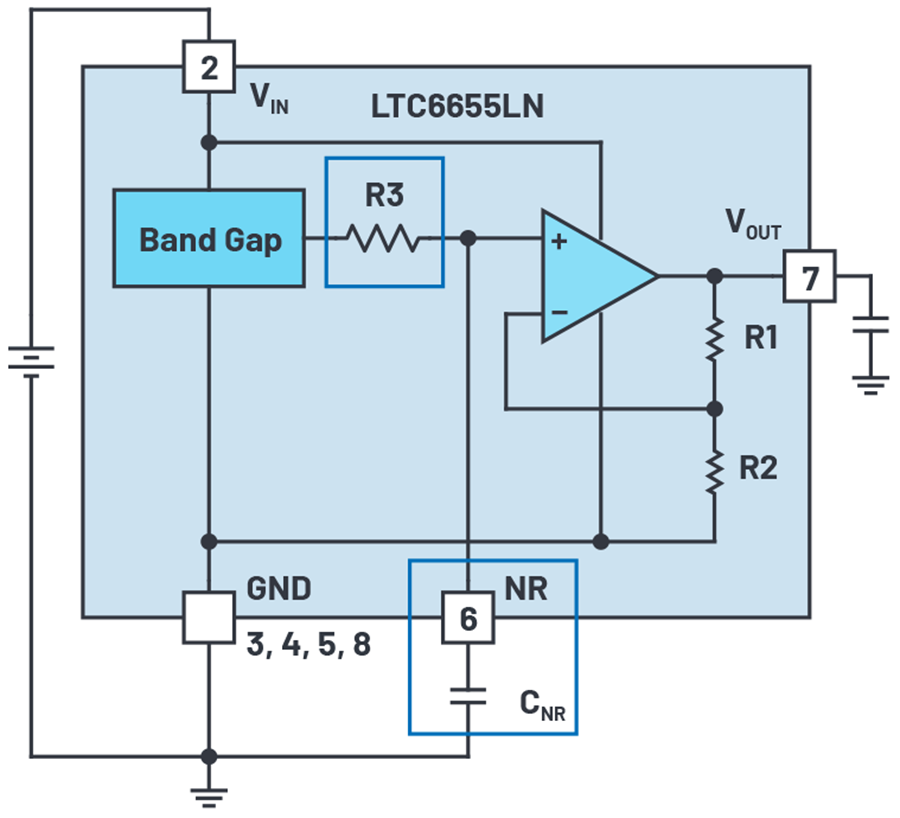

考慮到與RC LPF和SFG LPF有關的取舍,更好的解決方案是如圖10所示,將低通濾波器安裝在基準電壓的集成式低噪聲緩沖器之前。這種布局不但會減小PCB面積,還不影響基準電壓緩沖器的響應。使用快速穩定,具有高輸入阻抗,能夠灌電流和拉電流的基準電壓緩沖器,有助于解決負載調整不良的問題,保持直流精度,以及改善瞬變性能。LTC6655LN采用了這種架構。它配有降噪引腳,可以幫助降低寬帶噪聲,支持使用集成式輸出級緩沖器。LTC6655LN內置R3電阻(參考圖10),允許用戶在降噪(NR)引腳位置連接外部電容,以創建低通濾波器。采用LTC6655LN架構時,用戶可以根據系統要求配置低通截止頻率。

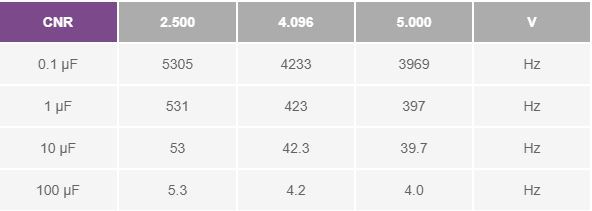

表2.3 dB截止頻率,適合連接至NR引腳的電容實現不同值

LTC6655LN RC LPF連接至緩沖器的非反向節點,該節點是此器件最靈敏的引腳。必須做好預防措施,應選擇極低漏電流類型的外部電容,以防泄漏電流從R3電阻漏出,導致直流精度下降。此外,R和C之間的變化相互無關,所以RC時間常數和LPF截止頻率會因為流程、電壓和溫度(PVT)差異而產生變化。

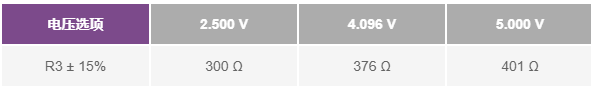

表3.3種電壓選項的R3的電阻值

基準電壓(例如內置LPF的LTC6655LN)提供最佳解決方案,用于簡化噪聲濾波器設計,消除對外部緩沖器的需求,以驅動ADC基準電壓電路。

圖10.LTC6655LN方框圖。

測試電路描述

AD7177-2精密ADC被用于確定LTC6655/LTC6655LN加10uF NR電容以及LTC6655后接SFG濾波器的標準性能,。AD7177-2是高分辨率32位低噪聲快速穩定2通道/4通道∑-?模數轉換器,用于實現低帶寬輸入。AD7177-2集成可編程數字帶通濾波器,允許用戶控制5SPS至10kSPS的輸出數據速率(ODR)。

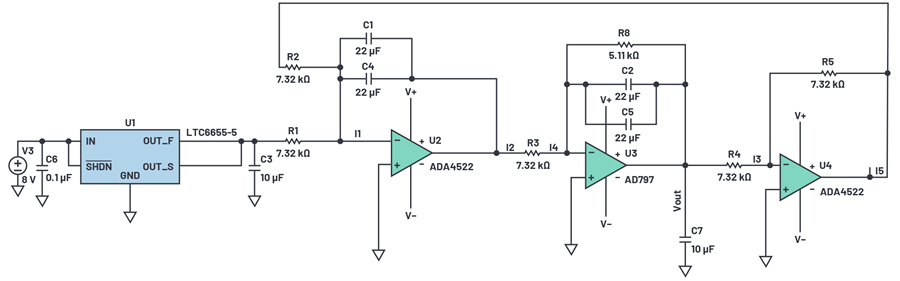

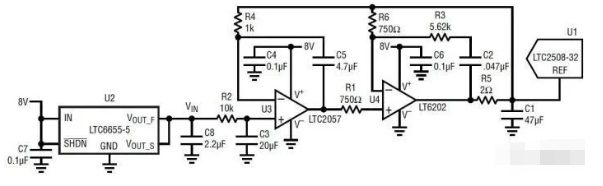

設計SFG LPF(圖11)時用到的組件包括2個ADA4522-1運算放大器、1個AD797運算放大器、多個25ppm表貼式電阻、多層表貼式陶瓷電容,以及1個10μF WIMA薄膜電容。ADA4522是一款軌到軌輸出運算放大器,寬帶噪聲密度為5.8nV/√Hz,閃爍噪聲為177nVp-p。AD797是一款低噪聲運算放大器,具備0.9nV/√Hz寬帶噪聲、50nVp-p閃爍噪聲、20V/μs出色壓擺率,以及100MHz增益帶寬,因此適合驅動ADC。

圖11.SFG LPF。

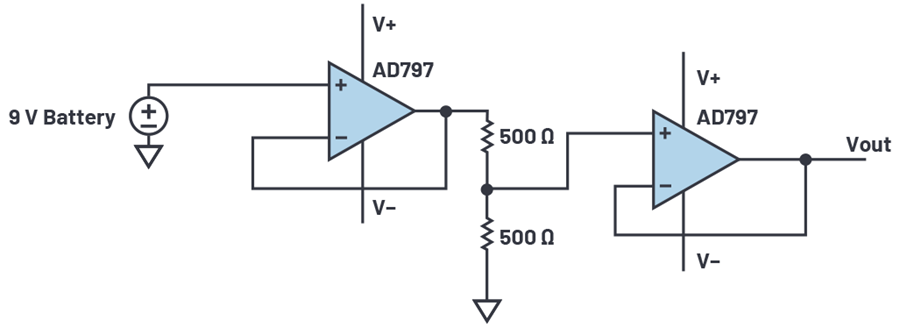

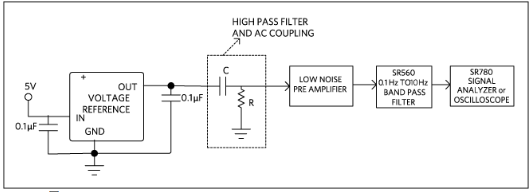

在使用LTC6655和帶有AD7177-2的LTC6655LN時,為了正確評估性能,需要使用整體噪聲低于ADC基準電壓和ADC噪聲的直流源。因此,會使用理想源,也就是9V電池電源,具體如圖12所示。

圖12.低噪聲直流源。

電路性能

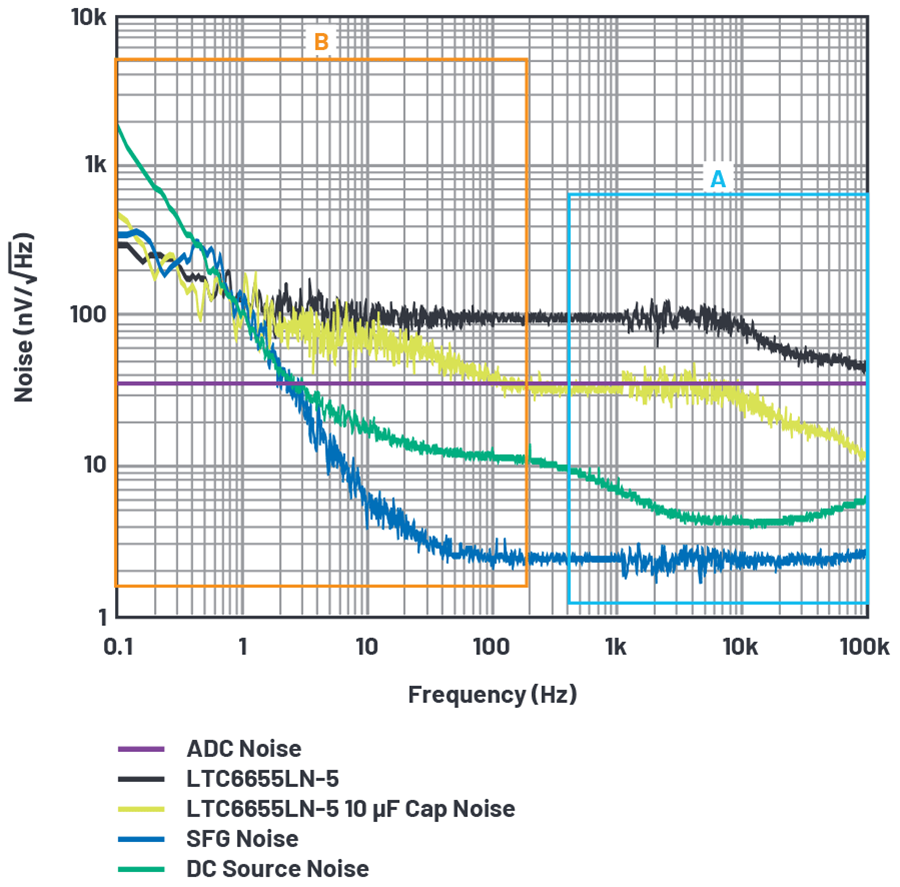

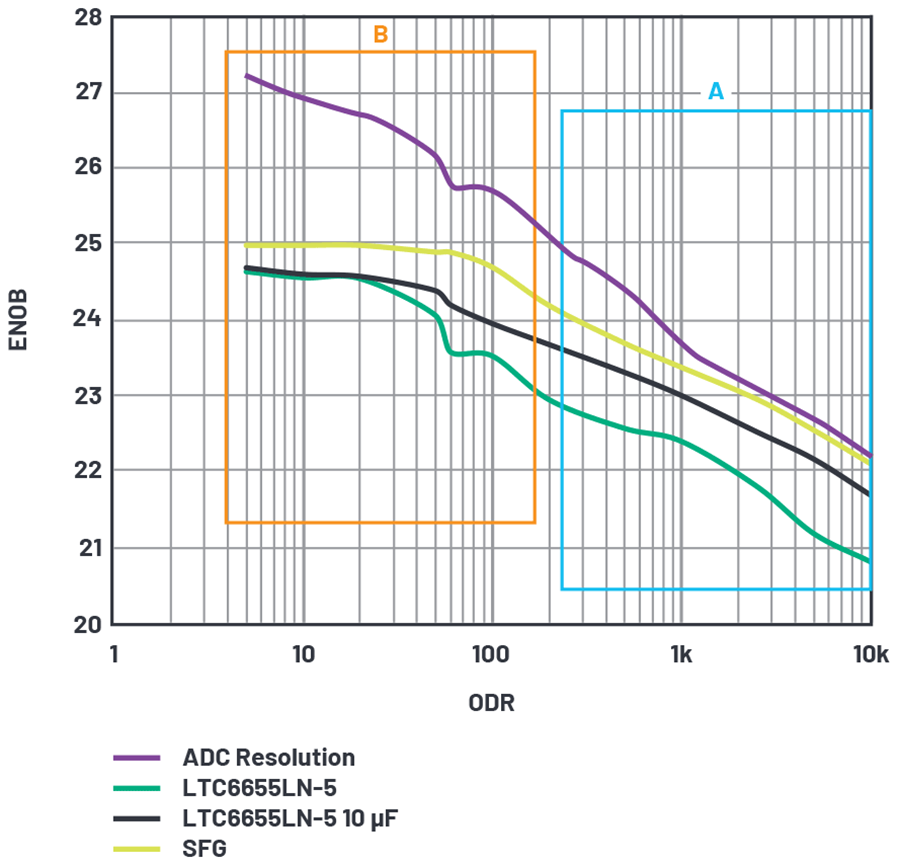

圖13顯示噪聲譜密度,圖14顯示輸出數據速率(ODR)和ENOB,描述AD7177-2的性能,它的VREF輸入連接至LTC6655或者采用10uF NR電容的LTC6655LN或者使用SFG方法濾波的LTC6655。關于在1 kHz時噪聲譜密度的比較結果,請參見表4。圖13和圖14都有兩個重要區域。

表4.1 kHz時的噪聲譜密度比較結果

區域A:

噪聲譜密度圖(圖13)顯示,ODR為500SPS及以上時,濾波LTC6655(SFG)和ADC直流輸入源噪聲遠低于ADC的噪聲,因此,ADC可以最大限度的去實現其最大性能,具體如圖14中的區域A所示。從ODR、ENOB和噪聲譜密度圖中可以看出,在區域A中,總集成噪聲(rms)的增高會妨礙信號鏈達到25位測量分辨率。

區域B:

在這個區域中,噪聲譜密度圖(圖13)顯示,三個基準電壓選項和直流源的閃爍噪聲升高,整體的系統噪聲則受直流源噪聲主導。區域B中的閃爍噪聲升高,會導致測量性能和ADC可以實現的最大性能之間的ENOB偏差增大(圖14)。

根據ODR和ENOB圖,濾波LTC6655(SFG)的ODR在小于等于20SPS時可以實現25位分辨率,帶10μF NR電容的LTC6655LN-5和LTC6655實現的分辨率最高不超過24.6位。

圖13.噪聲譜密度。

圖14.ODR與ENOB。

下方的表5匯總介紹AD7177-2ADC的性能,其中VREF輸入連接至LTC6655或者帶10μF NR電容的LTC6655LN,或者連接至濾波LTC6655(SFG)。在ADC輸入連接直流源,VREF輸入連接至LTC6655時,零縮放欄確定AD7177-2可以實現的最佳動態范圍。在ADC輸入設置為近乎滿量程時,帶10 μF NR電容的LTC6655LN-5的動態范圍平均增大4dB(與LTC6655相比,ODR范圍為10000SPS到59.96SPS)。另一方面,濾波LTC6655(SFG)的動態范圍平均增大7dB(與LTC6655相比,ODR范圍為10000SPS到59.96SPS)。在59.96SPS以下,動態范圍區域的變化不大,由ADC輸入直流源產生、占主導作用的低頻率閃爍噪聲是導致差異的主要原因。

與LTC6655/LTC6655LN相比,將10μF電容連接至LTC6655LN的NR引腳時,在1kHz時可以將寬帶噪聲降低62%,濾波LTC6655(SFG)可以將寬帶噪聲降低97%。

精密系統如果想要實現25位或以上的分辨率,必須非常重視基準電壓噪聲。如圖2所示,VREF噪聲占系統噪聲的比例與ADC滿量程的使用率成正比。本文顯示,在精密基準電壓中添加濾波器可以衰減VREF噪聲,從而降低整體的系統噪聲。后接SFG濾波器的LTC6655基準電壓可以將未配備濾波器的LTC6655的寬帶噪聲降低97%。但這會額外增加物料成本,增大PCB面積和功耗,降低幾PPM的直流精度,且導致精密基準電壓源輸出隨溫度發生變化。在考慮與SFG LPF有關的取舍時,LTC6655LN采用簡單設計,功耗低,只需要使用單個電容來降低寬帶噪聲,且無需使用外部緩沖器來驅動ADC。帶10μF NR電容的LTC6655LN與不帶濾波器的LTC6655相比,其寬帶噪聲降低62%。因此,用戶現在可以使用內置的LTC6655LN低通濾波器來讓精密系統實現所需的分辨率。

文章出處:【微信公眾號:亞德諾半導體】歡迎添加關注!文章轉載請注明出處。

-

噪聲

+關注

關注

13文章

1118瀏覽量

47369 -

基準電壓

+關注

關注

3文章

83瀏覽量

23119

原文標題:為何基準電壓噪聲非常重要?看了這篇你就明白了

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于LT6656精準串聯電壓基準的低噪聲基準

高質量的電壓基準設計

電壓基準噪聲對增量累加ADC中的DC噪聲性能的影響

DSPICFJ128GP802做音頻晶體離針遠一點重要嗎?

濾波器電路圖有嗎?該如何降低基準輸出噪聲?

775噪聲測量系統低噪聲電壓基準

基準電壓噪聲重要嗎?看完你就明白了!

基準電壓噪聲重要嗎?看完你就明白了!

評論