本篇將以德州儀器(TI)的高速ADC芯片—ads52j90為例,進行ADC的4線SPI配置時序介紹與分析。

從ads52j90的數據手冊我們不難發現,其SPI控制模塊主要包含4根信號線SEN,SCLK,SDIN以及SDOUT。TI公司對其產品SPI配置信號的命名方式與通用的SPI信號命名方式不一樣,但實際上SENSDINSDOUT分別對應CSBSDISDO。

SEN:SPI讀寫的使能信號;

SDIN:FPGA寫入ADC的配置數據(寄存器地址和對應地址的值);

SDOUT:ADC對應地址輸出的配置寄存器數據;

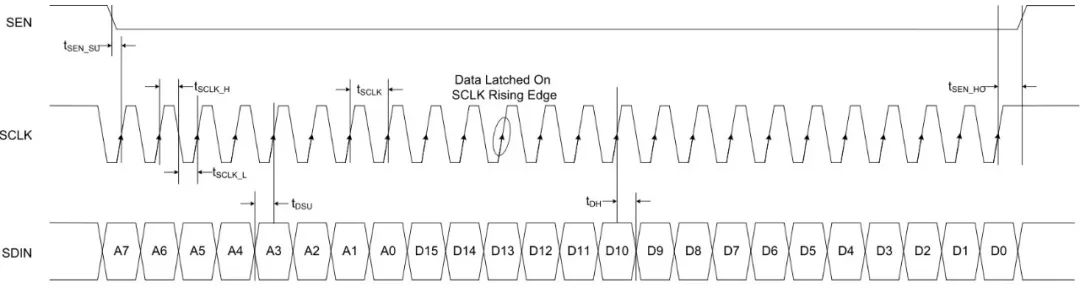

首先介紹該ADC的SPI的寫時序,datasheet給出的時序圖如圖1所示:我們首先大致看一下寫時序圖,能夠了解到對于SDIN來說,需要先寫入A7~A0的8bit的地址,接下來寫入該地址下的16bit的寄存器數值D15~D0,也就是說每進行一次寫操作需要不間斷的寫入24bit的數據。對于SEN來說,在進行寫操作時,其一直保持低電平,寫之前和寫完后都保持高電平。對于SCLK來說,其上升沿每次采集每1bit SDIN數據的中心位置,共需要采集24次,才能完成這24bit SDIN數據的寫入。

圖1:SPI寫時序圖

上面三點就是我們初步看這個時序圖所得到的結論。對于該ADC,按照這種方式進行寫操作就不會有問題。實際上所有ADC的SPI寫操作都有類似于上面介紹的共同準則,這里歸納如下:

1,無論SPI進行讀還是寫操作,SEN必須拉低,否則SPI不工作(既不讀也不寫),讀、寫完成之后SEN必須拉高;

2,SDIN的數據每次在SCLK的上升沿寫入SPI;

3,SDIN的數據組成一定是先寫入配置寄存器地址,再連續寫入配置寄存器數值;

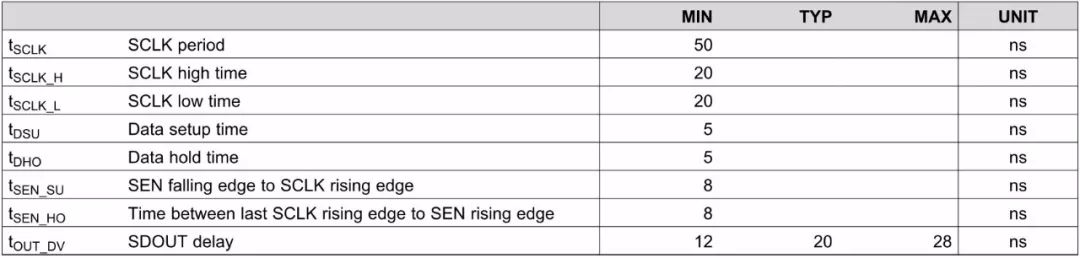

圖2:SPI時序要求

另外,我們看到時序圖上有許多時間參數,我們在寫代碼時不僅要遵守以上的共同準則,還要滿足這些參數的時序關系,并保留一定的時間量。datasheet都提供了這些參數的大小,如圖2所示。比如tSCLK的最小值是50ns,意味著SPI的時鐘最高20MHz。tSEN_SU的最小值為8ns,就表示SEN下降沿至少提前第一個SCLK的上升沿時間8ns。tDSU則表示SDIN的數據必須至少提前SCLK的上升沿5ns準備好,等等。只要遵守了相關的SPI準則以及datasheet里的SPI時序參數,SPI的寫操作就不會有問題了。

現在我們介紹該ADC的SPI讀時序,如圖3所示。讀操作的主要目的是監測ADC內部寄存器狀態,從而判斷ADC的配置狀態是否符合用戶的需求。從圖上我們可以看到,SPI的讀操作可以分解為兩個部分:第一個部分是先寫入A7~A0 8bit的寄存器地址到SDIN,然后SDOUT輸出對應地址的16bit的寄存器數值。

這里重點強調一下:理論上來說,在上升沿鎖存寫入的地址最后1bit后,在接下來的每次SCLK下降沿,SDOUT輸出1bit寄存器值,直到16bit寄存器數值完全輸出。但實際上每次SCLK下降沿輸出的數據只有經過tOUT_DV(12ns ~28ns)后才穩定,后端FPGA才能正確接收。從圖上我們不難發現,FPGA在SCLK的上升沿附近獲取SDOUT的數據是非常合適的,在這個位置獲取的數據最穩定。

圖3:SPI讀時序圖

4線SPI的讀寫時序分析就到這里了,再次強調幾個關鍵點:

關鍵點1:SEN在讀寫操作時,必須拉低。讀寫完成之后,必須拉高。

關鍵點2:SDIN的數據每次必須在SCLK的上升沿寫入SPI。對應的數據格式一定是寄存器地址+要寫入的寄存器數值。

關鍵點3:SOUT的數據總是在SCLK的下降沿輸出,因此選擇FPGA在SCLK的上升沿獲取SDOUT數據最穩定。

關鍵點4:一定要滿足datasheet給出的SPI的時序參數,并在代碼實現時要留有適當的時序裕量。

-

芯片

+關注

關注

453文章

50410瀏覽量

421849 -

adc

+關注

關注

98文章

6438瀏覽量

544104 -

SPI

+關注

關注

17文章

1701瀏覽量

91329

原文標題:FPGA通過SPI對ADC配置簡介(二)--4線SPI配置時序分析

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問ADS8671讀寫時序是怎么樣的?

ADC3663的SPI配置管腳連接至FPGA時遇到IO電平不匹配怎么解決?

ADS127L11配置ADC使用外部時鐘以及FILTER[4:0]都不成功,為什么?

ADS127L11使用4線spi不管怎么配置寄存器,示波器看到ADC的drdy脈沖周期始終是400K,怎么回事?

瀚海微SD NAND之SD 協議(42)SPI總線時序

DDR4時序參數介紹

FPGA 高級設計:時序分析和收斂

STM32F4 Cube配置ADC時選擇轉換觸發通道的選項中為什么沒有EXTI線11的選項?

STM32H7的Octo-SPI或者Quad-SPI能否支持讀取ADC的數據?

FPGA通過SPI對ADC配置簡介(三)3線SPI配置時序分析

ADC的4線SPI配置時序介紹與分析

ADC的4線SPI配置時序介紹與分析

評論