上篇介紹了如何利用verilog實現4線SPI配置時序,本篇將以AD9249介紹其3線SPI配置的verilog實現。

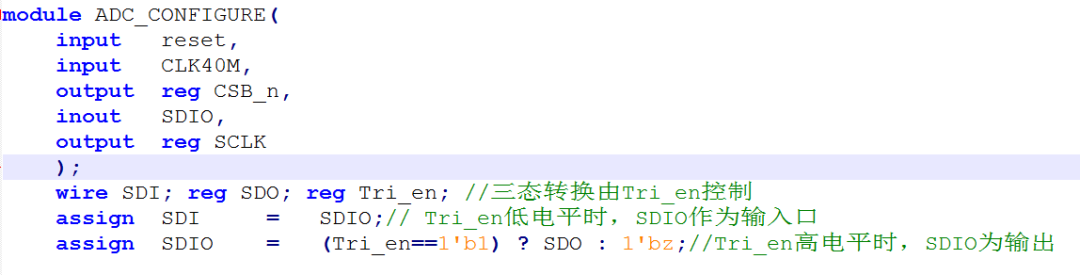

3線SPI的時鐘產生方式和上一篇的4線SPI相同,這里不在敘述。兩者的不同點在于:三線SPI模式需要FPGA管腳三態控制SDIO的輸入/輸出狀態。下圖所示的代碼即為三態控制邏輯。SDI、SDO成為了內部邏輯信號,和上篇的4線SPI配置相同操作即可,而SDIO為三態管腳,需定義為inout類型。

Tri_en信號即為三態控制信號,在寫操作中,該信號必須置高;然而在讀操作中,該信號在寫地址的前半段需置高,當完成寫地址操作后,ADC的SDIO接口由輸入變輸出,此時FPGA控制Tri_en信號拉低,將FPGA端的SDIO管腳由輸出變為輸入,從而正常接收ADC的SDIO口輸出的寄存器數值。

Tri_en到底應該在哪個具體時刻拉低,以便完成FPGA的SDIO三態轉換呢?答案其實在第三篇已經說的很清楚了~~~~

另外,3線SPI讀/寫操作有專門的讀寫標志位,大家務必要留心~~

3線SPI的FPGA實現就介紹到這里了,其實和4線基本一樣,只不過多了個三態轉換而已,大家把上篇的4線SPI的實現過程想清楚了,再加上一個三態轉換控制,3線SPI也就拿下了!

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601866 -

Verilog

+關注

關注

28文章

1344瀏覽量

109986 -

SPI

+關注

關注

17文章

1701瀏覽量

91329

原文標題:FPGA通過SPI對ADC配置簡介(五)--Verilog實現3線SPI配置

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

能否在純fpga上通過verilog實現SPI控制器去配置adc12dj3200?

單片機SPI通信實現

esp32-s3 spi初始化如何配置SPI_DEVICE_3WIRE?

用一塊fpga板通過杜邦線以SPI的方式控制AD5504,連接后發現并沒有控制上AD5504,為什么?

盤古1K開發板主芯片PGC1KG-LPG100介紹

SPI一根時鐘線一根單向數據線可以實現讀寫從機數據嗎?

電纜驅動傳感器儀表PT420-0040-111-1110介紹

STM32F407 3線SPI如何配置?

5V轉220V新一代無變壓器大功率升壓模塊XKT203-08介紹

FPGA通過SPI對ADC配置簡介(三)3線SPI配置時序分析

以AD9249介紹其3線SPI配置的verilog實現

以AD9249介紹其3線SPI配置的verilog實現

評論