時序電路是數字電路的基本電路,也是FPGA設計中不可缺少的設計模塊之一。時序電路與組合電路最大的不同點是:時序電路的輸出不僅與輸人有關,還與電路本身的狀態有關,即時序電路有記憶功能。大部分時序電路還有一個特征,就是有時鐘驅動,電路的各個狀態在時鐘節拍下變化。本章主要介紹時序電路的一些基本組件及一些簡單的時序邏輯電路應用實例。

13.1D觸發器建模

【D觸發器建模】

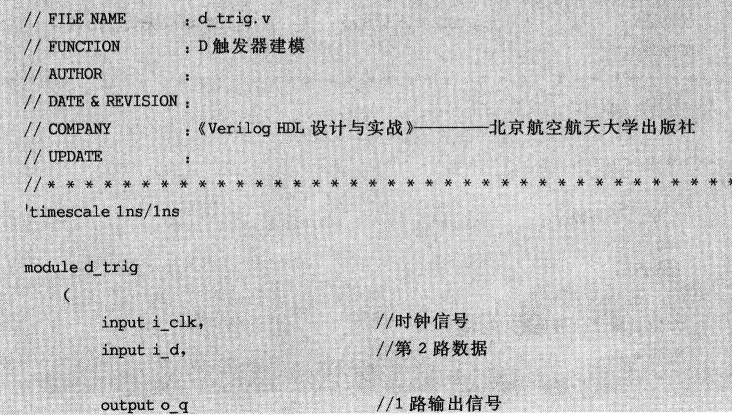

D觸發器是時序電路最基本的組件之一,其基本功能是:輸出端Q的更新只發生在時鐘信號的上升沿(也可以是下降沿,在沒有其他說明的情況下,例子中取上升沿)時刻,更新為此時輸人端D的信號。D觸發器的Verilog HDL編碼的實現比較簡單,具體實現如【代碼13-1】所列。

【代碼13-1】

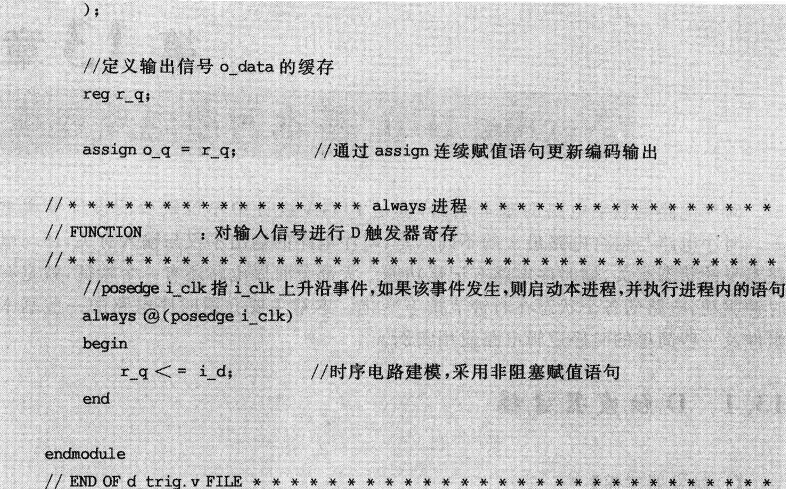

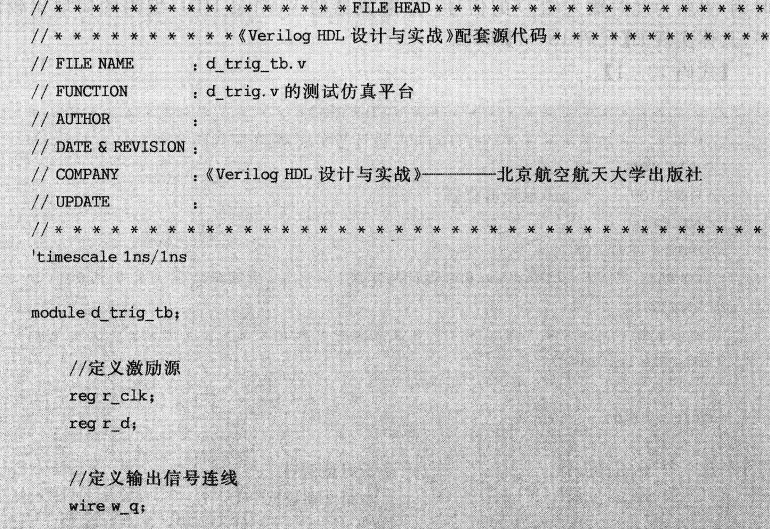

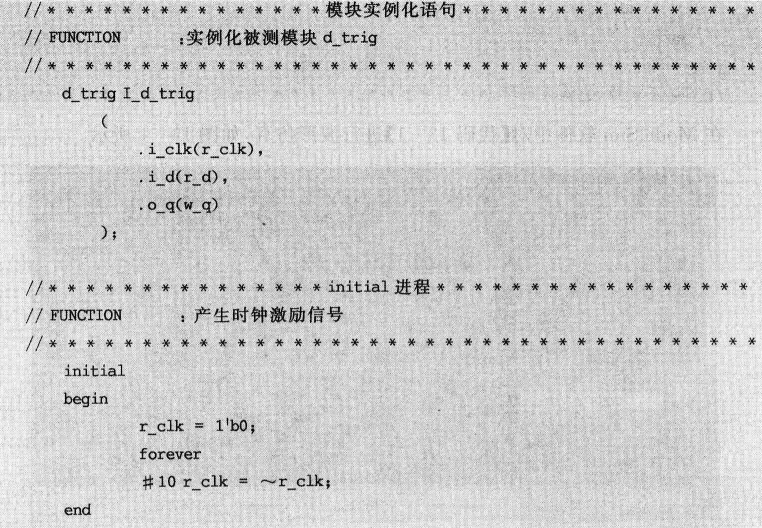

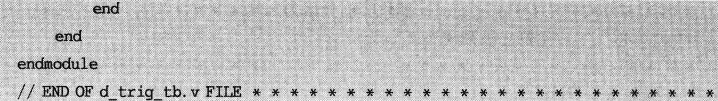

編寫【代碼13-1】的測試平臺如【代碼13-2】所列。

【代碼13-2】

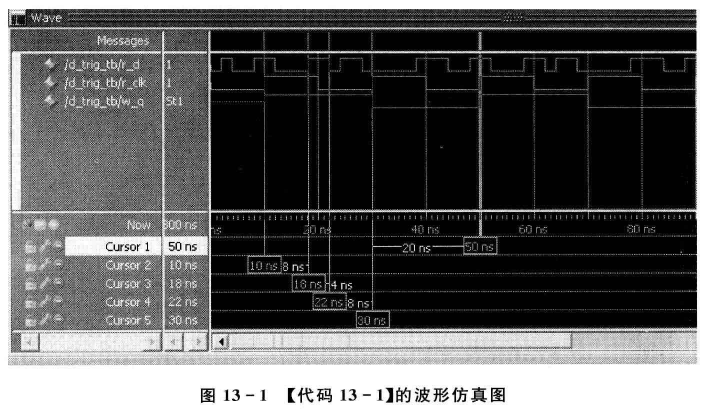

在ModelSim軟件中對【代碼13-1】進行波形仿真,如圖13-1所示。

波形仿真報告分析

從圖13-1可以看出,在10ns時刻以前,由于時鐘信號的上升沿還沒有到來過,所以w_q的值沒有被更新過,為x;在10ns時刻,在時鐘信號的,上升沿事件發生,w_q更新為此刻的r_d,值為1,該值會一直保持到時鐘信號的下一個上升沿事件發生時;在10ns時刻,雖然r_d的值發生了變化,但由于不是發生在時鐘信號的上升沿時刻,所以w_q的值并沒有發生變化。以上對波形的分析符合D觸發器的功能特點。

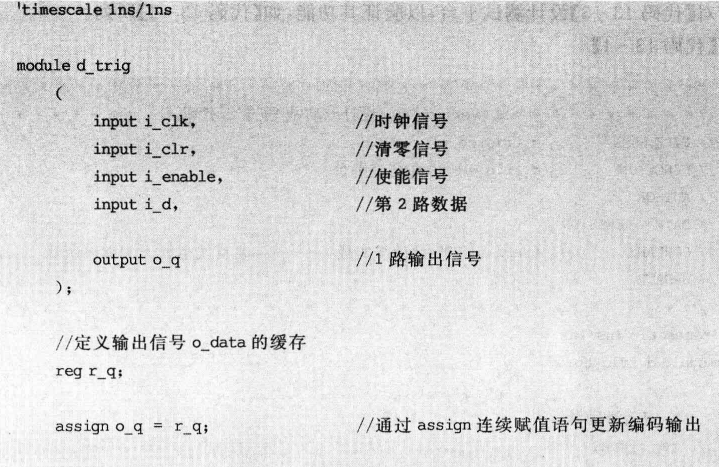

此外,還可以對【代碼13-1】的D觸發器加入一些控制信號,如清零信號、使能信號,具體實現如【代碼13-3】所列。

【代碼13-3】

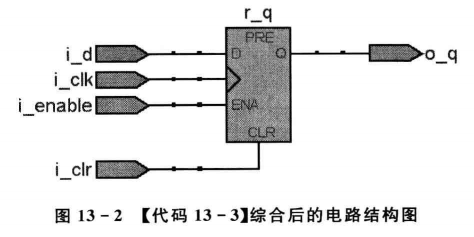

【代碼13-3】在Quartus II軟件中綜合后的電路結構如圖13-2所示。

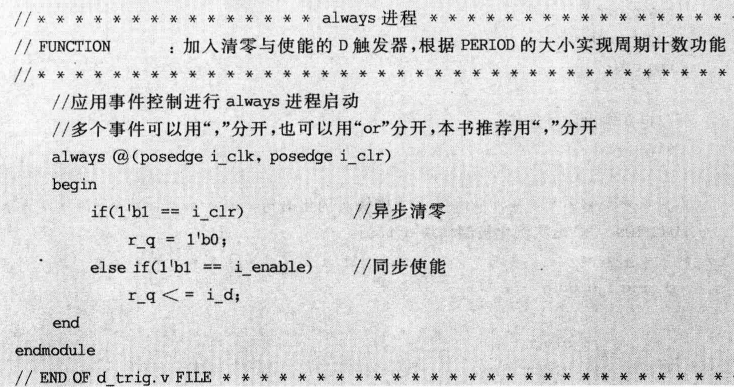

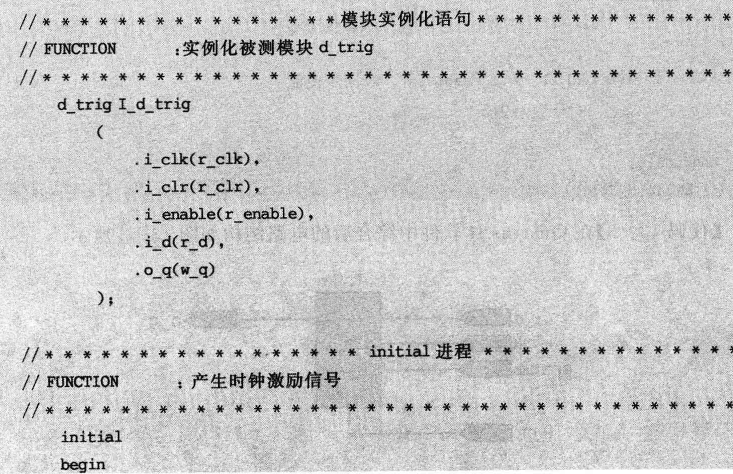

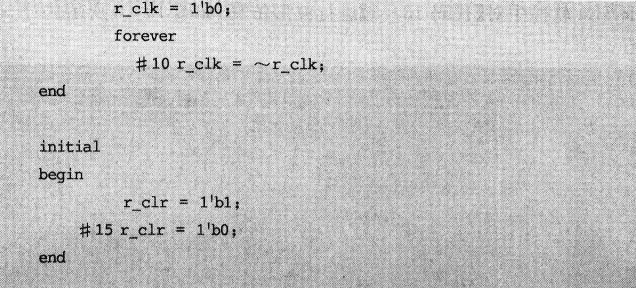

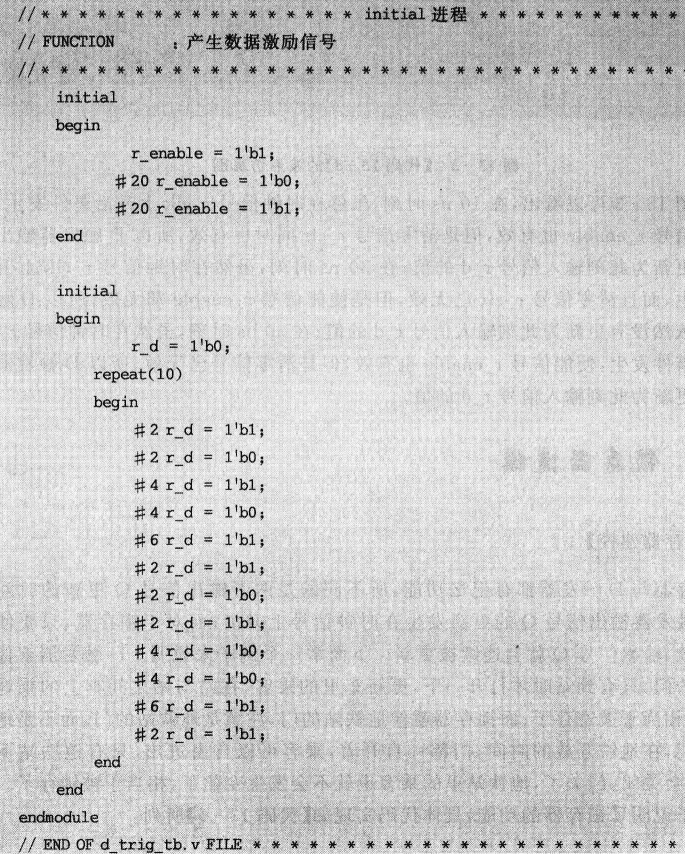

對【代碼13-3】設計測試平臺,以驗證其功能,如【代碼13-4】所列。

【代碼13-4】

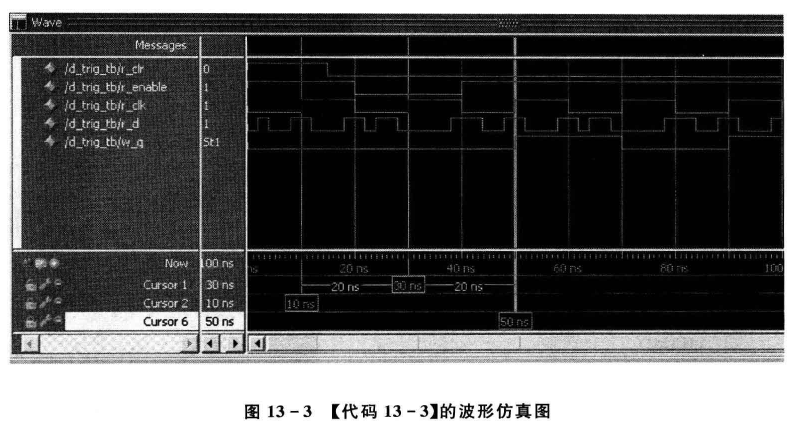

在ModelSim軟件中對【代碼13-3】進行波形仿真,如圖13-3所示。

從圖13-3可以看出,在10ns時刻,雖然在時鐘信號r_clk上升沿事件發生,而且使能信號r_enable也有效,但是清零信號r_clr同時也有效,所以D觸發器輸出依然沒有更新為此刻輸入信號r_d的值;在30ns時刻,雖然在時鐘信號r_clk上升沿事件發生,而且清零信號r_clr已無效,但是使能信號r_enable卻無效,所以D觸發器輸出依然沒有更新為此刻輸入信號r_d的值;在50ns時刻,雖然在時鐘信號r_clk上升沿事件發生,使能信號r_enable也有效,但是清零信號已無效,所以D觸發器輸出立即更新為此刻輸入信號r_d的值。

除此之外,有關Verilog HDL基本時序電路建模方面,還包括了鎖存器建模、JK觸發器建模等。想學習更多Verilog HDL建模、時序與整合電路方面的知識,可以下載編者為大家精選準備的一份FPGA學習指南合集:Verilog HDL那些事兒(建模篇,時序篇,整合篇)

Verilog HDL那些事兒建模篇:

在眾多的Verilog HDL 參考書,隱隱約約會會出現這樣的一個“建模”。建模在Verilog HDL的世界里是一個重要的基礎,很多初學Verilog HDL + FPGA 的朋友會成為徘徊在邊緣的一群,主要原因就是他們沒有掌握好建模技巧,而形成他們繼續前進的一大阻礙。在這里筆者將自己養成的建模技巧,編輯成為一本筆記,好讓許更多初學的朋友越過這一段學習的大障礙。

Verilog HDL那些事兒時序篇:

建模不是Verilog HDL 語言的所有,建模只是使用Verilog HDL 語言建立一個“像模像樣”的“形狀”而已。這個“形狀”實際上是很粗糙的,還沒有經過任何深入的分析。但是我們不可以小看這個“粗糙的形狀”,如果沒有這個“粗糙的形狀”模塊的設計根本無法完成。筆者在《Verilog HDL 那些事兒-建模篇》的結束語中有這樣講過:“建模是一個粗糙的東西,它還可以繼續細化”。

“細化”顧名思義就是進入模塊的深層進行分析和優化(如果有需要調試的話)的工作。但是前提,我們必須“更深入Verilog HDL 語言的世界”才能有效的“細化”模塊。這一本起名為《Verilog HDL 那些事兒-時序篇》的筆記分別有兩個部分,上半部分和下半部分。上半部分是“步驟和時鐘”;下半部分是“綜合和仿真”。

Verilog HDL那些事兒整合篇:

要在Verilog 要實現for 和while 等循環是一個矛盾的作業,這話何說呢?首先我們可以用Verilog 來模仿for 和while 等循環,這也是第一章的重點。可是隨著我們深入了解Verilog 各種不同的運行模式,模仿就會失去意義。.. 因為只要有一個指向步驟的i 再加上一些整合的技巧,怎么樣的循環我們都可以實現,這也是第五章的重點。當然整合篇所討論的內容不單是循環而已,整合篇的第二個重點是理想時序和物理時序的整合。說實話,筆者自身也認為要結合“兩個時序”是一件苦差事,理想時序是Verilog的行為,物理時序則是硬件的行為。不過在它們兩者之間又有微妙的“黏糊點”,只要稍微利用一下這個“黏糊點”我們就可以非常輕松的寫出符合“兩個時序”的模塊,但是前提條件是充足了解“理想時序”。

整合篇里還有一個重點,那就是“精密控時”。實現“精密控時”最笨的方法是被動式的設計方法,亦即一邊仿真,一邊估算時鐘的控制精度。這顯然是非常“傳統”而且“古老”的方法,雖然有效但往往就是最費精神和時間的。相反的,主動式是一種講求在代碼上和想象上實現“精密控時”的設計方法。主動式的設計方法是基于“理想時序”“建模技巧”和“仿順序操作”作為后盾的整合技巧。不說筆者吹牛,如果采用主動式的設計方法驅動IIC 和SDRAM 硬件,任何一段代碼都是如此合情合理。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42577 -

時序電路

+關注

關注

1文章

114瀏覽量

21681

原文標題:FPGA設計應用實例—Verilog HDL基本時序電路建模

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序邏輯電路設計

時序邏輯電路的分析和設計

數字電路基礎教程之時序邏輯電路的詳細資料概述

時序電路基本組件及時序邏輯電路應用實例

時序電路基本組件及時序邏輯電路應用實例

評論