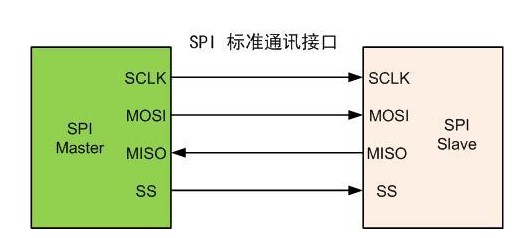

SPI數(shù)據(jù)通信是常用的一種中低速芯片級的數(shù)據(jù)通信。SPI數(shù)據(jù)通信協(xié)議簡單,連線不多,而且是全雙工通信,因此廣泛用于實(shí)現(xiàn)數(shù)據(jù)轉(zhuǎn)換和數(shù)據(jù)存儲等功能。本章簡要介紹SPI數(shù)據(jù)通信的協(xié)議及主端與從端的VerilogHDL建模與仿真。

SPI數(shù)據(jù)通信協(xié)議

SPI是英文Serial Peripheral Interface的首字母縮寫,中文可以翻譯為串行外圍設(shè)備接口。SPI 是Motorola公司首先推出的一種同步串行接口。它用于CPU或者FPGA與各種外圍器件進(jìn)行全雙工、同步串行數(shù)據(jù)通信。SPI 通信接口簡單,只需要4根線:clk同步時(shí)鐘信號、mosi主端輸出/從端輸人數(shù)據(jù)信號、miso主端輸人/從端輸出數(shù)據(jù)信號、cs從端片選信號(如果有多個(gè)從端,則需要有多個(gè)cs從端片選信號與之相對應(yīng))。SPI數(shù)據(jù)通信的同步串行傳輸順序是高位先傳、低位后傳。

四種SPI通信模式

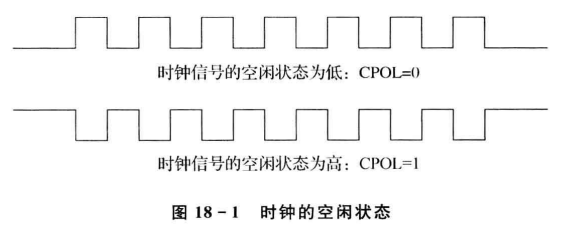

SPI數(shù)據(jù)通信有4種模式,分別稱為模式1至模式4。不同的模式是由開始數(shù)據(jù)采樣的邊沿及時(shí)鐘的空閑狀態(tài)決定的。時(shí)鐘的空閑狀態(tài)有2種,即高電平與低電平,分別對應(yīng)CPOL=1與CPOL=0,如圖18-1所示。

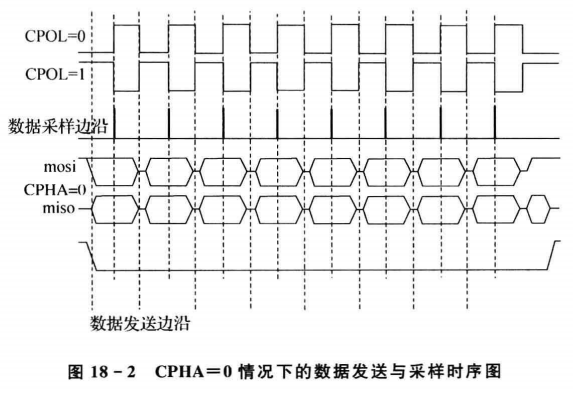

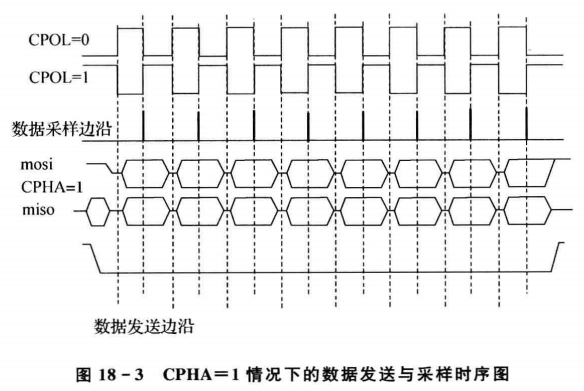

發(fā)送與接收數(shù)據(jù)的時(shí)鐘邊沿的情況也有2種:數(shù)據(jù)開始采樣發(fā)生在時(shí)鐘的第一個(gè)邊沿(也可理解為奇數(shù)邊沿進(jìn)行數(shù)據(jù)采樣)與數(shù)據(jù)開始發(fā)送發(fā)生在時(shí)鐘的第二個(gè)邊沿(也可理解為偶數(shù)邊沿進(jìn)行數(shù)據(jù)發(fā)送),分別對應(yīng) CPHA=0與CPHA=1,如圖18-2與圖18-3所示。

根據(jù)CPOL與CPHA的值,SPI的傳輸就可分為4種模式:模式0是CPOL=0,CPHA=0;模式1是CPOL= 1,CPHA=0;模式2是CPOL=0,CPHA=1;模式3是CPOL=1,CPHA=1。本章以模式0為例進(jìn)行介紹。

對應(yīng)圖18-2,分析在片選信號下降沿有效時(shí)開始發(fā)送最高位數(shù)據(jù),其余的數(shù)據(jù)在時(shí)鐘信號的下降沿發(fā)送,最后一個(gè)時(shí)鐘下降沿不發(fā)送數(shù)據(jù)。而數(shù)據(jù)采樣發(fā)生在時(shí)鐘信號的上升沿。

SPI從端數(shù)據(jù)通信模塊

SPI從端數(shù)據(jù)通信模塊建模

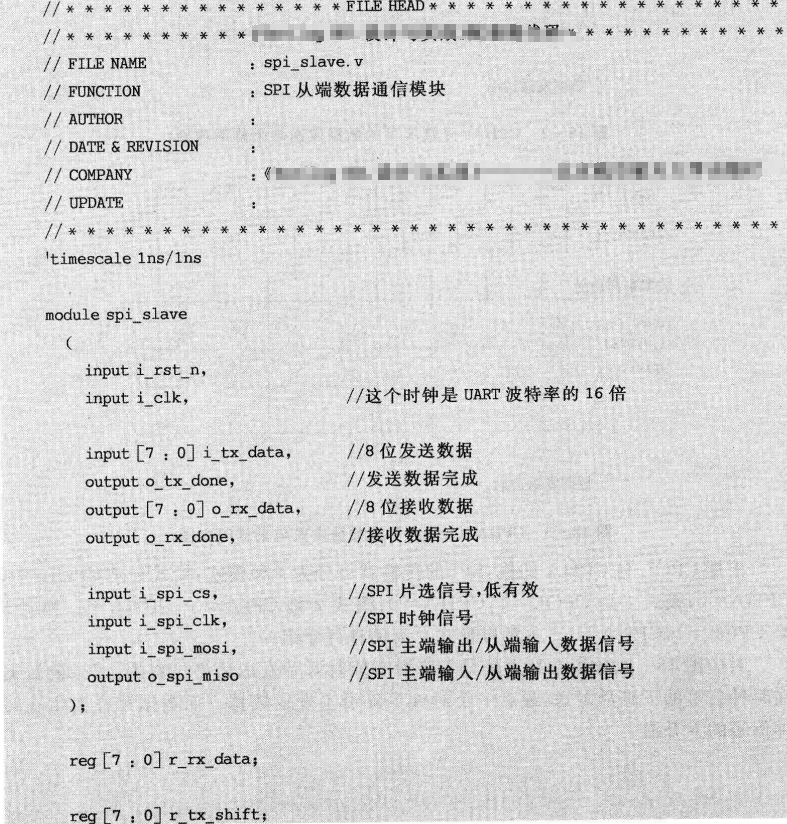

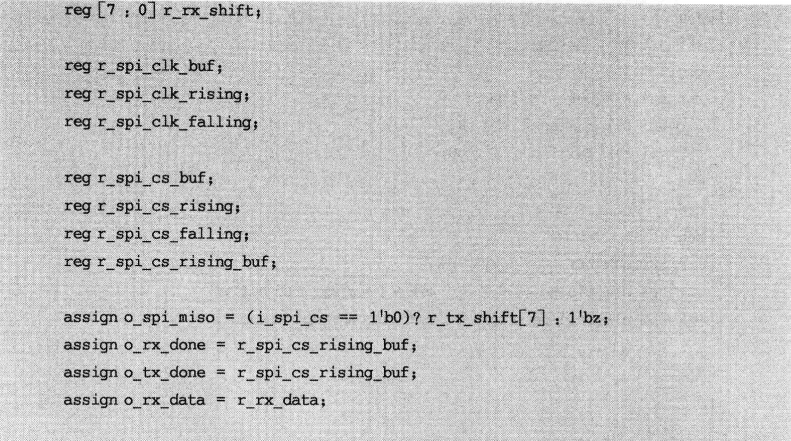

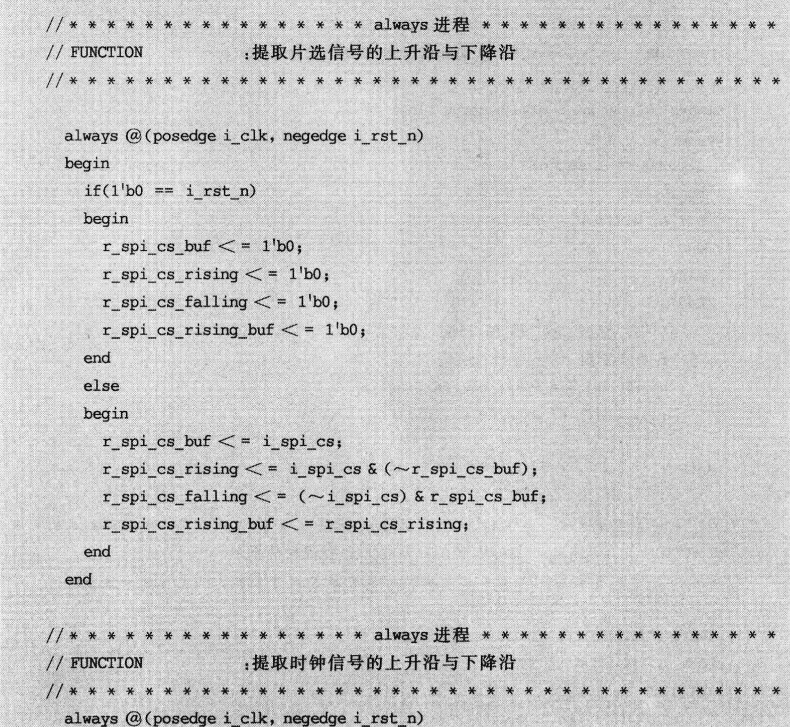

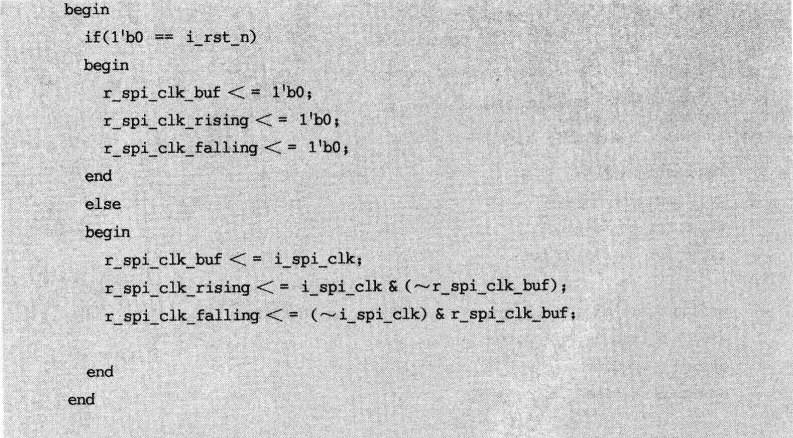

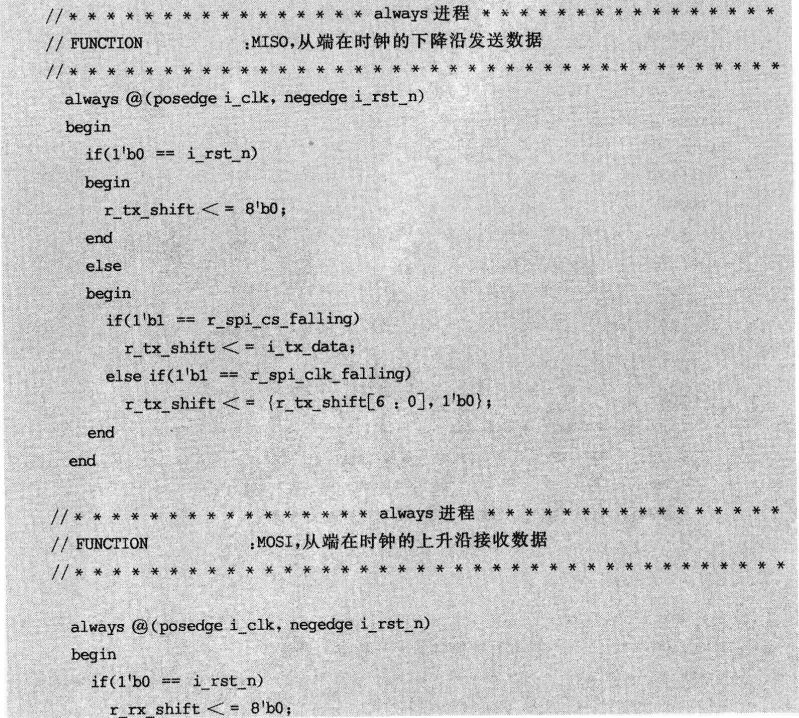

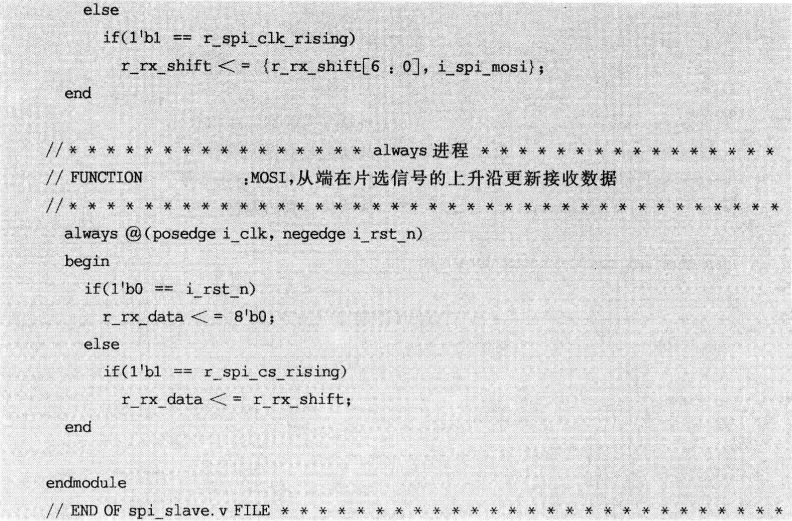

SPI數(shù)據(jù)通信分主端與從端,從端被動(dòng)地進(jìn)行數(shù)據(jù)通信的接收與發(fā)送。從端被動(dòng)的數(shù)據(jù)通信是根據(jù)時(shí)鐘信號與片選信號的邊沿進(jìn)行判斷的。當(dāng)片選信號的下降沿有效時(shí)發(fā)送最高位數(shù)據(jù),當(dāng)時(shí)鐘信號上升沿有效時(shí)進(jìn)行數(shù)據(jù)采樣接收數(shù)據(jù)。根據(jù)以上分析設(shè)計(jì)Verilog HDL代碼如【代碼18-1】所列。

【代碼18-1】

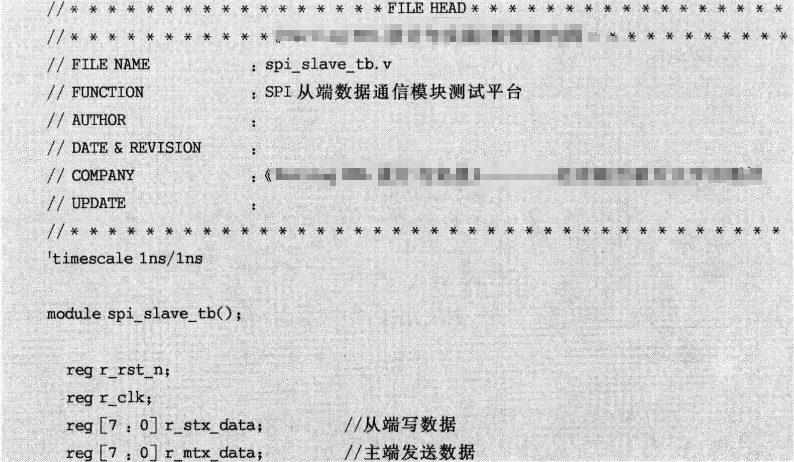

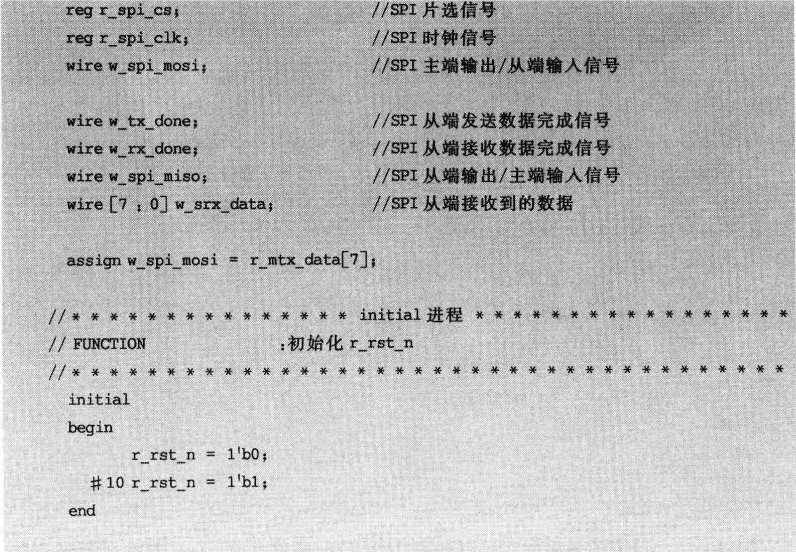

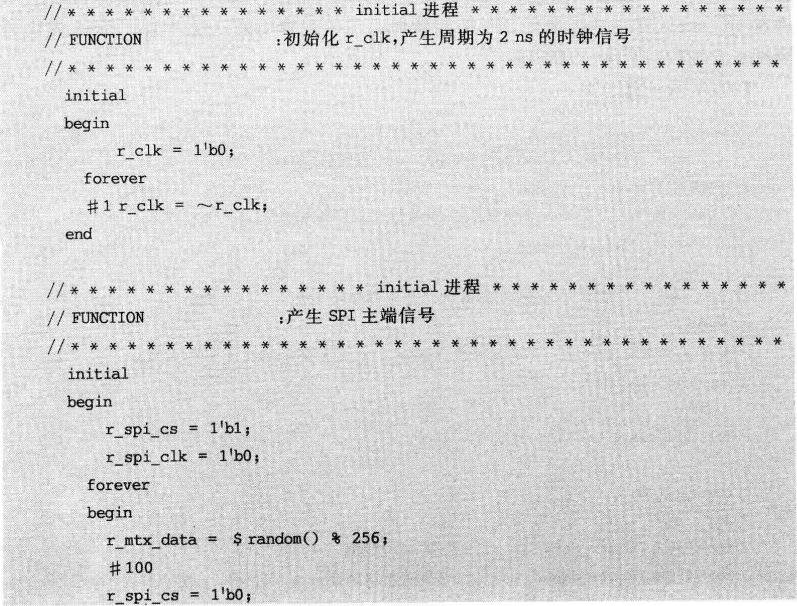

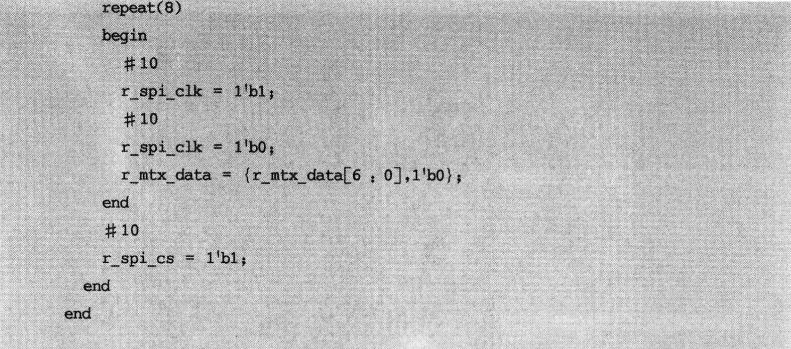

【代碼18-1】編譯無誤后,設(shè)計(jì)【代碼18-1】的測試平臺,通過觀察分析波形來確定spi_slave模塊是否滿足SPI從端數(shù)據(jù)通信的邏輯功能。設(shè)計(jì)spi_slave模塊的測試平臺如【代碼18-2】所列。

【代碼18-2】

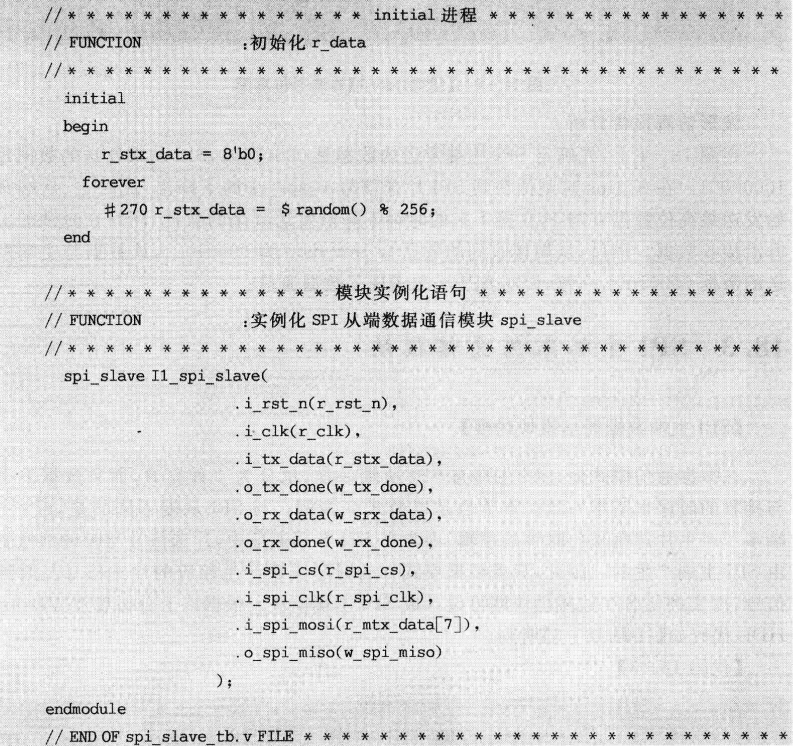

在ModelSim軟件中對【代碼18-1】進(jìn)行波形仿真,如圖18-4所示。

波形仿真報(bào)告分析

在圖18-4上,先確定SPI主端發(fā)送的數(shù)據(jù)是00001001,SPI從端發(fā)送的數(shù)據(jù)是10000001。在373 ns時(shí)刻捕獲到SPI片選信號r_spi_cs的下沿,此時(shí)主、從端開始發(fā)送最高位數(shù)據(jù)0與1,在接下來的時(shí)鐘下降沿發(fā)送其余的數(shù)據(jù),同時(shí)在時(shí)鐘的上升沿接收數(shù)據(jù)。最后,從端接收到的數(shù)據(jù)w_ srx_data為00001001,該數(shù)據(jù)與主端發(fā)送的數(shù)據(jù)00001001一致,說明SPI從端實(shí)現(xiàn)了數(shù)據(jù)通信。

SPI主端數(shù)據(jù)通佶模塊

SPI主端數(shù)據(jù)通信模塊建模

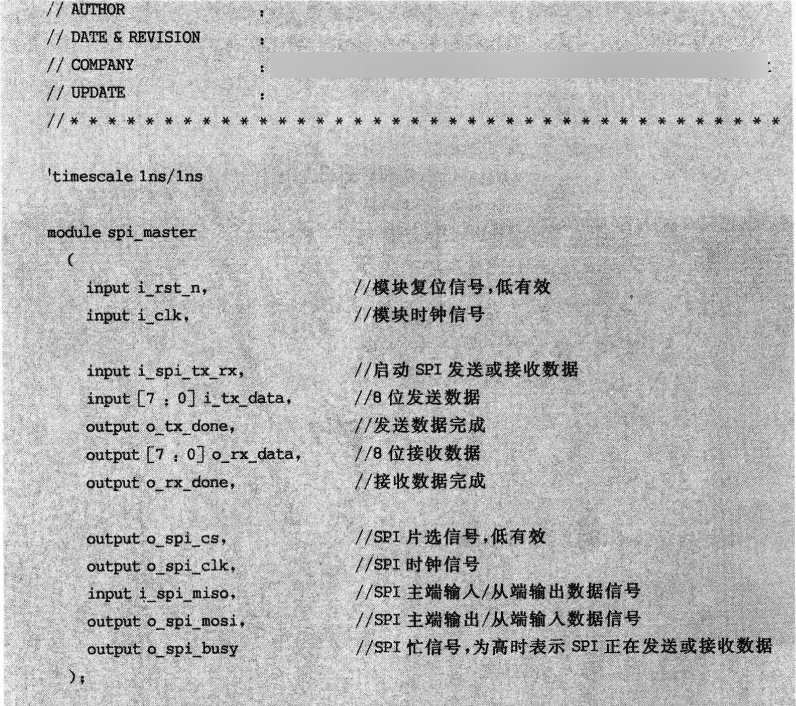

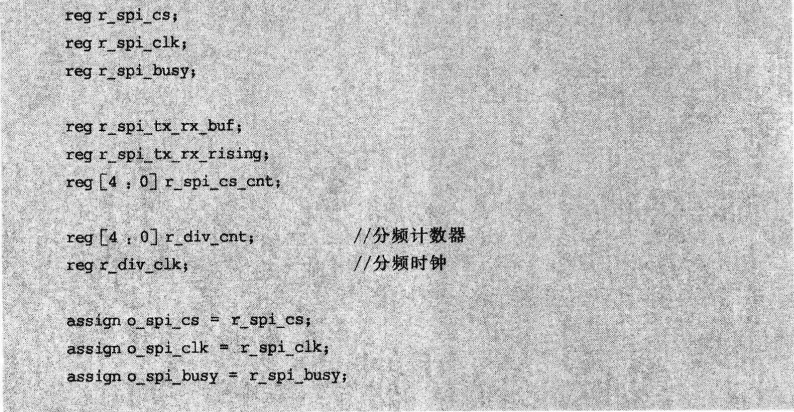

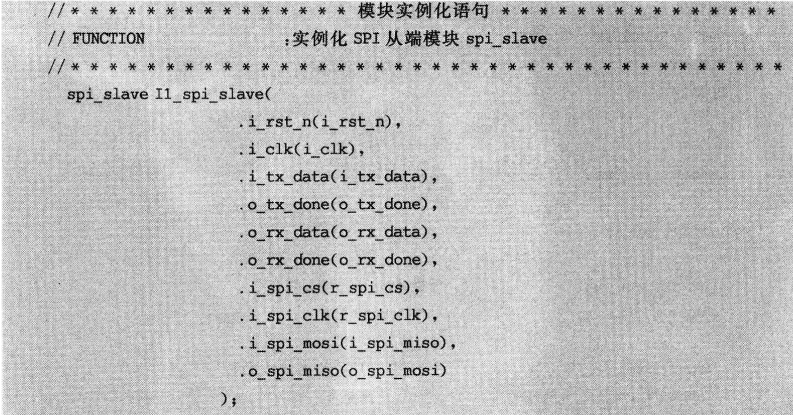

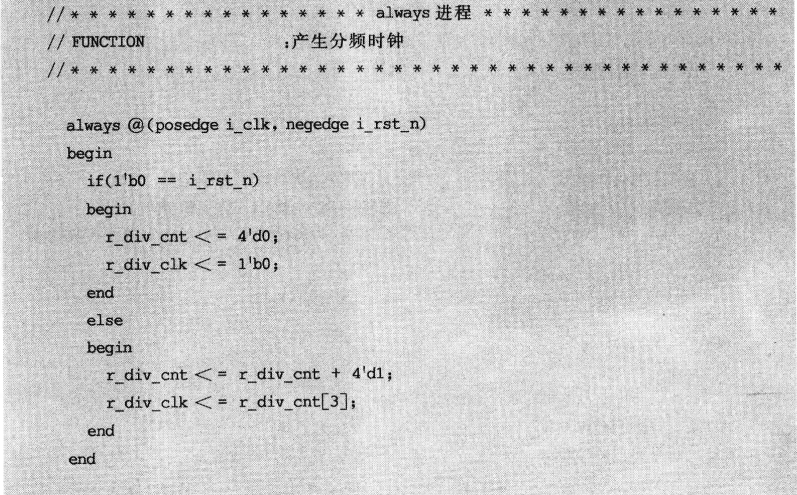

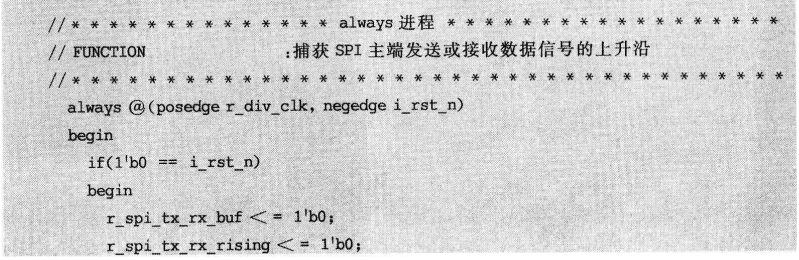

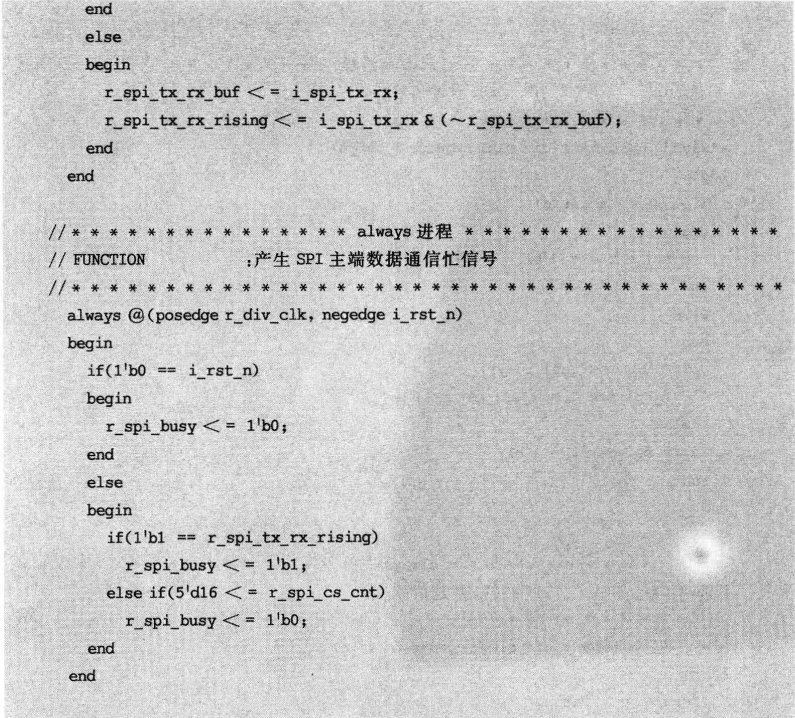

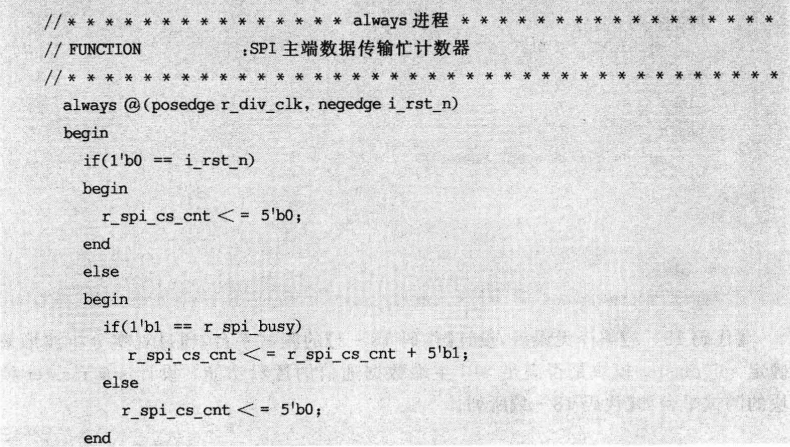

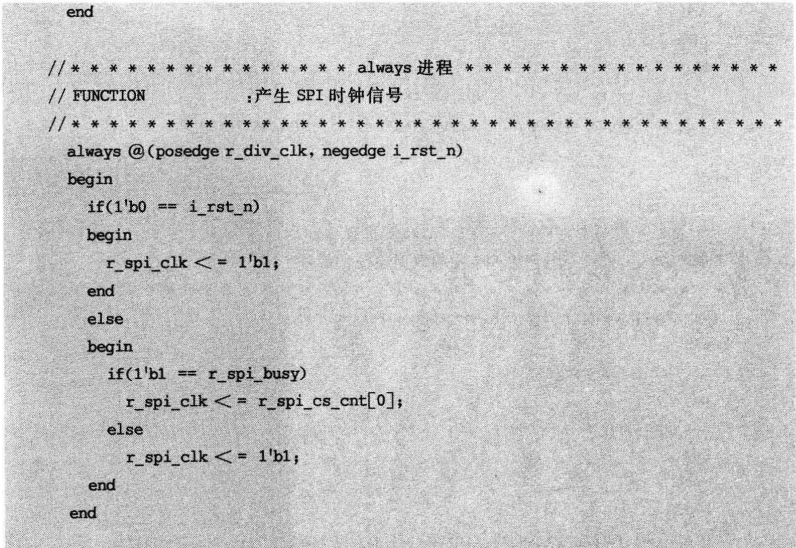

在數(shù)據(jù)通信模式上,SPI主端與SPI從端一樣,也分為4種模式,而且數(shù)據(jù)發(fā)送與接收的時(shí)序也基本一致。本節(jié)也是以模式0為例。與SPI從端不同的是,SPI主端多了產(chǎn)生片選信號與時(shí)鐘的邏輯,因?yàn)樵赟PI數(shù)據(jù)通信中,片選信號與時(shí)鐘信號是由SPI主端產(chǎn)生的。因此,只要根據(jù)模式0的時(shí)序關(guān)系產(chǎn)生相應(yīng)的片選信號與時(shí)鐘信號,再實(shí)例化SPI從端模塊即可設(shè)計(jì)成SPI主端模塊。根據(jù)以上分析設(shè)計(jì)Verilog HDL代碼如【代碼18-3】所列。

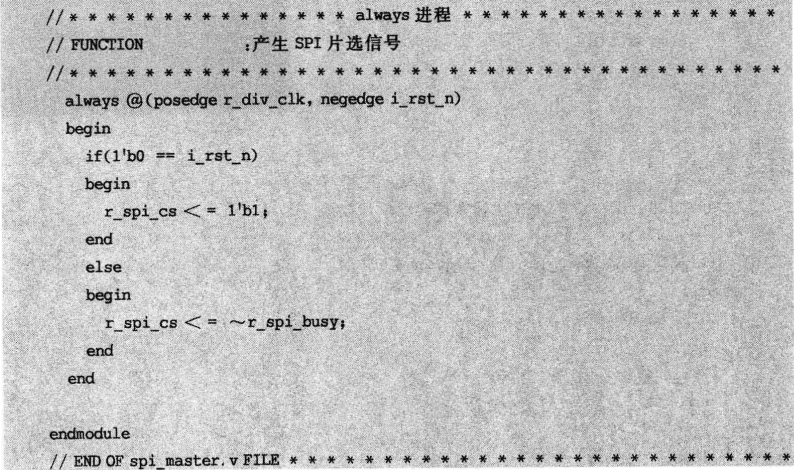

【代碼18-3】

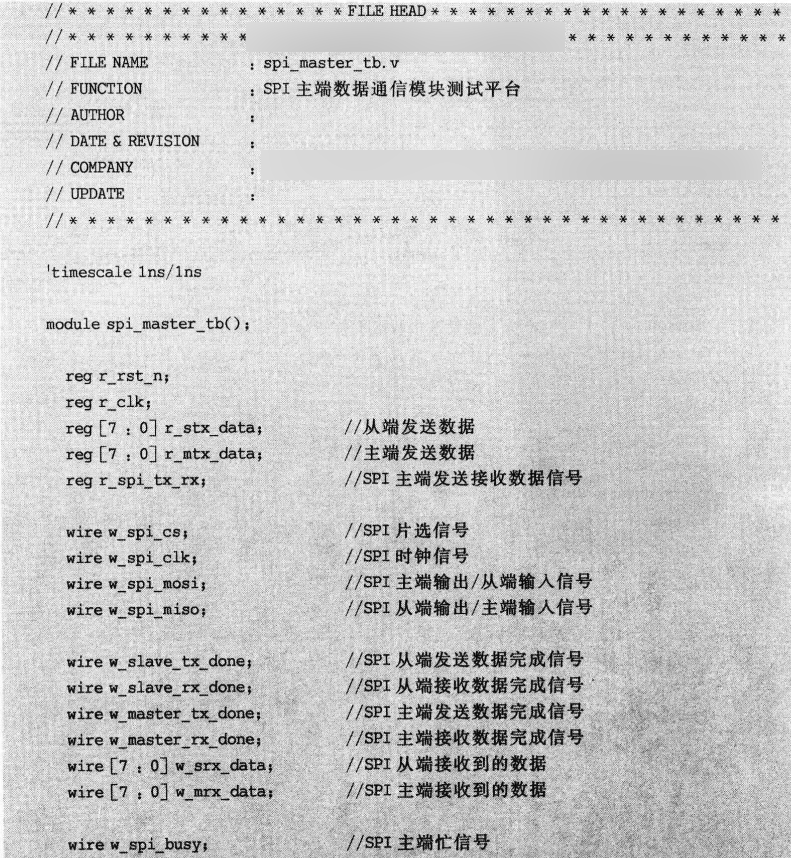

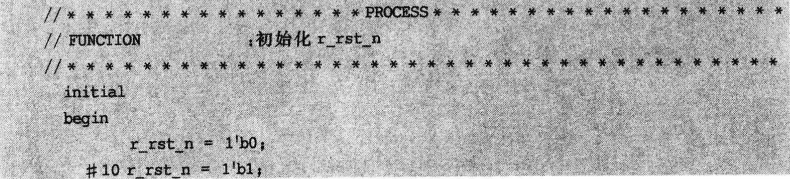

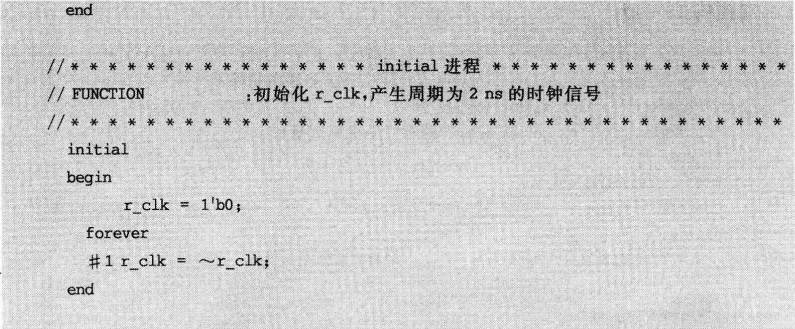

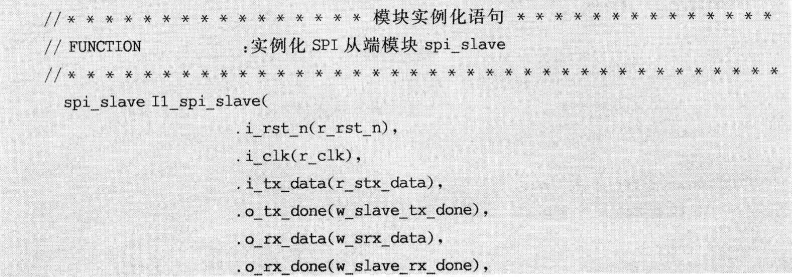

【代碼18-3】編譯無誤后,設(shè)計(jì)【代碼18-3】的測試平臺,通過觀察分析波形來確定spi_master模塊是否滿足SPI主端數(shù)據(jù)通信的邏輯功能。設(shè)計(jì)spi_master模塊的測試平臺如【代碼18-4】所列。

【代碼18-4】

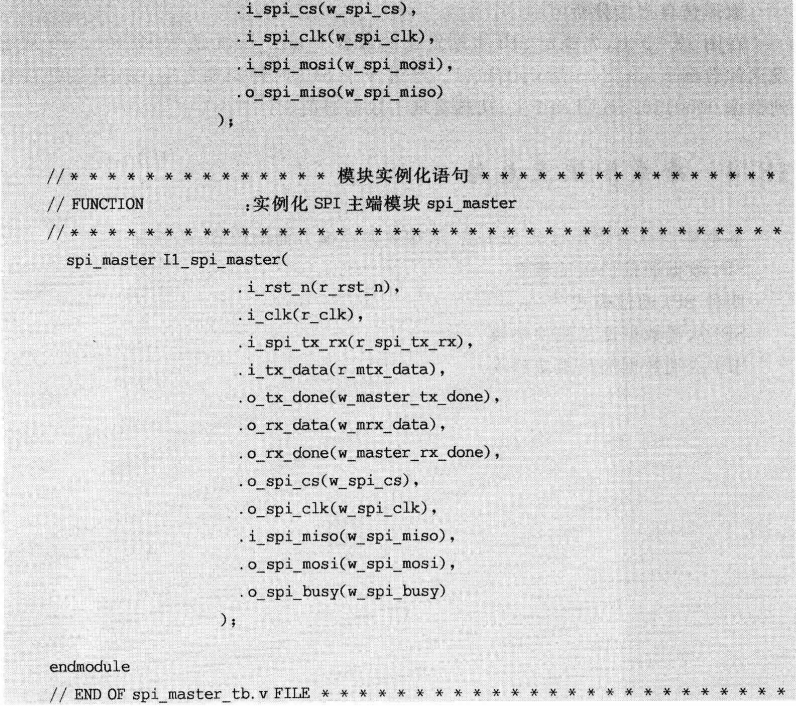

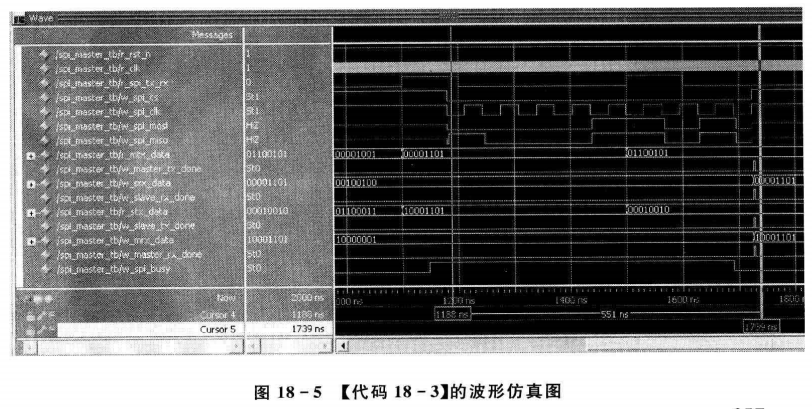

在ModelSim軟件中對【代碼18-3】進(jìn)行波形仿真,如圖18-5所示。

波形仿真報(bào)告分析

在圖18-5上,先確定SPI主端發(fā)送的數(shù)據(jù)r_mtx_data是00001101,SPI從端發(fā)送的數(shù)據(jù)r_stx_data是00001101。經(jīng)過8個(gè)SPI時(shí)鐘周期之后,主、從端都接收到數(shù)據(jù)00001101,說明SPI主、從端實(shí)現(xiàn)了數(shù)據(jù)通信。

本篇知識點(diǎn)主要介紹有關(guān)SPI主、從端數(shù)據(jù)通信建模方面的內(nèi)容,包括什么是SPI數(shù)據(jù)通信,四種SPI通信模式,以及SPI主、從端通信模塊建模的具體方法。另外,我們還講到如何基于Qsys的最小Nios II系統(tǒng)的搭建,基于其自帶的IP模塊的使用,包括了PIO模塊、UART模塊、定時(shí)器模塊以及SPI模塊等,基于Qsys的自定義外設(shè)、自定義指令的應(yīng)用實(shí)例。

-

SPI

+關(guān)注

關(guān)注

17文章

1669瀏覽量

90729 -

數(shù)據(jù)通信

+關(guān)注

關(guān)注

2文章

425瀏覽量

33665

原文標(biāo)題:FPGA設(shè)計(jì)應(yīng)用實(shí)例——SPI主從端數(shù)據(jù)通信實(shí)現(xiàn)

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)據(jù)通信基礎(chǔ)課件

數(shù)據(jù)通信基礎(chǔ)

數(shù)據(jù)通信的基本概念

單片機(jī)串行數(shù)據(jù)通信

什么是數(shù)據(jù)通信

無線移動(dòng)數(shù)據(jù)通信,無線移動(dòng)數(shù)據(jù)通信是什么意思

數(shù)據(jù)通信,數(shù)據(jù)通信原理是什么?

數(shù)據(jù)通信技術(shù)(華為資料)

數(shù)據(jù)通信基礎(chǔ)知識匯總

數(shù)據(jù)通信協(xié)議的簡介_數(shù)據(jù)通信協(xié)議有哪些

采用軟件模擬SPI總線實(shí)現(xiàn)雙單片機(jī)數(shù)據(jù)通信模塊的設(shè)計(jì)

詳談數(shù)據(jù)通信的傳輸損耗分類和原理

SPI主、從端數(shù)據(jù)通信建模的基礎(chǔ)知識

SPI主、從端數(shù)據(jù)通信建模的基礎(chǔ)知識

評論