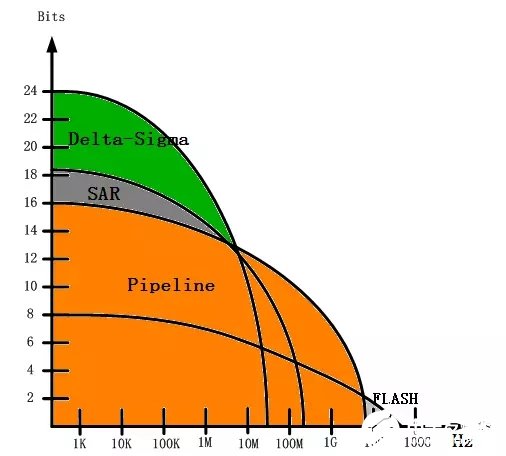

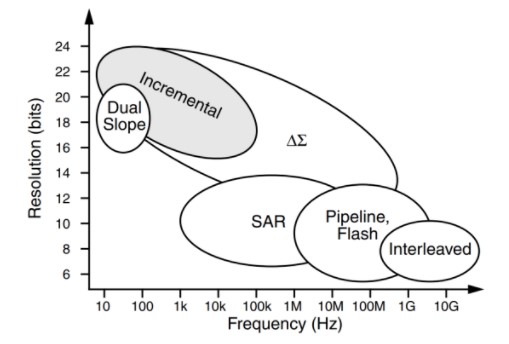

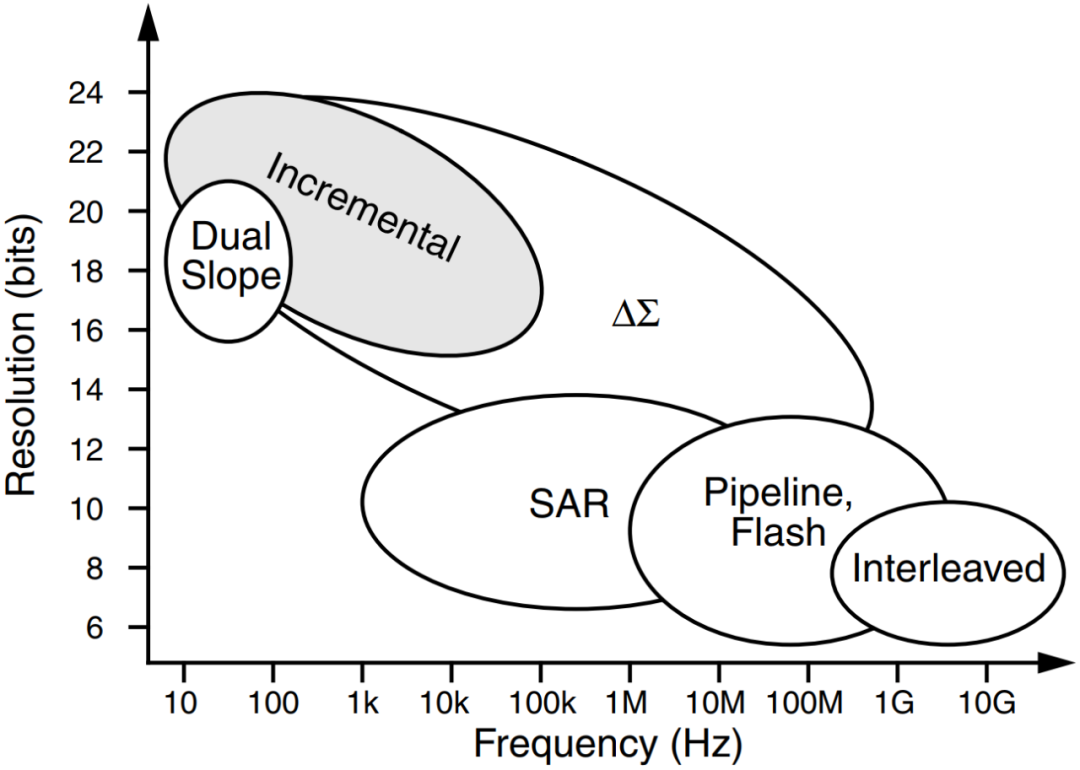

Sigma-Delta ADC是一種目前使用最為普遍的高精度ADC結構,在精度達到20位以上的場合,Sigma-Delta是必選的結構。通過采用過采樣、噪聲整形以及數字濾波技術,降低對模擬電路的設計要求,實現了其他類型的ADC無法達到的高精度和低功耗。通常情形下,各種類型ADC的精度與速度關系如圖1所示。

圖1 不同類型的ADC的精度和速度的對比

Sigma-Delta ADC的運作過程,就是把待測信號Vin與參考電壓(±Vref)之間的差值進行不斷的累積并通過反饋令這個差值趨于零。

實質上ADC就是除法器。

Dout=(Vin/Vref) * 2^n

一個分辨率為n位的ADC完成了一個以Vref為除數的除法,并且把結果用n位二進制數來表達。

那么什么是Sigma-Delta ADC?

Sigma-Delta最終實現的,與所有的ADC一樣,就是完成除法。模擬集成電路中除法器是不可實現的,但是模擬電路可以非常好的實現加法和減法(用運放及模擬開關對電容進行充放電)。Sigma-Delta ADC正是用加法和減法去實現除法的一種方式。

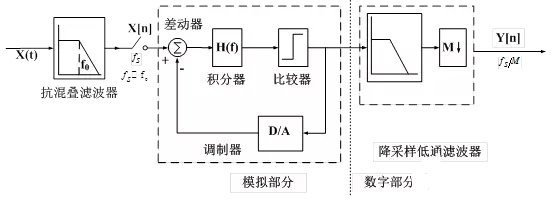

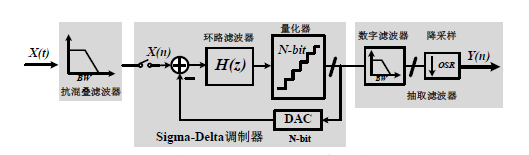

具體來說,如圖2所示,Delta-Sigma ADC的工作原理是由差動器、積分器和比較器構成調制器,它們一起構成一個反饋環路。調制器以大大高于模擬輸入信號帶寬的速率運行,以便提供過采樣。模擬輸入與反饋信號(誤差信號)進行差動(delta)比較。該比較產生的差動輸出饋送到積分器(sigma)中。然后將積分器的輸出饋送到比較器中。比較器的輸出同時將反饋信號(誤差信號)傳送到差動器,而自身被饋送到數字濾波器中。

圖2 過采樣ADC結構圖

這種反饋環路的目的是使反饋信號(誤差信號)趨于零。比較器輸出的結果就是1/0流。該流如果1密度較高,則意味著模擬輸入電壓較高;反之,0密度較高,則意味著模擬輸入電壓較低。接著將1/0流饋送到數字濾波器中,該濾波器通過降采樣與抽樣,將1/0流從高速率、低精度位流轉換成低速率、高精度數字輸出。

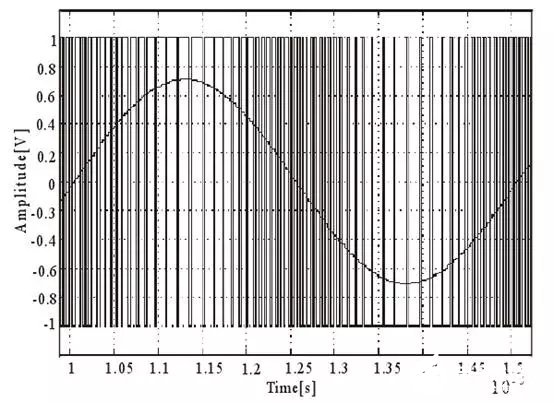

一個正弦波輸入信號與比較器輸出的碼流所對應的波形如圖3所示,輸出碼流隨著輸入信號幅值的變化而變化,當輸入信號處于波峰位置時,輸出碼流1占大多數;當輸入信號處于波谷位置時,輸出碼流0(圖3中,以-1表示)占大多數;輸入信號處于平衡位置時,輸出碼流1和0跳變激烈,各占50%。

圖3 正弦信號幅度與比較器輸出的碼流所對應的波形

sigma-delta ADC也有不同的結構,其特點可以如表1所示。

-

adc

+關注

關注

98文章

6452瀏覽量

544144 -

Sigma-Delta

+關注

關注

1文章

14瀏覽量

13664

發布評論請先 登錄

相關推薦

增量式Sigma-Delta ADC的性能需求

Sigma-Delta ADC常見問題解答

Sigma-delta轉換器

基于89C2051的Sigma-Delta ADC變化實現

UG-1525:評估ADuM7701 16位隔離Sigma-Delta ADC

UG-761:AD7714-3 24位低功耗Sigma-Delta ADC評估板

AD7791:低功率,Bufferd 24位Sigma-Delta ADC數據Sheet

AD7721:CMOS 16位,468.75 kHz,Sigma-Delta ADC數據Sheet

UG-1549:評估ADuM7703 16位隔離Sigma-Delta ADC

剖析Sigma-Delta ADC原理

增量式Sigma-Delta ADC與傳統結構的區別在哪?

一文解讀什么是Sigma-Delta ADC?

一文解讀什么是Sigma-Delta ADC?

評論