在2004年,楊百翰大學的地球微波遙感實驗室(MERS)開發(fā)了microSAR,展示了一種小型低成本LFM-CW SAR系統(tǒng)。在這一經驗的基礎上,BYU與Artemis Inc.合作開發(fā)了一個更強力的microASAR,克服了原有設計的許多局限性。

該microASAR設計的一個關鍵要素是過采樣數字接收機。 過采樣提供了三個主要優(yōu)點:

1. 信號de-chirped可以在任意中頻(IF),從而實現更好的RF濾波;

2. 通過數字濾波降低量化噪聲;

3. SAR能夠在de-chirped和脈沖模式下靈活切換。

基于BYU的microSAR系統(tǒng)雖然工作正常,但研究發(fā)現由于濾波器的脈沖響應較長,用于抑制饋電數據的High-Q濾波器會引起回波數據的失真。而使用偏置de-chirp可以避免這種失真。我們把這個系統(tǒng)稱為偏置IF LFM-CW。

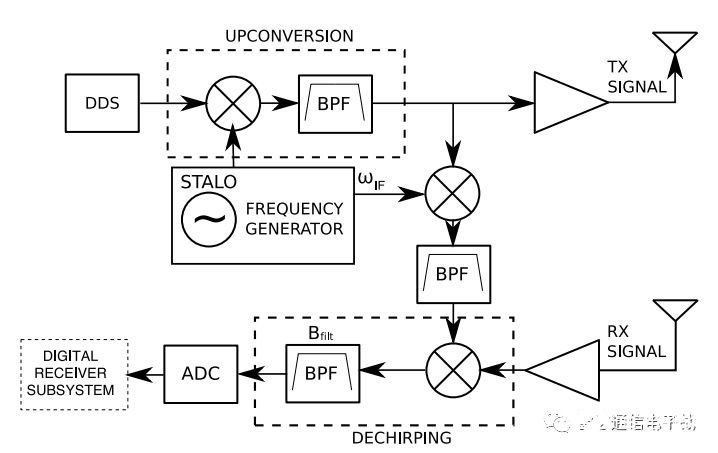

偏置 IF LFM-CW SAR的流程圖見圖1。首先使用ωIF對發(fā)送信號進行部分混頻后濾波。然后再與接收到的信號混頻,產生的差分分量與傳統(tǒng)的LFM-CW中的差分分量相似,但在偏置IF有所不同。有用信號在IF較高的部分,更容易找到High-Q濾波器,使其具有線性相位、銳利截止頻率和更好地抑制泄露。

使用一個高速ADC和FPGA就可以實現更高的性能與靈活性。 選擇一個可以采樣接收到的chirp全部帶寬的ADC可以實現脈沖模式以及在任意IF的de-chirp操作。FPGA通過提供充足的I/O端口來集成大量組件和通信設備,進一步增強了設計。FPGA提供了靈活的操作模式。

如果忽略相關能量的功耗成本以及ADC分辨率具有可比性,最好以最高速率對接收信號進行采樣,能夠使得量化噪聲減小。因為量化噪聲是依據采樣頻率,以更高的速率采樣信號可將噪聲譜擴展到更寬的帶寬,從而降低信號帶寬上的量化噪聲功率。

過采樣

數字信號處理的課程往往忽視振幅量化的影響,然而在LFM-CW系統(tǒng)中輸入信號的量化是噪聲的主要來源。一個完全隨機的信號在步長q量化時,它相當于在范圍內均勻地增加白噪聲。通過對信號采樣后進行適當的濾波,量化噪聲與信號比(QNSR)都降低了約3dB,信號被過采樣的因子為2。

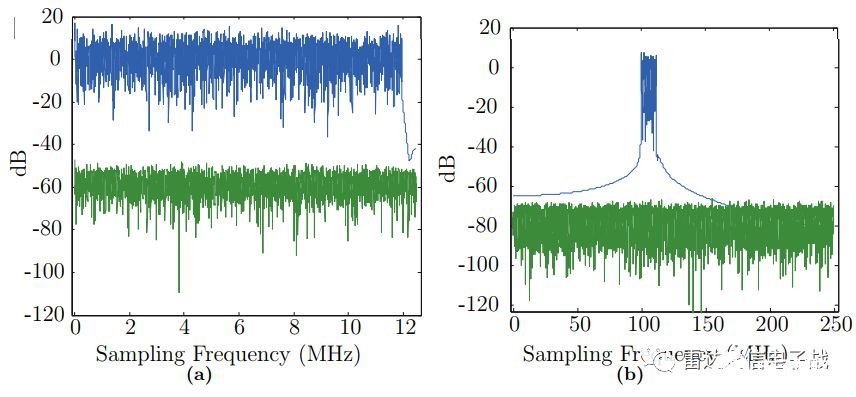

圖2 展示了過采樣獲得的SNR增益。 在圖2(a)仿真的LFM-CW回波以僅高于Nyquist 的速率進行采樣。信號與量化噪聲的間隔約為64dB。圖2(b)中的信號被過采樣因子約為18,比特數與圖2(a)相同。信號與量化噪聲的間隔則約為75dB。適當的采用帶通濾波器,過采樣可減少11dB的QNSR。

圖 2 用相應的量化噪聲來描述子采樣(a)和過采樣(b)信號的頻譜的圖。注意:過采樣的信號具有較大的信號,與噪聲間隔約為11dB;兩個圖中的信號頻譜具有相同的帶寬,圖形的頻率縮放是不同的。

對信號進行采樣后,下一步是在不影響數據完整性的情況下降低數據速率(抽取)。 此過程中有兩個步驟,第一步是濾掉量化噪聲,將信號變到基帶,以降低濾波后的信號采樣頻率。所有濾波功能都是采用數字多相濾波器實現,這種濾波器結合了過濾器和解碼器的操作, 從而減少了FPGA資源。

降低數據速率的第二步是預加。預加是將順序的回波加在一起,具有低通濾波多普勒頻譜的效果。預加可以用于microASAR數據,因為高PRF可用于分離泄露和第一個目標,PRF遠遠高于信號的多普勒帶寬所要求的水平。

從信號處理的角度來看,預加和濾波的順序是可改變的。但預加和濾波的順序極大地影響了實現的內存和硬件要求。還應該注意的是,在每次信號處理操作后,數據的比特寬度都會增加,以防止溢出。

FPGA實現

為使所需系統(tǒng)達到上述的靈活性和高性能,microASAR數字接收機配備了一個12bit 500MHz ADC和一個Xilinx Virtex-5 FX-30T FPGA。這種組合可以使microASAR能對200MHz帶寬的發(fā)射信號進行完整的采樣,并在各種de-chirp模式下工作。本節(jié)簡要介紹了用于 de-chirp操作的FPGA實現的總體設計,并概述了所使用的設計方略。

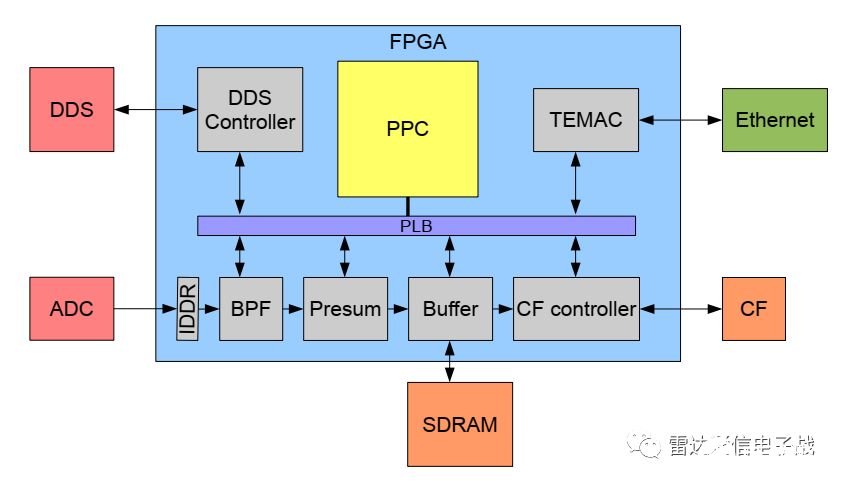

FPGA實現框圖如圖3 所示。FPGA上的嵌入式PowerPC處理器用于控制和協調完整數字接收機的操作,大多數參數可以通過與powerPC的以太網通信來設置。正常的信號數據路徑是從ADC到濾波子系統(tǒng),然后通過緩存器存入存儲卡。

數據路徑也可以中斷并通過以太網端口傳輸。ADC中的數據立即被分成兩個交錯的數據路徑,使得濾波器的時鐘速率可以減少兩倍來緩解時序約束。這兩個交錯數據流相位差180度,并在之后重組。

這個濾波子系統(tǒng)包括所有的濾波,預加,抽取步驟,并且能夠配置不同的操作參數。 濾波子系統(tǒng)由多相濾波器組成,以處理大量的操作并減少FPGA資源。多相濾波器減少量化噪聲并限制了信號頻譜以便通過抽取數字采樣數據將信號轉換為DC。

對于microASAR,這是通過采用用12MHz的帶通濾波器(BPF),從ωIF開始以20倍抽取,提供約3.3位的分辨率增加。這使信號的有效位數(ENOB)達到16位ADCs,這些ADC通常僅適用于較低的采樣率。預加在濾波之后進行,以減少內存要求,從而使假定可以在on-chip memory中計算。

若先執(zhí)行預加可以減少濾波所需的乘法器。不過,在大多數情況下,這需要外部高速存儲,從而增加功耗和開發(fā)時間。用多相濾波器替換單相濾波器,后接混頻器和多相低通濾波器,可以存儲更大的帶寬。同樣,除了使用混頻器和低通濾波器,同樣可以使用FFT。這兩種方法都需要更多的FPGA資源,并由于定點乘法和查找正余弦表而給信號增加噪聲。

這種簡潔的設置最大程度地減少了FPGA資源,只需改變PRF即可對各種應用進行操作。 降低PRF可以降低調頻斜率,壓縮de-chirped后的目標。模擬和數字濾波器有效地測量de-chirped數據的門。因此,通過將PRF從7-14kHz改變,SAR可以在5-1000米的高度、30-2500米的幅寬和0-150m/的速度下工作。雖然部分參數在機載作業(yè)中無法達到,但microASAR符合地面系統(tǒng)使用條件。

來源:雷達通信電子戰(zhàn)

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601856 -

濾波器

+關注

關注

160文章

7728瀏覽量

177684 -

SAR

+關注

關注

3文章

414瀏覽量

45898 -

數字接收機

+關注

關注

1文章

23瀏覽量

11621

發(fā)布評論請先 登錄

相關推薦

用于 de-chirp操作FPGA實現的總體設計

用于 de-chirp操作FPGA實現的總體設計

評論