在本教程中,我們將來聊一聊有關如何在 Vitis HLS 中使用 AXI4-Lite 接口創(chuàng)建定制 IP 的基礎知識。

注:在 Vivado HLS 中使用 AXI 創(chuàng)建 IP 的過程與使用 Vitis HLS 的過程不同。如果您想要在 Vivado HLS 中創(chuàng)建 AXI IP,請參閱UG902。

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/c_ug902-vivado-high-level-synthesis.pdf

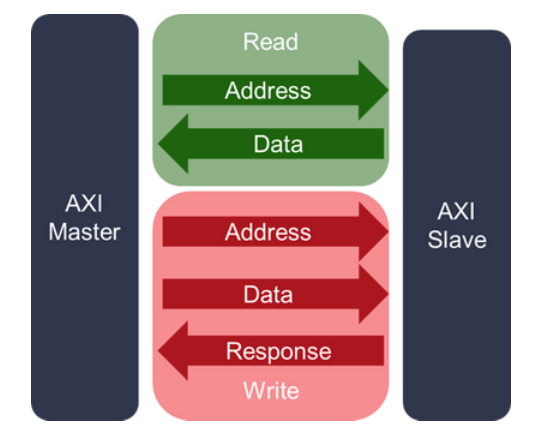

AXI4-Lite 屬于基本 AXI 通信協(xié)議。它常用于簡單的低吞吐量存儲器映射通信(例如,往來于控制寄存器和狀態(tài)寄存器的通信)。

如上圖所示,AXI4-Lite 接口可設置為只讀(僅包含 2 條讀取通道)或只寫(僅包含 3 條寫入通道)。

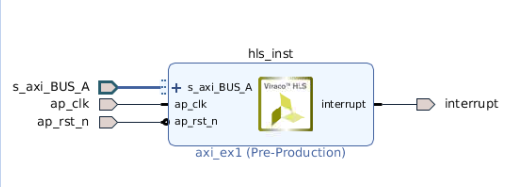

在本教程中,我們將創(chuàng)建以下 IP,并使用 s_axi_BUS_A 作為我們的 AXI4-Lite 接口:

本教程結(jié)束時,您將能夠

了解在 Vitis HLS 中創(chuàng)建 AXI4-Lite 接口的相關基礎知識。

了解 Vitis HLS 中的編譯指示相關信息,此類編譯指示用于定義所使用的 AXI 接口。

打開 AXI4-Lite 設計示例

在 Vitis HLS 中提供了 AXI4-Lite 的設計示例。要打開 AXI4-Lite 的設計示例,請遵循以下步驟進行操作:

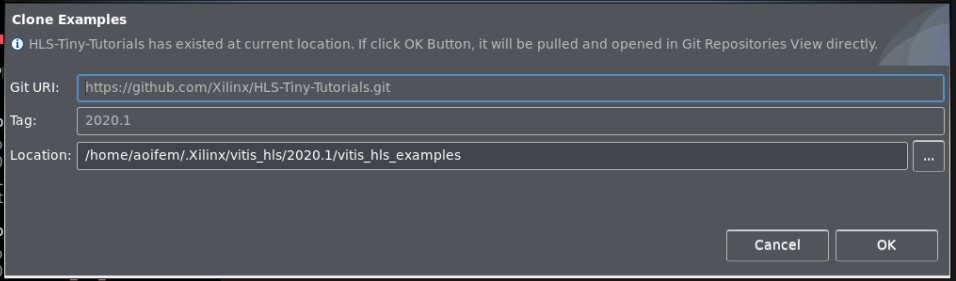

1. 打開 Vitis HLS GUI。在首頁屏幕中,選擇“克隆示例 (Clone Examples)”選項以便從 GitHub 復制 Vitis HLS 設計示例:

2. 在彈出選項卡中,選擇示例的保存位置,然后單擊“確定 (OK)”:

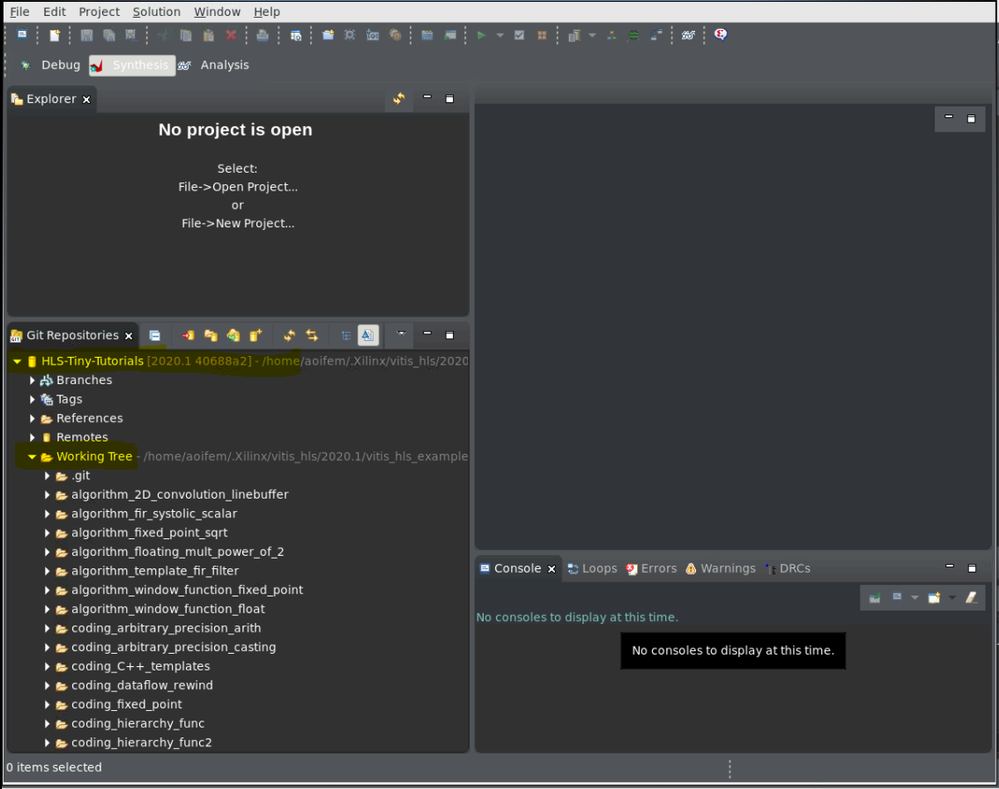

3. 在下一個屏幕中,設計示例將顯示在左下角。選中“HLS 微教程 (HLS Tiny Tutorials)”和“工作樹結(jié)構 (Working Tree)”旁的箭頭即可查看所有可用示例。

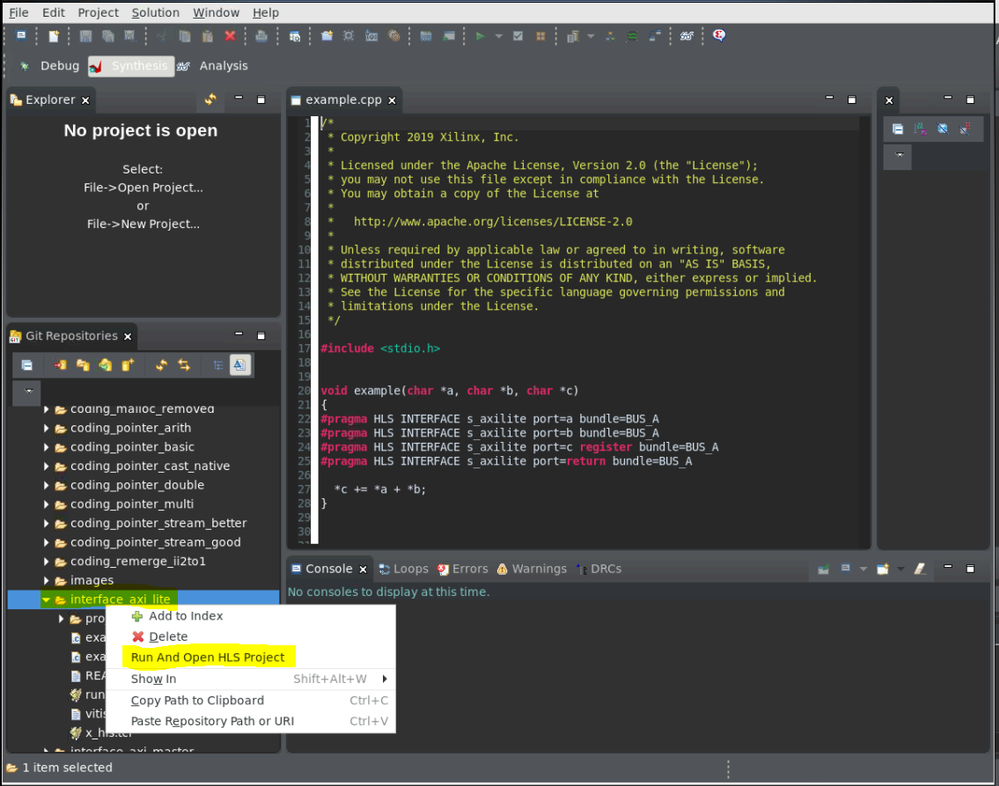

4. 向下滾動,找到 interface_axi_lite 示例。右鍵單擊文件夾名稱,然后選中“運行并打開 HLS 工程 (Run and Open HLS Project)”選項。

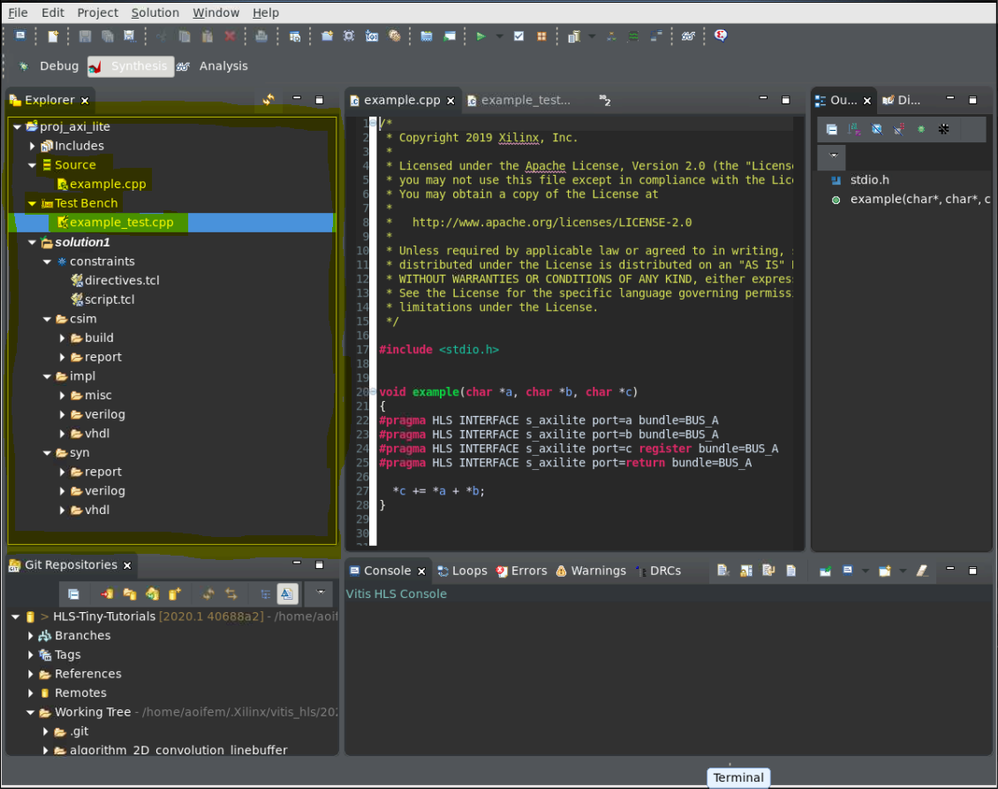

5. 完成此操作后,將在左側(cè)選項卡中打開此工程。雙擊 example.cpp 和 example_test.cpp 以查看源代碼和測試激勵文件。

源代碼詳解

此示例包含 2 個主要文件:

Example.cpp - 此代碼將綜合到 RTL 中以創(chuàng)建“簡介”中所示的 IP。此 IP 將與 Vivado Design Suite 中的其它 IP 相結(jié)合,并最終被放置到您的硬件上。

Example_test.cpp - 此測試激勵文件將用于確保 example.cpp 按期望方式運行。Example.cpp 算法將通過如下方式進行檢查:將該算法的輸出與測試激勵文件中執(zhí)行的“期望數(shù)據(jù) (golden data)”計算結(jié)果進行比較。只要黃金數(shù)據(jù)與 example.cpp 的返回結(jié)果相匹配,HLS 中的測試激勵文件就會返回 0。

選中左側(cè)列中“源代碼 (Source)”下的 example.cpp 即可打開源代碼。接下來我們來詳細看下代碼:

函數(shù)實參

void example(char *a, char *b, char *c)

進入庫之后首先可看到的是 example(); 函數(shù)。只要您熟悉基于 C 語言的設計,就不難發(fā)現(xiàn),通過形參(如上述示例中的 char *a、char *b 和 char*c)即可瞬間執(zhí)行所有輸入和輸出操作。

在 RTL 設計中,數(shù)據(jù)通過端口進出 IP。這些端口可使用特定 I/O 協(xié)議(例如,AXI4-Lite、AXI4-Stream 等)來進行操作,這樣即可保證 IP 塊之間能夠進行標準化的通信。

對于進出 IP 的每一條數(shù)據(jù),都應將其指定為主源文件中的一個獨立函數(shù)實參。稍后,該函數(shù)實參將被綜合成硬件 (RTL) 中的一個“端口”。

注:端口實際上可通過 3 種不同方法來創(chuàng)建,但本教程將主要講解采用函數(shù)實參的方法。

端口衍生自:

指定的任意函數(shù)級協(xié)議。

函數(shù)實參。

全局變量(供頂層函數(shù)訪問,在其作用域范圍外定義)。

注:由于 AXI4-Lite 接口中的變量為函數(shù)實參,因此在 C 語言代碼中無法為其指定默認值。因此,無法為 AXI4-Lite 接口中的任何寄存器指定默認值。這些寄存器可通過 config_rtl 命令進行復位來實現(xiàn),但不能為其指定任何其它默認值。(請參閱控制復位行為以了解詳細信息)。

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html

接口編譯指示

接下來,我們來看看編譯指示接口。

首先逐一了解下其中每個組件:

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c register bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

我們需要把 IP 的輸入/輸出定義為 s_axilite,這樣才能使用 AXI4-Lite 協(xié)議。如果我們的代碼中不包含此行,那么數(shù)據(jù)輸入/輸出將綜合到基本連線中,并且將不含關聯(lián)的握手信號。在此情況下,輸入將保持穩(wěn)定狀態(tài)直至執(zhí)行讀取輸入操作為止,一旦未謹慎執(zhí)行此操作,就可能導致錯誤。

接口編譯指示格式如下:

#pragma HLS interface

其中:

port=

(register):這是可選關鍵字,用于寄存(即存儲)信號和所有關聯(lián)的協(xié)議信號。它會導致信號保持直至至少完成函數(shù)執(zhí)行的最后一個周期為止。

bundle=

s_axilite port=return:用于設置類型為 s_axilite 的函數(shù)實參,端口名稱“return”將在 IP 塊中創(chuàng)建中斷信號。您可通過 AXI4-Lite 接口和 C 語言驅(qū)動程序文件來完成中斷編程。如需了解更多信息,請參閱此處

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html#auo1539734222936

注:如果任意頂層函數(shù)實參指定為 AXI4-Lite 接口,則函數(shù)返回也必須指定為 AXI4-Lite 接口。

注 2:默認情況下,HLS 會為分組到同一個 AXI4-Lite 接口的每個端口分配地址。Vitis HLS 在C 驅(qū)動程序文件(如下鏈接)中提供了分配的地址。要顯式定義地址,可使用 offset 選項。在 AXI4-Lite 接口中,Vitis HLS 保留地址 0x0000 到 0x000C,用于塊級 I/O 協(xié)議信號和中斷控制。

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html#auo1539734222936

函數(shù)主體

*c += *a + *b;

在該函數(shù)中,可以精確定義希望此 IP 執(zhí)行的操作,此 IP 將導入 2 個值(a 和 b)并將結(jié)果 (c) 存儲在寄存器中。為測試功能,測試激勵文件將為 a 和 b 提供 example() 函數(shù),并將其與自己計算 a+b 所得的值進行比較。如果結(jié)果相匹配,那么測試激勵文件應始終返回 0,并且 c 仿真即可通過。

-

接口

+關注

關注

33文章

8265瀏覽量

149985 -

C語言代碼

+關注

關注

0文章

10瀏覽量

9132

原文標題:開發(fā)者分享 | Vitis HLS 中的 AXI4-Lite 簡介-上

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

Zynq中AXI4-Lite和AXI-Stream功能介紹

創(chuàng)建AXI Sniffer IP以在Vivado IP Integrator中使用教程

可以在EDK中使用Axi4Stream接口/總線嗎?

AXI4-lite端口可以保持未連接狀態(tài)嗎?

【正點原子FPGA連載】第四章呼吸燈實驗-領航者ZYNQ之HLS 開發(fā)指南

使用Vitis HLS創(chuàng)建屬于自己的IP相關資料分享

將DSP設計融入嵌入式系統(tǒng)的AXI4-Lite接口

如何創(chuàng)建基本AXI4-Lite Sniffer IP以對特定地址上正在發(fā)生的讀寫傳輸事務進行計數(shù)

Vitis HLS工具簡介及設計流程

AXI4 、 AXI4-Lite 、AXI4-Stream接口

如何在Vitis HLS中使用C語言代碼創(chuàng)建AXI4-Lite接口

使用AXI4-Lite將Vitis HLS創(chuàng)建的IP連接到PS

自定義AXI-Lite接口的IP及源碼分析

如何在Vitis HLS GUI中使用庫函數(shù)?

如何在Vitis HLS中使用C語言代碼創(chuàng)建AXI4-Lite接口

如何在Vitis HLS中使用C語言代碼創(chuàng)建AXI4-Lite接口

評論