硅材料根據(jù)晶胞的排列方式不同,分為單晶硅和多晶硅。單晶硅和多晶硅最大的區(qū)別是單晶硅的晶胞排是有序的,而多晶硅是無序的。在制造方法方面,多晶硅一般是直接把硅料倒入坩堝中融化,然后再冷卻而成。單晶硅是通過拉單晶的方式形成晶棒(直拉法)。在物理性質方面,兩種硅的特性相差較大。單晶硅導電能力強,光電轉換效率高,單晶硅光電轉換效率一般在 17%~25%左右,多晶硅效率在 15%以下。

▲半導體硅片和光伏硅片

▲單晶硅晶胞結構

光伏硅片:由于光電效應,且單晶硅優(yōu)勢明顯,所以人們使用硅片完成太陽能到電能的轉換。在光伏領域使用的一般為圓角方形的單晶硅電池片。價格較便宜的電多晶硅片也有使用,但轉換效率較低。

▲單晶硅電池片正反面

▲多晶硅電池片正反面

由于光伏硅片對純度、曲翹度等參數(shù)要求較低,所制造過程相對簡單。以單晶硅電池片為例,第一步是切方磨圓,先按照尺寸要求將單晶硅棒切割成方棒,然后將方棒的四角磨圓。第二步是酸洗,主要是為了除去單晶方棒的表面雜質。第三步是切片,先將清洗完畢后的方棒與工板粘貼。然后將工板放在切片機上,按照已經(jīng)設定好的工藝參數(shù)進行切割。最后將單晶硅片清洗干凈監(jiān)測表面光滑度,電阻率等參數(shù)。

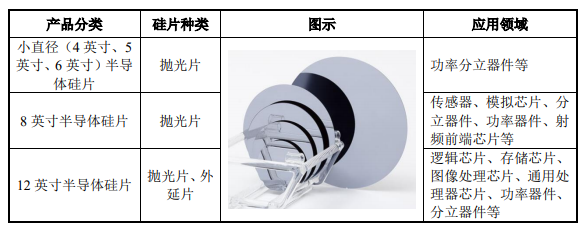

半導體硅片:半導體硅片比光伏硅片的要求更高。首先,半導體行業(yè)使用的硅片全部為單晶硅,目的是為了保證硅片每個位臵的相同電學特性。在形狀和尺寸上,光伏用單晶硅片是正方形,主要有邊長 125mm,150mm,156mm 的種類。而半導體用單晶硅片是圓型,硅片直徑有 150mm(6 寸晶圓),200mm(8 寸晶圓)和 300mm(12 寸晶圓)尺寸。在純度方面,光伏用單晶硅片的純度要求硅含量為 4N-6N 之間(99.99%-99.9999%),但是半導體用單晶硅片在 9N(99.9999999%)-11N(99.999999999%)左右,純度要求最低是光伏單晶硅片的 1000 倍。在外觀方面,半導體用硅片在表面的平整度,光滑度和潔凈程度要比光伏用硅片的要求高。純度是光伏用單晶硅片和半導體用單晶硅片的最大不同。

▲半導體硅片制造過程

摩爾定律的發(fā)展就是硅片的發(fā)展。由于半導體用硅片是圓形,所以半導體硅片也叫“硅晶圓”或者“晶圓”。晶圓是芯片制造的“基底”,所有的芯片都是在這個“基底”上制造。在半導體用硅片的發(fā)展歷程中,主要有尺寸和結構兩個方向。

在尺寸上,硅片的發(fā)展路徑是越來越大:在集成電路發(fā)展初期,使用的是 0.75 英寸晶圓。而增加晶圓面積,增加單片晶圓上的芯片個數(shù)可以降低成本。1965 年左右,隨著摩爾定律的提出,集成電路技術和硅片都迎來快速發(fā)展期。硅片經(jīng)歷了4 寸、6 寸、8 寸和 12 寸等節(jié)點。自從2001 年英特爾和 IBM聯(lián)合開發(fā)了 12 寸晶圓芯片制造后,現(xiàn)主流硅片就是12寸晶圓,占比約為 70%,但 18寸(450mm)晶圓的已經(jīng)提上議程。

▲不同尺寸晶圓的參數(shù)

▲硅片大小的發(fā)展

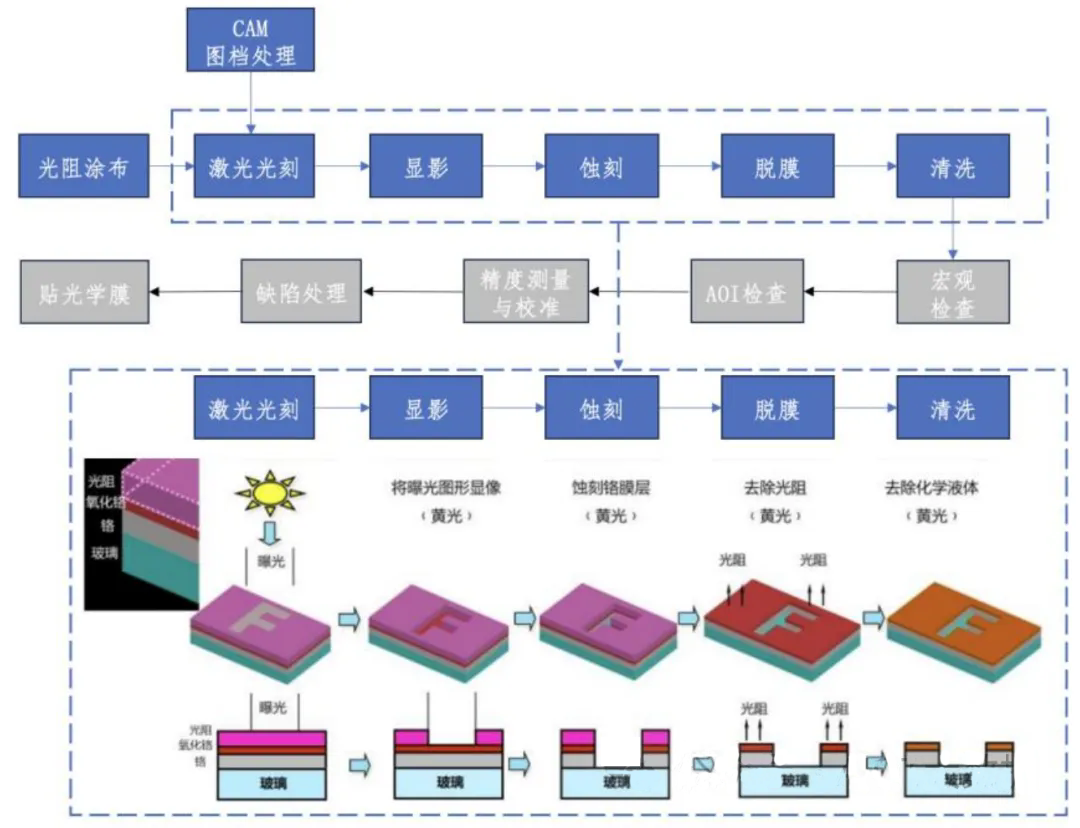

在結構方面,硅片的發(fā)展方向是越來越復雜:集成電路發(fā)展初期是只有邏輯芯片一種,但是隨著應用場景不斷增多,邏輯芯片、功率器件、模擬芯片、數(shù)模混合芯片,flash/Dram 存儲芯片、射頻芯片等等相繼出現(xiàn),使得硅片在結構上出現(xiàn)了不同的形態(tài)。現(xiàn)在,主要有以下三種:

PW(Polish Wafer):拋光片。拉單晶后直接切割得到的硅片由于在光滑度或者翹曲度方面不盡完美,所以首先要經(jīng)過拋光處理。這種方式也是最原始硅片的處理方式。

AW(Anneal Wafer):退火晶圓。隨著制程技術的不斷發(fā)展,晶體管特征尺寸的不斷縮小,拋光片的缺點也逐漸 暴露出來,比如硅片表面局部的晶格缺陷,硅片表面含氧量較高等。為了解決這些問題,退火晶圓技術被開發(fā)出來。在拋光后,將硅片放在充滿惰性氣體的爐管中(一般為氬氣),進行高溫退火。這樣既可以修復硅片表面晶格缺陷,同時也可以減少表面含氧量。

EW(Epitaxy Wafer):外延層硅片。隨著集成電路的應用場景不斷增加,由硅片廠制造的標準硅片在電學特性上已經(jīng)不能滿足某些產品的要求。同時,通過熱退火減少的晶格缺陷也不能滿足越來越小的線寬需求。這就衍生出了外延層硅片。通常的外延層就是硅薄膜。是在原始硅片的基礎上,利用薄膜沉積技術,生長一層硅薄膜。由于在硅外延中,硅基片是作為籽晶的模式存在,所以生長外延層會復制硅片的晶體結構。由于襯底硅片是單晶,所以外延層也是單晶。但是由于沒有被拋光,所以生長完成后的硅片表面的晶格缺陷可以被降到很低。

外延技術指標主要包括外延層厚度及其均勻性、電阻率均勻性、體金屬控制、顆粒控制、層錯、位錯等缺陷控制。現(xiàn)階段人們通過優(yōu)化外延的反應溫度、外延氣體的流速、中心及邊緣的溫度梯度,實現(xiàn)了很高的外延層硅片質量。因產品不同和技術升 級的需要,通過不斷優(yōu)化外延工藝,現(xiàn)在已經(jīng)實現(xiàn)了很高的外延硅片質量。

另外,現(xiàn)在技術已經(jīng)可以生成電阻率摻雜元素、摻雜濃度與原始硅片不同的外延層,這樣更容易控制生長出來的硅片的電學特性。比如可以通過在 P 型硅片上生成一層 N 型硅外延層,這樣就形成了一個低濃度參雜的 PN 結,為后續(xù)芯片制造中起到優(yōu)化擊穿電壓,降低閂鎖效應等等目的。外延層厚度一般根據(jù)使用場景不同而不同,一般邏輯芯片的厚度為 0.5 微米到 5微米左右,功率器件由于需要承受高電壓,所以厚度為 50 微米到 100 微米左右。

▲外延硅片生長過程

▲外延片的不同參雜

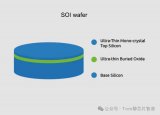

SW(SOI Wafer):SOI 全稱是 Silicon-On-Insulator(絕緣體上硅)。由于 SOI 硅片具有寄生電容小、短溝道效應小、繼承密度高、速度快、功耗低等優(yōu)點,特別是在襯底噪聲低這個優(yōu)點使得 SOI 硅片常常用在射頻前端芯片中。

▲普通硅片 MOS 結構

▲SOI 硅片 MOS 結構

制造 SOI 硅片的方法主要有四種:SIMOX 技術、Bonding 技術、Sim-bond 技術和 Smart-CutTM 技術;SOI 硅片的原理比較簡單,核心目標就是在襯底中間加入一層絕緣層(一般以二氧化硅 SiO2 為主)。

▲四種制造 SOI 硅片技術

從性能參數(shù)上來看,Smart-CutTM 技術是現(xiàn)在 SOI 硅片制造技術中性能最優(yōu)異的。Simbond 技術性能和 Smart-Cut 技術性能相差不大,但是在頂層硅厚度方面,Smart-Cut 技術生產的 SOI 硅片更薄,而且從生產成本來說,Smart-Cut 技術可以重復利用硅片,對于未來的大批量生產情況,Smart-Cut 技術更有成本優(yōu)勢,所以現(xiàn)在業(yè)界公認以 Smart-Cut 技術為未來 SOI 硅片發(fā)展方向。

▲SOI 硅片不同制造技術的性能對比

SIMOX 技術:SIMOX 全稱 Separation by Implanted Oxygen(注氧隔離技術)。向晶圓中注入氧原子,然后經(jīng)過高溫退火,使氧原子與周圍的硅原子發(fā)生反應,生成一層二氧化硅。此項技術的難點是控制氧離子注入的深度與厚度。對于離子注入技術要求較高。

Bonding 技術:Bonding 技術又稱鍵合技術,用 bonding 制造的 SOI 硅片又叫 Bonded SOI,簡稱 BSOI。Bonding技術需要兩片普通硅晶圓,在其中一片上生長一層氧化層(SiO2),然后與另外一片硅源鍵合,連接處就是氧化層。最后再進行研磨和拋光到想要的填埋層(SiO2)深度。由于鍵合技術比離子注入技術簡單,所以目前 SOI 硅片大都采用 bonding 技術制作。

▲離子注入方式形成絕緣體上硅

▲wafer bonding 方式形成絕緣體上硅

Sim-bond 技術:注氧鍵合技術。Sim-bond 技術是 SIMOX 與 bond 技術的結合。優(yōu)點是可以高精度控制埋氧層厚度。第一步是向一片硅晶圓注入氧離子,然后高溫熱退火形成氧化層,然后在該硅片表面形成一層 SiO2 氧化層。第二步是將該硅片與另外一片晶圓鍵合。然后進行高溫退火形成完好的鍵合界面。第三步,減薄工藝。利用 CMP 技術減薄,但是與 bond 技術不同的是,sim-bond 有自停止層,當研磨到 SiO2 層時,會自動停止。然后經(jīng)過腐蝕去掉 SiO2層。最后一步是拋光。

Smart-cut 技術:智能剝離技術。Smart-cut 技術是鍵合技術的一種延伸。第一步是將一片晶圓氧化,在晶圓表面生成固定厚度的 SiO2。第二步是利用離子注入技術,向晶圓的固定深度注入氫離子。第三步是將另外一片晶圓與氧化晶圓鍵合。第四步是利用低溫熱退火技術,氫離子形成氣泡,令一部分硅片剝離。然后利用高溫熱退火技術增加鍵合強度。第五步是將硅表面平坦化。這項技術是國際公認的 SOI 技術發(fā)展方向,埋氧層厚度完全由氫離子注入深度決定,更加準確。而且被剝離出的晶圓可以重復利用,大大降低了成本。

▲sim-bond 方式形成絕緣體上硅

▲Smart-cut 方式形成絕緣體上硅

責任編輯:pj

-

半導體

+關注

關注

334文章

27013瀏覽量

216287 -

光電效應

+關注

關注

0文章

91瀏覽量

13863 -

單晶硅

+關注

關注

7文章

190瀏覽量

28213

發(fā)布評論請先 登錄

相關推薦

2024年第二季全球半導體硅片出貨面積環(huán)比增長7.1%

掌握半導體大硅片生產技術,中欣晶圓科創(chuàng)板IPO終止

132億元!滬硅產業(yè)擴產300mm半導體硅片

硅片和soi這兩種材料,他們的不同之處是什么呢?

1GW產能所需的硅料、硅片及電池數(shù)量介紹

逆變器如何匹配182/210硅片尺寸的超高功率組件呢?

光伏發(fā)電原理及工作過程 光伏設備有哪些

使用ICP-MS/MS進行光伏硅片表面Ti納米顆粒表征的實驗過程

關于半導體硅片和光伏硅片的制造過程介紹

關于半導體硅片和光伏硅片的制造過程介紹

評論