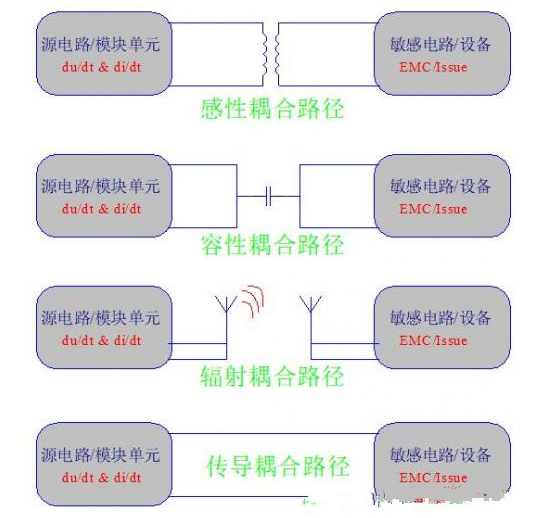

電磁干擾(EMI)是電磁能,它通過輻射或感應干擾電子設備中的信號。從收音機上的靜電到手機靠近音頻設備時聽到的嗡嗡聲,電磁干擾一直在我們身邊。

要產生EMI,您所需要的只是能量和天線。電子設備基本上是充滿電磁能的電路板。您所需要的只是跨能量源的偶極子,并且您的天線可以輻射EMI。此外,由于EMI輻射會影響我們周圍世界中的關鍵電子設備,例如飛機上的設備,因此在產品投放市場之前,您必須通過EMI / EMC法規和標準。讓我們深入探討可用于降低PCB設計中EMI的常用技術。

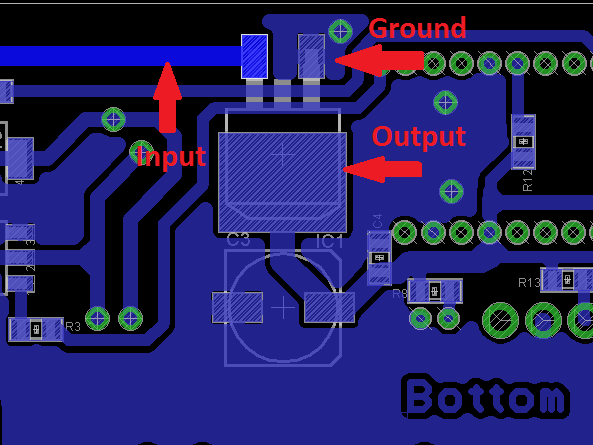

接地

在許多方面,接地層都是抵御EMI產生的那種噪聲的第一道防線,因為電路至少需要浮地才能工作。用教科書中的水類比法,如果電路中的電流像是一系列水管中的水,則接地層就像是一大盆水。當水倒入盆地時,會形成波紋。這些漣漪很容易被大盆地吸收,但是如果盆地較小,它們會停留更長的時間并在水池壁周圍反彈。

在PCB中,接地層在那里提供0伏參考線到電源接地端子,用于電路的返回路徑。但是,與盆地不同,制造“波紋”時會產生噪聲,偶極子會形成,整個電路板會變成天線。這就是為什么接地層(PCB中的銅箔層)要占據電路板盡可能多的橫截面的原因。要降低整個板上的EMI,就要從有效利用接地層開始。減少地面電磁干擾的一些常見最佳做法包括:

l使用多層板。地平面太小?添加另一層可以為您提供更多關于如何處理板上高速走線的選擇。差分對產生串擾?將它們放在降低噪音的內層中。

l小心使用分開的接地層。如果要分開接地層,請確保有充分的理由,例如分開模擬和數字接地以避免噪聲耦合,因為分開的接地層可以充當縫隙天線并輻射。

l僅在單個點連接分離的接地平面。您擁有的公共接地連接越多,創建的環路就越多,您的設計將輻射出更多的EMI。

l將旁路或去耦電容器連接至接地層。如果您的設計中有這些,則可以通過將它們接地來減少返回電流路徑,從而減小環路的尺寸,從而減小輻射。只是要確保不要在電源層和無關的接地層之間連接旁路電容器,否則會引起電容性耦合。

走線布局

跡線是電路板上的導電路徑,在電路處于活動狀態時會包含流動的電子,這意味著它們只是彎曲或與創建全輻射天線交叉。

跟蹤布局的常見最佳做法包括:

l避免銳角直角彎曲。電容在45°角區域增加,從而改變了特性阻抗并導致反射。圓角直角可以緩解這種情況。

l將信號分開。將高速走線(例如時鐘信號)與低速信號分開,模擬信號與數字信號分開。

l使返回路徑短。

l差分走線的走線應盡可能靠近。這增加了耦合系數,使受影響的噪聲進入共模,這對于差分輸入級來說問題較少。

l明智地使用過孔。通孔是必需的,因為它們使您可以在布線時利用電路板上的多層。設計人員必須意識到,他們在混頻中增加了自己的電感和電容效應,并且由于特性阻抗的變化會產生反射。

l避免在差分走線中使用過孔。如有必要,請使用兩個通孔共享的橢圓形抗焊盤,以減少寄生電容。

組件安排

電子元器件是電子電路的基礎。注意每個組件的EMI影響可導致更好的PCB設計。組件布局的最佳做法包括:

l將模擬電路與數字電路分開。與走線一樣,AC和DC電路應分開放置,以避免串擾和其他問題。屏蔽,利用多層優勢以及使用單獨的接地都是可行的選擇。

l隔離高速組件。組件越快越小,EMI越大。通過屏蔽和濾波來緩解CPU和GPU中高頻時鐘的自然EMI效應。

EMI屏蔽

某些組件將不可避免地產生EMI,這是可以的。我們可以用法拉第籠將它們屏蔽,這是一種由導電材料制成的外殼,其厚度足以阻擋RF波。盡管理想的法拉第籠應該是沒有開口的導電外殼,但實際上我們使用的是由金屬或導電泡沫制成的盒子(稱為墊圈)。

降低下一個PCB設計中的EMI

在板上布置走線和過孔的方式中意外地創建天線太容易了。再加上對更高時鐘速度的不斷增長的需求,您開始意識到為什么降低EMI比以往任何時候都更為重要。準備好將這些EMI降低技巧中的一些技巧融入您的下一個設計中了嗎?

-

電路板設計

+關注

關注

1文章

127瀏覽量

16479 -

PCB設計

+關注

關注

394文章

4671瀏覽量

85319 -

PCB布線

+關注

關注

20文章

463瀏覽量

42031 -

華秋DFM

+關注

關注

20文章

3493瀏覽量

4385

發布評論請先 登錄

相關推薦

PCB設計中怎么降低EMC

pcb設計中如何設置坐標原點

PCB設計與PCB制板的緊密關系

儲能PCB設計與制造思考 探討儲能PCB設計與制造中的關鍵要素

這幾招教你解決PCB設計中的電磁干擾(EMI)問題

多層pcb設計如何過孔的原理

使用PCB孔來減少EMI的教程

EMC之PCB設計技巧

PCB設計中EMI傳導干擾該如何處理?

降低PCB設計中EMI的技術

降低PCB設計中EMI的技術

評論