本地振蕩器(LO)是現(xiàn)代通信、汽車、工業(yè)和儀器儀表應用中的關鍵組件。無論從基帶到RF實施上變頻還是反過來的下變頻,為汽車雷達、材料檢測應用生成掃頻,或者為上述應用電路的構建和測試而開發(fā)儀器儀表,我們生活的很多方面都存在LO。電路和工藝技術的進步已幫助降低了此類電路的成本、復雜性和面積;與過去需要更廣泛地混合使用有源和無源技術相比,現(xiàn)代集成電路大大降低了LO的設計難度。

過去,適用于GSM等2G通信應用的大部分LO都使用與ADI公司的ADF4106類似的整數(shù)N分頻PLL,以及窄帶T封裝VCO(例如VCO190-1846T)。在大多數(shù)情況下,這些VCO的高品質因素(Q)使其非常易于滿足該嚴苛標準下的相位噪聲規(guī)格。那時的手機一般只支持一種無線標準,標準本身的數(shù)據(jù)速率也有限(雖然2G網(wǎng)絡出色的覆蓋率幫助手機獲得了廣泛的市場認可)。基站LO一般是使用多種IC和VCO子模塊組合而成的模塊,如圖1所示。

對無線數(shù)據(jù)速率以及與不同的全球無線標準兼容性的需求不斷提高,促進了寬帶VCO的發(fā)展,與窄帶VCO相比,寬帶VCO有助于實現(xiàn)更寬的頻率覆蓋范圍,支持更多的新可用頻譜。支持這種數(shù)據(jù)吞吐量的微波回程網(wǎng)絡也承受著壓力,需要支持高階調制率,可針對不同范圍和標準進行配置,同時幫助網(wǎng)絡提供商降低工程難度,提高投資回報率。為了支持這些網(wǎng)絡開發(fā),典型的信號分析儀使用了龐大笨重的釔鐵石榴石(YIG)振蕩器,以及使用類似技術的笨重濾波器。

VOC改進

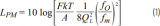

開發(fā)集成硅芯片微波VCO面臨的最大技術挑戰(zhàn)是可用晶圓制造工藝中的Q值有限。在許多情況下,繞線電感(用于T封裝VCO中)的Q值可能從數(shù)百的典型值降至剛剛超過10,因Leeson方程的限制,Q值會嚴重影響相位噪聲,根據(jù)此方程,相位噪聲LPM(公式1)與VCO Q值成平方反比,和輸出頻率成平方正比關系。

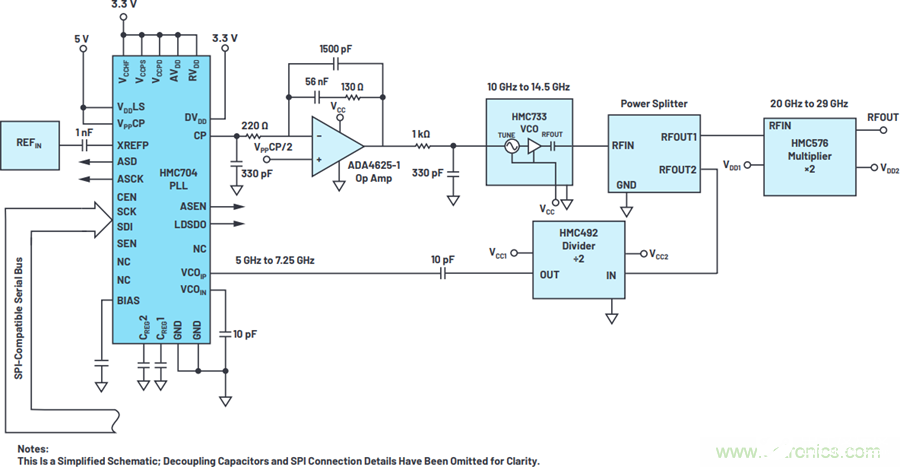

基于砷化鎵(GaAs)或鍺硅(SiGe)制造的寬帶單核VCO通過將VCO的調諧端口范圍從5V(大部分硅基PLL電荷泵可用的典型電壓)擴展至15V、甚至30V來解決范圍與噪聲的問題。這意味著,諧振器Q可以保持不變,但擴展的變?nèi)?a target="_blank">二極管可調諧性可以提供更廣泛的調諧范圍,但不會惡化相位噪聲。這種更高調諧范圍帶來的挑戰(zhàn),可以通過使用有源低通濾波器以將電荷泵電壓(典型值為5V)轉換為15 V或30 V來解決(參見圖2中HMC733的調諧范圍)。這些有源濾波器需要使用高壓低噪聲運算放大器。所以,典型的微波LO將由PLL(如ADF4106),運算放大器以及GaAsVCO組成,在很多情況下,還需要一個外部分頻器,將VCO信號分頻至PLL允許的最大輸入頻率(對于ADF4106,為6 GHz)。GaAs VCO一般在S頻段和更高頻段下運行,因為諧振器電路一般在2GHz以上提供最佳性能。設計電路板時更要格外小心,這需要熟知電源、模擬以及RF和微波領域專業(yè)知識。PLL濾波器的設計及其性能仿真都需要具備豐富的控制理論和噪聲建模經(jīng)驗,并且需要熟悉每個組件。完成這些任務所需的經(jīng)驗并不容易獲得,一般只有從事硬件設計工作幾十年的資深人士才具備。

圖2. HMC733調諧范圍。

目前有多種技術可以解決低Q值問題。在類似ADF4360的產(chǎn)品系列中,裸片(粘接到焊盤上)表面焊線的Q值大約為30。厚金屬電感也可以改善Q值,改進變?nèi)荻O管Q也有助于大幅提高諧振器Q值,從而進一步改善相位噪聲性能。適合制造高頻率VCO和N分頻器電路的BiCMOS工藝,以及用于開關各種電容的CMOS邏輯電路,這些意味著寬帶PLL和VCO IC切實可行,其小巧的尺寸和更寬的頻率范圍則使其迅速得到無線市場的認可。

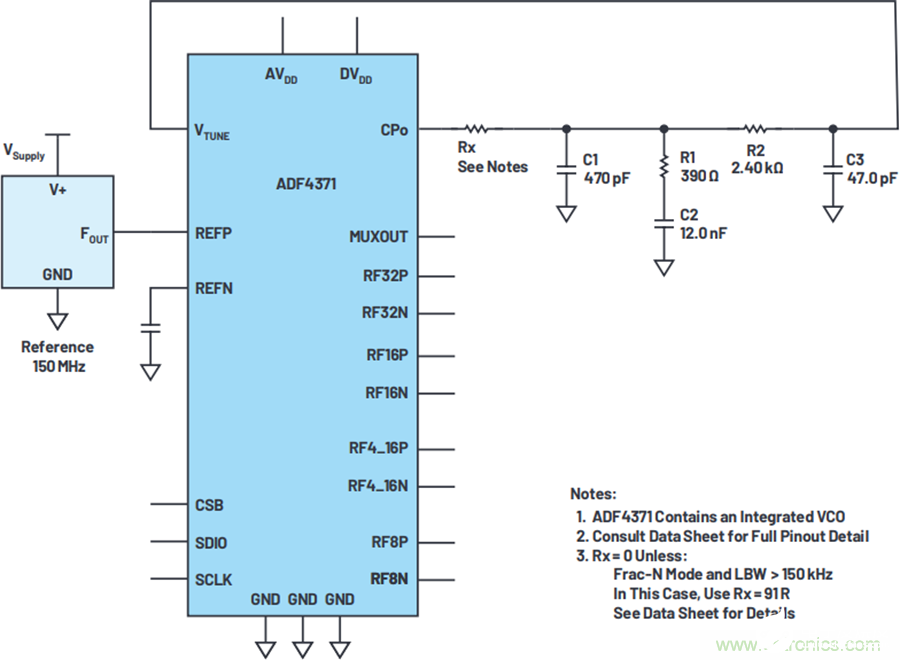

許多寬帶LO都采用了這種方法。覆蓋整個倍頻范圍的VCO很有優(yōu)勢,這是因為一組分頻器可生成的頻率范圍只受最低可用VCO頻率和最高可用分頻比限制。采用硅芯片工藝的VCO設計取得了重 大突破,通過開關不同的電容組,可以將VCO范圍劃分為多個子頻段。這支持實現(xiàn)更廣泛的頻率覆蓋范圍,無需通過降低振蕩器諧振器Q值來犧牲相位噪聲,同時支持使用電壓較低的電荷泵,所以無需使用額外的運算放大器,其需要更高的電源電壓軌。進一步改善可將VCO頻段的數(shù)量從數(shù)十個增加到數(shù)百個,甚至在單片IC上開發(fā)其他單獨的重疊VCO內(nèi)核(按需進行開關),從而進一步優(yōu)化相位噪聲,例如ADF4371(圖3)。從圖2中HMC733的單核VCO與圖3的ADF4371的多頻段VCO之間,可以看出明顯的不同。

圖3. ADF4371頻率與VTUNE的關系。

從圖2的頻率與VTUNE關系圖中可以看出,HMC733調諧電壓與輸出頻率成正比,而在圖3中,調諧電壓基本上在VTUNE的1.65V目標值的幾百毫瓦以內(nèi)。智能頻段選擇邏輯或自動校準電路意味著用戶無需針對頻率開發(fā)頻段查找表,且存在足夠裕量,可以保證在電源電壓范圍,尤其是溫度電壓范圍內(nèi)可靠運行。

PLL改進

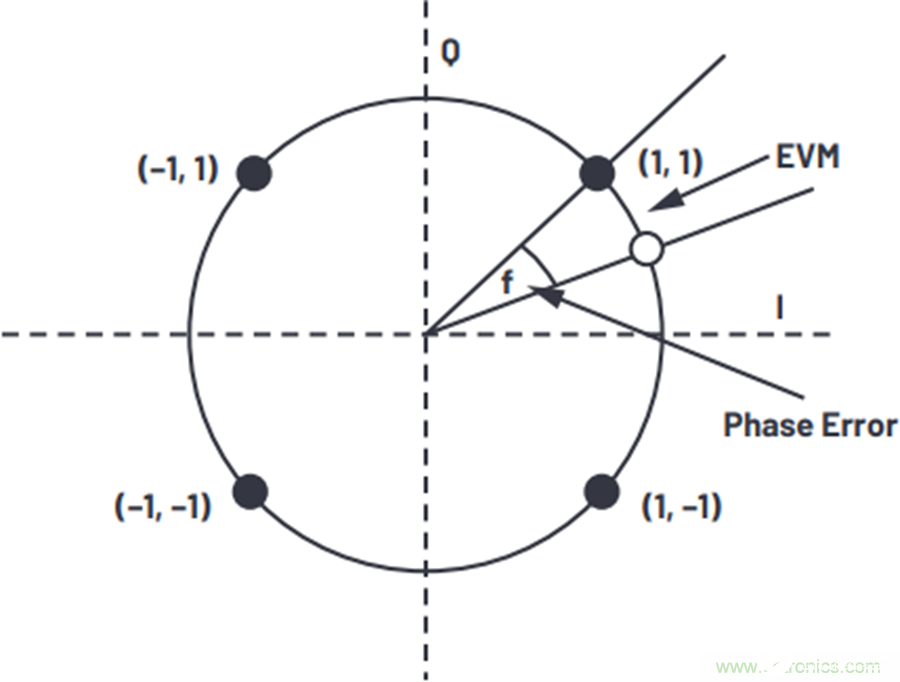

實現(xiàn)更高的數(shù)據(jù)速率需要具有更低的向量誤差調制(EVM)速率(圖4),這主要取決于窄帶無線應用中PLL頻率合成器的帶內(nèi)相位噪聲貢獻;使用200kHz信道柵提供1.8GHz輸出需要很高的N(9000),因而N分頻器的20log(N)貢獻會在頻段內(nèi)產(chǎn)生嚴重影響。高階調制速率(例如64QAM)需要更低的EVM,這會推動開發(fā)、采用和部署小數(shù)N分頻頻率合成器,比如ADF4153A和ADF4193,這會使信道柵與PFD頻率無關,從而大幅降低帶內(nèi)噪聲。將ADF4106和ADF4153A進行比較(比較圖5和圖6),可以明顯看出這一優(yōu)勢,在1kHz頻偏下,帶內(nèi)噪聲從–90dBc/Hz降至–105dBc/Hz。我們使用ADIsimPLL?來計算,它可以對ADI公司的所有PLL產(chǎn)品進行了仿真。

圖4. 相位誤差QPSK。

圖5. 帶VCO-1901846T的整數(shù)N分頻ADF4106。

圖6. 帶VCO-1901846T的小數(shù)N分頻ADF4153A。

小數(shù)N分頻還具有額外的優(yōu)勢,由于PFD頻率更高,支持的環(huán)路帶寬更寬,因此鎖定時間更短。利用多個電荷泵失調電流和∑-?擾動功能,可將小數(shù)N雜散降低到可接受的水平。ADF4193和 ADF4153A分別支持26MHz和32MHz PFD頻率,更高的PFD頻率也允許用戶進一步降低N,由于整數(shù)邊界雜散(IBS)的發(fā)生率和影響較小,因此可進一步改善EVM并簡化頻率規(guī)劃。ADF4371采用的最新PLL拓撲支持高達160MHz的PFD頻率。小數(shù)N分頻器件頻率分辨率的改善(小數(shù)調制器從12位分辨率增加到39位分辨率)也意味著PLL可用于生成幾乎所有分辨率達到毫赫(MHz),且精度極高的頻率。

圖7. ADF4371。

過去,使用小數(shù)N分頻器件遇到的主要阻礙在于存在很高的小數(shù)雜散,這些雜散由∑-?調制器生成,會降低頻譜純度,因此需要工程師付出更多努力,以減少或消除其影響。由于ADF4371具有較低的小數(shù)雜散,并且沒有整數(shù)邊界,所以干凈頻譜意味著可以花費更少時間來研究、調試,或者從一定程度上消除了這些煩人的頻率生成偽影帶來的影響。較低的帶內(nèi)整數(shù)邊界雜散(–55dBc)意味著一旦經(jīng)PLL濾波器濾波,雜散就可以得到有效衰減。例如,如果將40kHz濾波器用于400 kHz信道柵,那么濾波器提供35dB衰減意味著距離整數(shù)邊界最近信道的雜散為–90dBc。能夠使用高達160MHz的高PFD頻率意味著整數(shù)邊界出現(xiàn)的幾率更低,相比使用32MHz PFD頻率,使用160MHz PFD頻率時,其幾率低5倍。

由于PFD頻率和頻率分辨率的提高,PLL品質因數(shù)(FOM)也有顯著提升,例如從ADF4153的–216dBc/Hz提高到ADF4371的–233dBc/Hz(小數(shù)模式)。將圖5和圖7中的ADIsimPLL曲線進行比較,ADF4106在整數(shù)模式下,采用200kHz PFD頻率設置,10kHz環(huán)路帶寬,生成1.85GHz輸出,而ADF4371則采用160MHz PFD頻率設置,150kHz環(huán)路帶寬。可以看出,在1kHz頻偏時存在20dB的差異,PLL頻率合成器技術取得明顯進步。

同時可以看出,存在著1ps和51fs的集成rms相位抖動的差異。值得注意的是,與過去由電感Q決定rms噪聲性能相比,帶內(nèi)噪聲的大幅改善(通過低FOM和小數(shù)N分頻實現(xiàn))允許用戶將環(huán)路濾波器帶寬增加至150kHz,從而抑制此帶寬內(nèi)的VCO噪聲,并降低10kHz至100kHz范圍內(nèi)的惡化,后者一般決定rms噪聲。為實現(xiàn)這一帶內(nèi)相位噪聲的改善目標,采用更高規(guī)格的PLL頻率參考源至關重要,通過改進此類方法的性能和靈活性,大多數(shù)用戶都能接受這種權衡考量方案。在某些情況下,新型小數(shù)N分頻PLL提供的更低帶內(nèi)噪聲可以和使用偏移或轉換環(huán)路的PLL的結果相匹敵,后者在VCO至PFD的反饋路徑中使用了混頻器,可大大簡化要求嚴苛應用的頻率生成。

ADF4371VCO的基波頻率范圍為4GHz至8GHz,這是考慮了制造設備所使用的SiGe工藝的VCO相位噪聲性能的最佳點。為了生成更高頻率,我們使用了倍頻器。通過重新設計VCO來實現(xiàn)雙倍頻率范圍存在一定問題,因為噪聲的降低幅度高于通過擴展VCO的頻率范圍所預期的6dB。所以,采用了倍頻器,它將VCO范圍從8GHz擴展到16GHz,還采用了四倍頻器,將4GHz至8GHz的VCO范圍擴展到16GHz至32GHz。在每種情況下,倍頻器都會帶來一些頻率噪聲,包括VCO饋通,以及2×、3×和5×VCO頻率。為了降低濾波要求,每個倍頻器電路都包含跟蹤濾波器,以調諧輸出,最大限度提高了所需頻率與頻率噪聲的功效比。雙倍輸出的次諧波抑制一般低至45dB,四部輸出則低至35dB。

寬帶工作

從之前所示的窄帶示例中,可以看出新型PLL/VCO技術優(yōu)勢明顯,但與使用HMC733VCO的HMC704PLL生成寬帶頻率相比,使用ADF4371還可以更進一步改善。用戶使用分立式解決方案時面臨諸多挑戰(zhàn),其目標是生成20GHz至29GHz的干凈可變LO。

首先,HMC733VCO的輸出功率必須在板上分配,并分頻至適合HMC704的頻率,所以必須使用外部分頻器(如(HMC492),將10GHz至14.5GHz范圍分頻至HMC704允許的5GHz至7.25GHz。

然后,必須使用倍頻器(如HMC576)將10GHz至15GHz頻率范圍倍增至20GHz至30GHz。

需要使用有源低通濾波器來生成HMC733所需的調諧電壓。本示例使用ADA4625-1。這也要求運算放大器的電源電壓高到足以生成所需的調諧調壓(在本例中,為15 V)。

調諧靈敏度的變化必須在整個VCO頻率范圍內(nèi)進行補償。這通常通過調節(jié)電荷泵電流,以保持電荷泵增益和VCO增益的乘積來實現(xiàn)。

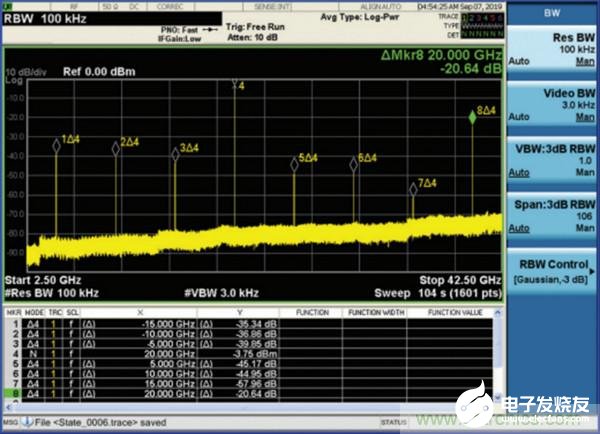

HMC576倍頻器之后的VCO饋通約為–20dBc。ADF4371的調諧濾波器會將倍頻器產(chǎn)生的不必要的頻率抑制在35 dBc。這大大簡化了后續(xù)濾波。

圖8. 分立式PLL/VCO倍頻器解決方案。

相比之下,ADF4371 PLL/VCO開箱即用,只需使用一個高品質的外部參考頻率源,即可生成此頻率。可以復制 EV-ADF4371SD2Z的布局,同時復制相應的電源管理解決方案。環(huán)路濾波器的設計也會明顯簡化,因為不需要最終用戶補償靈敏度(kV)的變化,也無需使用有源濾波器元件。用戶無需花費數(shù)周時間來選擇器件,也無需花費大量時間來為每個分立式組件構建仿真模型,他們可以直接使用ADIsimPLL來設計和仿真預期的性能,并通過ADF4371評估板來評估獲取準確的預期結果,因為評估結果與仿真性能非常接近。更少的組件數(shù)量和更高的集成水平能夠大幅改善系統(tǒng)的尺寸和重量,此外,也會大幅改善系統(tǒng)性能,計算得出的ADF4371集成rms抖動為60fs,而分立式解決方案的抖動為160fs。從圖9可以看出,組件數(shù)量和電路板面積均明顯節(jié)省,如果不包括必要的退耦電容和其他所需的無源器件,有源器件和功率分路器的總面積相當于96mm2,而ADF4371僅49mm2。用戶也可以根據(jù)需要為VCO選擇3.3V電源,以節(jié)省功率。

圖9. ADF4371框圖。

在基波VCO模式下,ADF4371的頻譜純度達到最高,無用雜散(非帶內(nèi))僅限于VCO諧波。對于許多轉換器時鐘應用,方波本身的特性不會造成問題,可能確實合乎需要,但對于儀器儀表應用來說,寬帶雜散頻率一般必須低于50dBc。可調諧波濾波器可幫助消除這些諧波,專門設計的ADMV8416/ADMV8432非常適合對ADF4371的輸出進行濾波。

ADMV8432是一款可調諧帶通濾波器,指定中心工作頻率范圍為16GHz至32Ghz,典型 3dB帶寬為18%,典型插入損耗為9dB,寬帶抑制大于30dB,專為配合ADF4371四倍頻器輸出使用而設計。ADMV8416也是一款可調諧帶通濾波器,工作頻率范圍為7GHz至16GHz,典型 3dB帶寬為16%,典型插入損耗為8dB,寬帶抑制大于30dB,可配合ADF4371倍頻器輸出使用。

圖10. ADF4371 20 GHz輸出。

圖11. 使用ADMV8432濾波器的ADF4371 20 GHz輸出。

ADMV8416/ADMV8432均采用雙重疊頻段結構,帶內(nèi)部RF開關,可以實現(xiàn)更寬的頻率覆蓋范圍,同時保持出色的抑制性能。頻段選擇通過對所需的電平轉換器實施數(shù)字邏輯控制來實現(xiàn)。電平轉 換器確保內(nèi)部RF開關會進行相應的偏置,以獲得高于+34dBm的最佳輸入三階交調截點(IIP3)。

在每個工作頻段內(nèi),可調諧濾波器通過0V至15V的模擬控制電壓進行控制,消耗的電流不到1μA。這種控制電壓一般通過DAC和運算放大器驅動電路生成。例如AD5760DAC后接ADA4898運算放大器,可以為濾波器提供相對較快的調諧速度和低噪聲驅動電壓。如果調諧速度不太重要,則可以將DAC直接驅動至濾波器的調諧端口。

考慮到這些模擬調諧濾波器的性能指標,可以在犧牲少量輸出功率的情況下,去除ADF4371頻率合成器倍頻器和四倍頻器輸出中的無用諧波成分。雖然為了解決插入損耗問題,可能需要額 外的放大級,但濾波器一般比分立式開關組解決方案要小,尤其在需要寬帶可調諧性的情況下。此外,頻率合成器的雜散電平在濾波前一般為–35dBc,濾波后可以達到–55dBc。未濾波且 未使用的輸出的耦合可能會影響?zhàn)佂ǎ瑯嫿P蜁r應該非常小心,以實現(xiàn)濾波器IC的全阻帶抑制。

結論

隨著相關工藝、電路和封裝技術的各種創(chuàng)新,頻率生成技術不斷發(fā)展,能夠為用戶提供比以前的分立式解決方案的體積更小、功能和性能更出色的解決方案。寬帶頻率工作趨勢推動了新款IC的開發(fā),即覆蓋多個倍頻率,頻率范圍高達32GHz。寬帶PLL/VCO提供了很高的靈活性和簡潔性,可以幫助最終用戶大幅縮短設計時間和加快上市時間。

對頻譜純度的需求推動濾波IC不斷創(chuàng)新,這些IC與新開發(fā)的頻率合成器IC配合使用,可以提供現(xiàn)代無線應用所需的低相位噪聲和高頻譜純度毫米波信號源。用戶可以使用免費的仿真工具ADIsimPLL來評估和比較PLL性能,還可以使用簡單易用、具有直觀界面的快速行為模型幫助進行組件選型。這款工具為設計工程師節(jié)省了大量時間,使他們無需構建大量不同領域的數(shù)學模型來預測性能。

-

PLL技術

+關注

關注

0文章

10瀏覽量

3668

發(fā)布評論請先 登錄

相關推薦

ADMV8416/ADMV8432與PLL/VCO IC配合實現(xiàn)PLL/VCO技術的提升

用于無線應用的集成PLL和VCO

VCO底部,??中間或頂部是最佳PLL性能嗎?

基于高壓VCO的高性能PLL設計

集成VCO的PLL產(chǎn)品功能如何?

基于TPM的系統(tǒng)綜合技術性能評估方法研究

高性能RF PLL和PLL VCO技術的介紹

CN0232 將集成VCO和外部PLL電路的頻率合成器雜散輸出降至最低

提升PLL/VCO技術性能的方法

提升PLL/VCO技術性能的方法

評論