1 概述

TSA5059是專門為數字衛星接收機的調諧系統設計的單片PLL頻率合成器,它的工作頻率可達2.7GHz,供電電壓為5V±10%,電源電流為45mA。輸入信號幅度(RMS)在頻率為64-150MHz、150MHz-2.2GHz、2.2-2.7GHz時分別為12.6-300mV、7.1-300mv和22.4-300mV。該器件的晶振頻率為4-16MHz,工作溫度范圍為-20-+85℃,采用SO16及SSO16兩種封裝形式。其引腳排列如圖1所示。各引腳的功能說明如下:

1腳(CP):電荷泵輸出端,該腳可編程為四種電流值輸出方式。

2腳(XTAL):參考晶振或其它振蕩器輸入。

3腳(XT/COMP):參考頻率輸出端,該腳在軟件控制下,既可輸出由晶體產生的振蕩信號或其它振蕩器信號,也可輸出上述信號的4分頻信號。

4腳(AS):I2c總線地址選擇輸入,高電平有效。

5腳(SDA)、6腳(SCL):分別為I2c總線的數據線和時鐘線。

7-10腳(P3-P0):集電極開路式I/O口,在I2c總線控制下可讀入外部數據或向外輸出數據。

11腳(ADC):內部3位A/D轉換器模擬信號輸入端,該轉換器與其它部分相對獨立,通過I2c總線可讀取轉換結果。

12腳(Vcc):電源端。

13腳(RFA)、14腳(RFB):通常與壓控振蕩器(VCO)的輸出端相連。

15腳(GND):接地端。

16腳(VT):調諧電壓輸出端,一般作為壓控振蕩器的控制電壓。

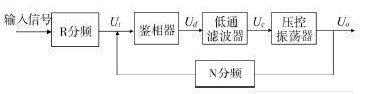

2 工作原理

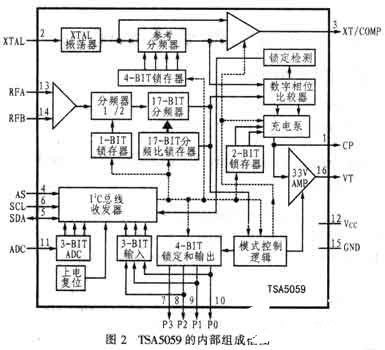

圖2所示是TSA5059的內部組成框圖。圖中,來自于2腳的晶振或其它振蕩器信號經TSA5059內部振蕩器后產生相應的頻率信號,該頻率信號再經參考分頻器分頻即可產生參考頻率FR。13腳、14腳的輸入信號一般為壓控振蕩器(VCO)的輸出信號,該信號在TSA5059內部經放大器進行呻鬲度放大后再經預定標器(由軟件可控為分頻值為1或2的分頻器)和17位分頻器后可產生比較信號頻率Fc,把這兩個信號送人數字相位比較器進行相位此較以產生相位差信號,然后將該相位差信號再經電荷泵電路處理來產生相對應的電流,該電流一路由1腳輸出,另一路經33V放大器(33V AMP)后由16腳輸出以控制壓控振蕩器的輸出頻率F。,從而使Fc值鎖定在FR值上。這樣,由于這兩者僅有相位之差而無頻率值之差,而且F。與Fc之間有固定的分頻值,故F。是穩定的,這就是TSA5059鎖相環的基本工作原理。

3 對TSA5059的控制:

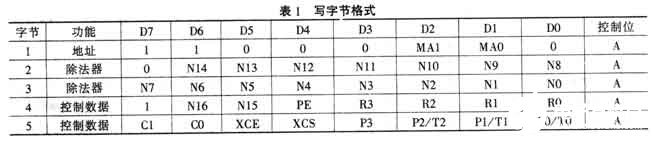

對TSA5059的控制可通過I2c總線來實現。在向TSA5059寫入控制數據時,可按表1所列順序進行。其中第一個字節為地址字節,且在寫入時,D7位必須為0。表1中主要字節的每位含義如下:

MAl、MA0:可編程地址位,如果一塊電路板上有多個TSA5059(最多四個)由一個控制器控制,為了分別控制每一個TSA5059,其MAI、MA0應按表2所列編碼并向4腳提供電壓。

A:回答位。

N16-NO:17位分頻器分頻比N控制位,即:

N=N16 X 216+N15 X 215+.。.+ N1 X 21+NO

PE:預定標器控制位,PE=1時,預定標器分頻比為2,反之為1。

R3-BO:參考分頻器分頻比控制位,見表3所列。

C1、CO:電荷泵電流選擇位,當ClC0為00時,其電荷泵電流IcP典型值為135μA,為01時,IcP為280μA,為10時,IcP為600μA,為11時,IcP為1230μA。

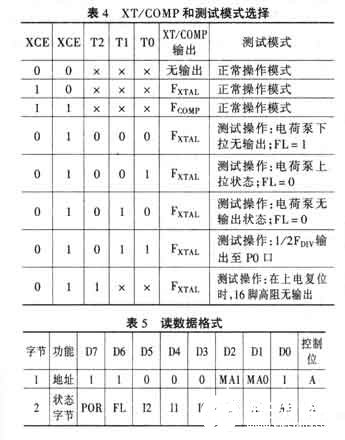

XCE:XT/COMP輸出允許位,該位為1時,輸出被激活。

XCS:XT/COMP選擇位,該位為1時,為信號輸出模式,為0時為測試模式。

T2-T0:XCE=0且XCS=1時的測試模式。

P3-P1:P3-P1口輸出狀態。

P0:P0口輸出狀態,但測試模式除外。表4給出了TSA5059中XT/COMP和測試模式的具體選擇說明。實際上,也可以在第一個字節后按以下幾種順序進行寫操作:

(1)字節4、5、2和3;

(2)字節2、3、4和停止信號;

(3)字節4、5、2和停止信號;

(4)字節2、3和停止信號;

(5)字節2和停止信號;

(6)字節4和停止信號。

對TSA5059進行讀操作可按表5的順序進行。在讀操作時,地址字節的D7位必須為1。當TSA5059的地址被確認后,TSA5059將產生應答脈沖以使第一個數據字節(狀態字節)被傳送在SDA線上,當第一個數據字節被讀出后,假若控制器在SDA線上產生了一個應答脈沖,第二個數據字節即可被讀出。而如果控制器在SDA線上產生了一個非應答脈沖,那么,數據傳送將結束,此時TSA5059將釋放SDA 線并使控制器產生停止狀態。當把P0至P2口當作輸入口時,它們必須被編程為高阻狀態。

表5中各狀態字節的每位含義如下:

當上電或Vcc低于2.75V時,POR標志位為1;在對TSA5059進行讀操作時,如果TSA5059檢測到讀時序結束,那么,POR標志位為0。當環路相位被鎖定時,FL=1。12、11、10位分別代表I/O口的狀態。

A2、A1、A0的編碼值代表了11腳的5個不同電壓等級,當A2AlA0為100時, 11腳電壓值為0.6Vcc-Vcc,011時為0.45Vcc-0.6Vcc,010時為0.3Vcc-0.45Vcc,001時為0.15Vcc-0.3Vcc,000時為0.-0.15Vcc。若把AFC電壓接至11腳,即可通過I2c總線讀出其數值的大小范圍,其讀出精度為±0.03 Vcc。

參考頻率FR的獲取是通過向表1中的第4個字節中的R3-R0寫入不同的編碼值來實現的,在4MHz晶振時,R3-R0在不同值時的FR值可參見表3。應當說明的是:TSA5059的3腳既可輸出2腳所接的晶振頻率,也可輸出經參考分頻器分頻后的FR。

4 典型應用

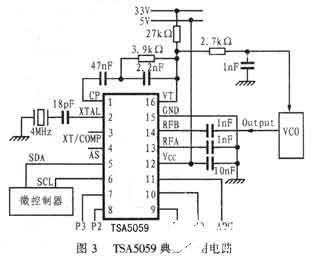

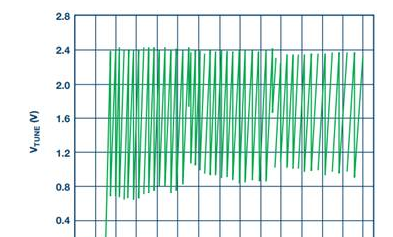

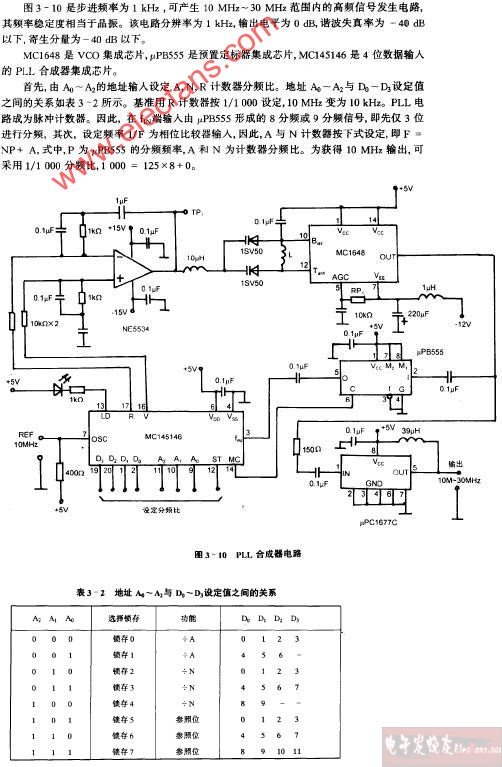

TSA5059的典型應用電路如圖3所示,其中33V電壓作為33V放大器的電源。1腳與16腳之間所接的元件組成環路濾波器,具體元件數值應視VCO的中心頻率而定。16腳的輸出電壓經RC低通濾波器濾波后可用于控制壓控振蕩器(VCO),而VCO的輸出電壓則送至14腳并經分頻后與參考頻率相比較以產生相位差信號,該相位差信號再經33V放大器放大以控制振蕩頻率。本電路采用的是負反饋,其最終VCO的輸出頻率將被鎖定在預定的數值上。

另外,利用TSA5059及SLl925(衛星零IF QPSK調諧電路)、STV0299(內含QPSK、BPSK解調電路及誤碼校正電路)還可組成高性能數字衛星接收機的下變頻器。

責任編輯:gt

-

接收機

+關注

關注

8文章

1180瀏覽量

53408 -

衛星

+關注

關注

18文章

1702瀏覽量

66907 -

pll

+關注

關注

6文章

775瀏覽量

135052

發布評論請先 登錄

相關推薦

詳解頻率合成器高性能架構的實現

如何利用FPGA設計PLL頻率合成器?

DDS PLL短波頻率合成器設計

基于FPGA與PLL頻率合成技術設計的整數/半整數頻率合成器

單片PLL頻率合成器TSA5059的特點性能及典型應用電路

單片PLL頻率合成器TSA5059的特點性能及典型應用電路

評論