在現實生活中,要想消除應用中的所有電源噪聲是不可能的。任何系統都不可能完全不受電源噪聲的影響。因此,作為 ADC 的用戶,設計人員必須在電源設計和布局布線階段就做好積極應對。在設計人員面臨眾多電源選擇的情況下,為高速 ADC 設計清潔電源時可能會面臨巨大挑戰。在利用高效開關電源而非傳統 LDO 的場合,這尤其重要。此外,多數 ADC 并未給出高頻電源抑制規格,這是選擇正確電源的一個關鍵因素。

本技術文章將描述用于測量轉換器 AC 電源抑制性能的技術,由此為轉換器電源噪聲靈敏度確立一個基準。我們將對一個實際電源進行的簡單噪聲分析,展示如何把這些數值應用于設計當中,以驗證電源是否能滿足所選轉換器的要求。總之,本文將描述一些簡單的指導方針,以便帶給用戶一些指導,幫助其為高速轉換器設計電源。

當今許多應用都要求高速采樣模數轉換器(ADC)具有 12 位或以上的分辨率,以便用戶能夠進行更精確的系統測量。然而,更高分辨率也意味著系統對噪聲更加敏感。系統分辨率每提高一位,例如從 12 位提高到 13 位,系統對噪聲的敏感度就會提高一倍。因此,對于 ADC 設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC 屬于 敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現最佳性能。噪聲來源眾多,形式多樣,噪聲輻射會影響性能。

當今電子業界的時髦概念是新設計在降低成本的同時還要“綠色環保”。具體到便攜式應用,它要求降低功耗、簡化熱管理、最大化電源效率并延長電池使用時間。然而,大多數 ADC 的數據手冊建議使用線性電源,因為其噪聲低于開關電源。這在某些情況下可能確實如此,但新的技術發展證明,開關電源可以也用于通信和醫療應用(見參考文獻 部分的“How to Test Power Supply Rejection Ratio (PSRR) in an ADC”(如何測試 ADC 中的電源抑制比(PSRR)))。

本文介紹對于了解高速 ADC 電源設計至關重要的各種測試測量方法。為了確定轉換器對供電軌噪聲影響的敏感度,以及確定供電軌必須處于何種噪聲水平才能使 ADC 實現預期性能,有兩種測試十分有用:一般稱為電源抑制比(PSRR)和電源調制比(PSMR)。

模擬電源引腳詳解

一般不認為電源引腳是輸入,但實際上它確實是輸入。它對噪聲和失真的敏感度可以像時鐘和模擬輸入引腳一樣敏感。即使進入電源引腳的信號實際上是直流,而且一般不會出現重復性波動,但直流偏置上仍然存在有定量的噪聲和失真。導致這種噪聲的原因可能是內部因素,也可能是外部因素,結果會影響轉換器的性能。

想想經典的應用案例,其中,轉換器采樣時鐘信號中有噪聲或抖動。采樣時鐘上的抖動可能表現為近載波噪聲,并且 / 或者還可能表現為寬帶噪聲。這兩種噪聲都取決于所使用的振蕩器和系統時鐘電路。即使把理想的模擬輸入信號提供給理想的 ADC,時鐘雜質也會在輸出頻譜上有所表現,如圖 2 所示。

圖 2. 采樣時鐘噪聲對理想數字化正弦波的影響

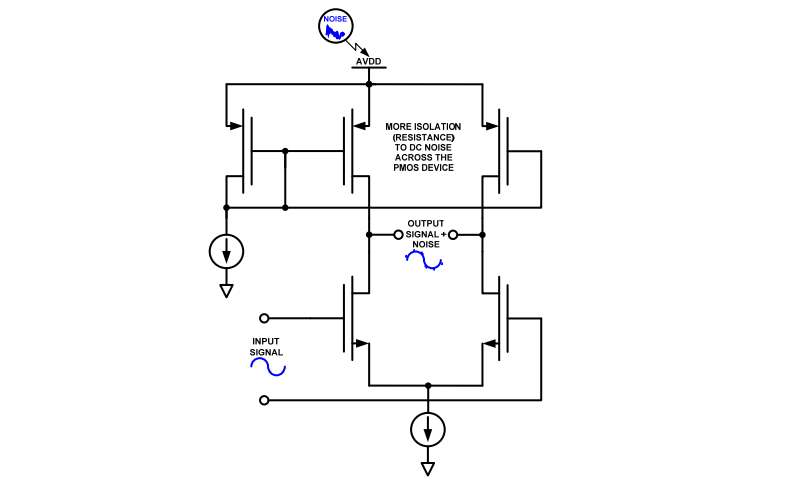

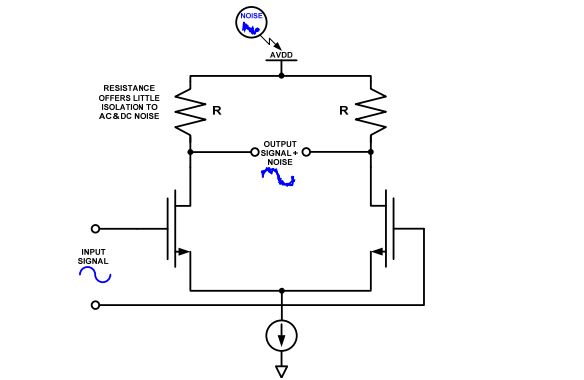

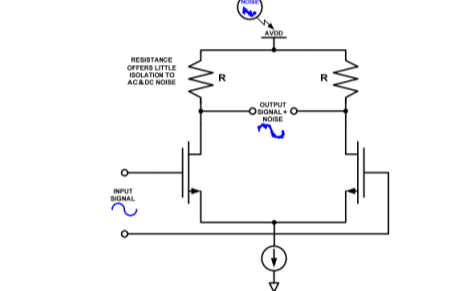

由該圖可以推論出是電源引腳。用一個模擬電源引腳(AVDD)代替圖 2 中的采樣時鐘輸入引腳。相同的原理在此同樣適用,即任何噪聲(近載波噪聲或寬帶噪聲)將以這種卷積方式出現在輸出頻譜上。然而,有一點不同;可以將電源引腳視為帶一個 40 dB 至 60 dB 的衰減器(具體取決于工藝和電路拓撲結構)的寬帶輸入引腳。在通用型 MOS 電路 結構中,任何源極引腳或漏極引腳在本質上都是與信號路徑相隔離的(呈阻性),從而帶來大量衰減,柵極引腳或信號路徑則不是這樣。假定該設計采用正確的 電路結構類型來使隔離效果達到最大化。在電源噪聲非常明顯的情況下,有些類型(如共源極)可能并不是十分合適,因為電源是通過阻性元件偏置的,而該阻性元件后來又連接到輸出 級,如圖 3 和圖 4 所示。AVDD 引腳上的任何調制、噪聲等可能更容易表現出來,從而對局部和 / 鄰近電路造成影響。這正是需要了解并探索轉換器 PSRR 數據的原因所在。

圖 3. 不同的電路拓撲結構——實現方案 A

圖 4. 不同的電路拓撲結構——實現方案 B

正如不同實現方式所示,存在寄生 R、C 和失配造成的不同頻率特性。記住,工藝也在不斷變小,隨著工藝的變小,可用帶寬就會增加,可用速率也會提升。考慮到這一點,這意味著更低的電源和更小的閾值。為此,為什么不把電源節點當作高帶寬輸入呢,就像采樣時鐘或模擬輸入引腳一樣呢?

何謂電源抑制

當供電軌上有噪聲時,決定 ADC 性能的因素主要有三個,它們是 PSRR-dc、PSRR-ac 和 PSMR。PSRR-dc 指電源電壓的變化與由此產生的 ADC 增益或失調誤差的變化之比值,它可以用最低有效位(LSB)的分數、百分比或對數 dB (PSR = 20 × log10 (PSRR))來表示,通常規定采用直流條件。

但是,這種方法只能揭示 ADC 的一個額定參數隨電源電壓可能會如何變化,因此無法證明轉換器的穩定性。更好的方法是在直流電源之上施加一個交流信號,然后測試電源抑制性能(PSRR-ac),從而主動通過轉換器電路耦合信號(噪聲源)。這種方法本質上是對轉換器進行衰減,將其自身表現為雜散(噪聲),它會在某一給定幅度升高至轉換器 噪底以上。其意義是表明在注入噪聲和幅度給定的條件下轉換器何時會崩潰。同時,這也能讓設計人員了解到多大的電源噪聲會影響信號或加入到信號中。PSMR 則以不同的方式影響轉換器,它表明當與施加的模擬輸入信號進行調制時,轉換器對電源噪聲影響的敏感度。這種影響表現為施加于轉換器的 IF 頻率附近的調制,如果電源設計不嚴 謹,它可能會嚴重破壞載波邊帶。

總之,電源噪聲應當像轉換器的任何其他輸入一樣進行測試和處理。用戶必須了解系統電源噪聲,否則電源噪聲會提高轉換器噪底,限制整個系統的動態范圍。

電源測試

圖 6 所示為在系統板上測量 ADC PSRR 的設置。分別測量每個電源,以便更好地了解當一個交流信號施加于待測電源之上時,ADC 的動態特性。開始時使用一個高容值電容,例如 100 μF 非極化電解質電容。電感使用 1 mH,充當直流電源的交流阻塞器,一般將它稱為“偏置 -T”,可以購買采用連接器式封裝的產品。

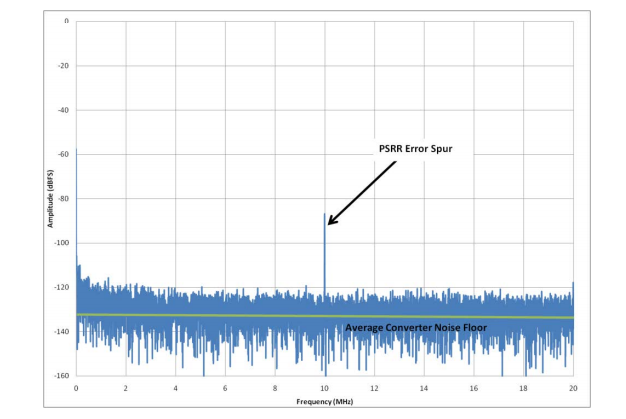

使用示波器測量交流信號的幅度,將一個示波器探針放在電源進入待測 ADC 的電源引腳上。為簡化起見,將施加于電源上的交流信號量定義為一個與轉換器輸入滿量程相關的值。例如,如果 ADC 的滿量程為 2V p-p,則使用 200 mV p-p 或–20 dB。接下來讓轉換器的輸入端接地(不施加模擬信號), 查找噪底 /FFT 頻譜中處于測試頻率的誤差雜散,如圖 5 所示。若要計算 PSRR,只需從 FFT 頻譜上所示的誤差雜散值中減去–20 dB 即可。例如,如果誤差雜散出現在噪底的–80 dB 處,則 PSRR 為–80 dB – –20 dB,即–60 dB(PSRR = 誤差雜散(dB) – 示波器測量結果(dB))。–60 dB 的值似乎并不大,但如果換算成電壓,它相當于 1 mV/V(或 10?60/20),這個數字對于任何轉換器數據手冊中的 PSRR 規格而言都并不鮮見。

圖 5. PSRR—FFT 頻譜示例

圖 6. 典型的 PSRR 測試設置

下一步是改變交流信號的頻率和幅度,以便確定 ADC 在系統板中的 PSRR 特性。數據手冊中的大部分數值是典型值,可能只針對最差工作條件或最差性能的電源。例如,相對于其他電源,5 V 模擬電源可能是最差的。應確保所有電源的特性都有說明,如果說明得不全面,請咨詢廠家。這樣,設計人員將能為每個電源設置適當的設計約束條件。

請記住,使用 LC 配置測試 PSRR/PSMR 時有一個缺點。當掃描目標頻段時,為使 ADC 電源引腳達到所需的輸入電平,波形發生器輸出端所需的信號電平可能非常高。這是因為 LC 配置會在某一頻率(該頻率取決于所選的值)形成陷波濾波器。這會大大增加陷波濾波器處的接地電流,該電流可能會進入模擬輸入端。要解決這一問題,只需在測試頻率 造成測量困難時換入新的 LC 值。這里還應注意,LC 網絡在直流條件下也會發生損耗。記住要在 ADC 的電源引腳上測量直流電源,以便補償該損耗。例如,5 V 電源經過 LC 網絡后,系統板上可能只有 4.8 V。要補償該損耗,只需升高電源電壓即可。

PSMR 的測量方式基本上與 PSRR 相同。不過在測量 PSMR 時,需將一個模擬輸入頻率施加于測試設置,如圖 7 所示。

圖 7. 典型的 PSMR 測試設置

另一個區別是僅在低頻施加調制或誤差信號,目的是查看此信號與施加于轉換器的模擬輸入頻率的混頻效應。對于這種測試,通常使用 1 kHz 至 100 kHz 頻率。只要能在基頻周圍看到誤差信號即混頻結果,則說明誤差信號的幅度可以保持相對恒定。但也不妨改變所施加的調制誤差信號幅度,以便進行檢查,確保此值恒定。為了獲得最終結果, 最高(最差)調制雜散相對于基頻的幅度之差將決定 PSMR 規格。圖 8 所示為實測 PSMR FFT 頻譜的示例。

圖 8. PSMR—部分 FFT 頻譜示例

電源噪聲分析

對于轉換器和最終的系統而言,必須確保任意給定輸入上的噪聲不會影響性能。前面已經介紹了 PSRR 和 PSMR 及其重要意義,下面將通過一個示例說明如何應用所測得的數值。該示例將有助于設計人員明白,為了了解電源噪聲并滿足系統設計需求,應當注意哪些方面以及如何正確設計。

首先,選擇轉換器,然后選擇調節器、LDO、開關調節器等。并非所有調節器都適用。應當查看調節器數據手冊中的噪聲和紋波指標,以及開關頻率(如果使用開關調節器)。典型調節器在 100 kHz 帶寬內可能具有 10 μV rms 噪聲。假設該噪聲為白噪聲,則它在目標頻段內相當于 31.6 nV rms/√Hz 的噪聲密度。

接著檢查轉換器的電源抑制指標,了解轉換器的性能何時會因為電源噪聲而下降。在第一奈奎斯特區 fS/2,大多數 高速轉換器的 PSRR 典型值為 60 dB (1 mV/V)。如果數據手冊 未給出該值,請按照前述方法進行測量,或者詢問廠家。

使用一個 2 V p-p 滿量程輸入范圍、78 dB SNR 和 125 MSPS 采樣速率的 16 位 ADC,其噪底為 11.26 nV rms。任何來源的噪聲都必須低于此值,以防其影響轉換器。在第一奈奎斯特區,轉換器噪聲將是 89.02 μV rms (11.26 nV rms/√Hz) × √(125 MHz/2)。雖然調節器的噪聲(31.6 nv/√Hz)是轉換器的兩倍以上,但轉換器有 60 dB 的 PSRR,它會將開關調節器的噪聲抑制到 31.6 pV/√Hz (31.6 nV/√Hz × 1 mV/V)。這一噪聲比轉換器的噪底小得多,因此調節器的噪聲不會降低轉換器的性能。

電源濾波、接地和布局同樣重要。在 ADC 電源引腳上增加 0.1 μF 電容可使噪聲低于前述計算值。請記住,某些電源引腳吸取的電流較多,或者比其他電源引腳更敏感。因此應當慎用去耦電容,但要注意某些電源引腳可能需要額外的去耦電容。在電源輸出端增加一個簡單的 LC 濾波器也有助 于降低噪聲。不過,當使用開關調節器時,級聯濾波器能將噪聲抑制到更低水平。需要記住的是,每增加一級增益就會每 10 倍頻程增加大約 20 dB。

最后需要注意的一點是,這種分析僅針對單個轉換器而言。如果系統涉及到多個轉換器或通道,噪聲分析將有所不同。例如,超聲系統采用許多 ADC 通道,這些通道以數字方式求和來提高動態范圍。基本而言,通道數量每增加一倍,轉換器 / 系統的噪底就會降低 3 dB。對于上例,如果使用兩個轉換器,轉換器的噪底將變為一半(?3 dB);如果 使用四個轉換器,噪底將變為?6 dB。之所以如此,是因為每個轉換器可以當作不相關的噪聲源來對待。不相關噪聲源彼此之間是獨立的,因此可以進行 RSS(平方和的平方根)計算。最終,隨著通道數量增加,系統的噪底降低,系統將變得更敏感,對電源的設計約束條件也更嚴格。

-

轉換器

+關注

關注

27文章

8639瀏覽量

146894 -

開關電源

+關注

關注

6449文章

8290瀏覽量

480802 -

adc

+關注

關注

98文章

6452瀏覽量

544147

發布評論請先 登錄

相關推薦

如何幫助高速轉換器設計電源

如何為高速轉換器設計電源

如何為高速轉換器設計電源

評論