在電源研發的過程中,我們總會遇到這樣或者那樣的問題,這里有大牛多年研發電源問題及解答,一起學習吧!

話不多說,直接上題。

問題一

我們小功率用到多的反激電源,為什么我們常常選擇65K或者100K(這些頻率段附近)作為開關頻率?有哪些原因制約了?或者哪些情況下我們可以增大開關頻率?或者減小開關頻率?

開關電源為什么常常選擇65K或者100K左右范圍作為開關頻率,有的人會說IC廠家都是生產這樣的IC,當然這也有原因。每個電源的開關頻率會決定什么?

應該從這里去思考原因。還會有人說頻率高了EMC不好過,一般來說是這樣,但這不是必然,EMC與頻率有關系,但不是必然。想象我們的電源開關頻率提高了,直接帶來的影響是什么?當然是MOS開關損耗增大,因為單位時間開關次數增多了。如果頻率減小了會帶來什么?開關損耗是減小了,但是我們的儲能器件單周期提供的能量就要增多,勢必需要的變壓器磁性要更大,儲能電感要更大了。選取在65K到100K左右就是一個比較合適的經驗折中,電源就是在折中合理化折中進行。

假如在特殊情形下,輸入電壓比較低,開關損耗已經很小了,不在乎這點開關損耗嗎,那我們就可以提高開關頻率,起到減小磁性器件體積的目的。

關鍵:如何選擇合適IC的開關頻率?主流IC的開關頻率為什么是大概是這么一些范圍?開關頻率和什么有關,說的是普遍情況,不是想鉆牛角尖好多IC還有什么不同的頻率。更多的想發散大家思維去注意到這些問題!

我這里想說的普遍情況,主要想提的是開關頻率和什么有關,如何去選擇合適開關頻率,為什么主流IC以及開關頻率是這么多,注意不是一定,是普遍情況,讓新手區理解一般行為,當然開關電源想怎么做都可以,要能合理使用。

1、你是如何知道一般選擇65或者100KHZ,作為開關電源的開關頻率的?(調研普遍的大廠家主流IC,這二個會比較多,當然也有一些在這附近,還有一些是可調的開關頻率)

2、又是如何在工作中發現開關電源開關頻率確實工作在65KHZ,或100KHZ的。(從設計角度考量,普遍電源使用這個范圍)

3、有兩張以上的測試65KHZ100KHZ頻率的圖片說明嗎?(何止二張圖片,毫無意義)

4、你是否知道開關電源可以工作在1.5HZ.(你覺得這樣談有必要,工作沒有什么不可以,純熟鉆牛角尖,做技術切記鉆牛角尖,那你能談談為什么普遍電源不工作在1.5HZ,說這個才有意義,你做出1.5HZ的電源純屬毫無意義的事情)

提醒:做技術人員切記鉆牛角尖,咱們不是校園研究派,是需要將理論與實踐現結合起來,做出來的產品才是有意義的產品!

問題二

LLC中為什么我們常在二區設計開關頻率?一區和三區為什么不可以?有哪些因素制約呢?或者如果選取一區和三區作為開關頻率會有什么后果呢?

LLC的原理是利用感性負載隨開關頻率的增大而感抗增大,來進行調節輸出電壓的,也就是PFM調制。并且MOS管開通損耗ZVS比ZCS小,一區是容性負載區,自然不可取。那么三區,開關頻率大于諧振頻率,這個仍是感性負載區,按道理MOS實現ZVS沒有問題,確實如此。但是我們不能忽略副邊的輸出二極管關斷。

也就是原邊MOS管關斷時,諧振電流并沒有減小到和勵磁電流相等,實現副邊整流二極管軟關斷。這也是我們通常也不選擇三區的原因。

我們不能只按前人的經驗去設計,而要知道只所以這樣設計是有其必然的道理的!

問題三

當我們反激的占空比大于50%會帶來什么?好的方面有哪些?不好的方面有哪些?

反激的占空比大于50%意味著什么,占空比影響哪些因素?:占空比設計過大,首先帶來的是匝比增大,主MOS管的應力必然提高。一般反激選取600V或650V以下的MOS管,成本考慮。占空比過大勢必承受不起。

第二點:很重要的是很多人知道,需要斜坡補償,否則環路震蕩。不過這也是有條件的,右平面零點的產生需要工作在CCM模式下,如果設計在DCM模式下也就不存在這一問題了。這也是小功率為什么設計在DCM模式下的其中一個原因。當然我們設計足夠好的環路補償也能克服這一問題。

當然在特殊情形下也需要將占空比設計在大于50%,單位周期內傳遞的能量增加,可以減小開關頻率,達到提升效率的目的,如果反激為了效率做高,可以考慮這一方法。

問題四

反激電源如果要做到一定的效率,需要從哪些方面著手?準諧振?同步整流?

反激的一大劣勢就是效率問題,改善效率有哪些途徑可以思考的呢?減小損耗是必然的,損耗的點有開關管,變壓器,輸出整流管,這是主要的三個部分。

開關管我們知道反激主要是PWM調制的硬開關居多,開關損耗是我們的一大難點,好在軟開關的出現看到了希望。反激無法向LLC那樣做到全諧振,那只能朝準諧振去發展(部分時間段諧振),這樣的IC也有很多問世,我司用的較多是NCP1207,通過在MOS管關斷后,下開通前1腳檢測VCC電壓過零后,然后在一個設定時間后開通下一周期。

變壓器的損耗如何做到,完美使用的變壓器后面問題會涉及到。

同步整流一般在輸出大電流情況下,副邊整流流二極管,哪怕用肖特基損耗依然會很大,這時候采用同步整流MOS替代肖特基二極管。有些人會說這樣成本高不如用LLC,或者正激呢,當然沒有的,只有更合適的。

問題五

電源的傳導是怎么形成的?傳導的途徑有哪些?常用的手段?電源的輻射受哪些東西影響?怎么做大功率的EMC。

電源傳導測量方式是通過接收輸入端口L,N,PE來自電源內部的高頻干擾(一般150K到30M)。

解決傳導必須弄清楚通過哪些途徑減弱端口接收到的干擾。

如圖:一般有二種模式:L,N差模成分,以及通過PE地回路的共模成分。有些頻率是差共模均有。

通過濾波的方式:一般采用二級共模搭配Y電容來濾去,選擇的方式技巧也很重要,布板影響也很大。一般靠近端口放置低U電感,是鎳鋅材質,專門針對高頻,繞線方式采用雙線并繞,減少差模成分。后級一般放置感量較大,在4MH到10MH附近,只是經驗值,具體需要與Y電容搭配。X電容濾差模也需要靠近端口,一般放在二級共模中間。放置Y電容,電容布板時走線需要加粗,不可外掛,否則效果很差。(這些只是輸入濾波網絡上做文章)

當然也可以從源頭上下手,傳導是輻射耦合到線路中的結果,減弱了開關輻射也能對傳導帶來好處。影響輻射的幾處一般有MOS管開通速度,整流管導通關斷,變壓器,以及PFC電感等等。這些電路上的設計需要與其他方面折中不做詳述。

一些經驗技巧:針對大功率的EMC一般需要增加屏蔽,立竿見影,屏蔽的部位一般有幾處選擇:

第一:輸入EMI電路與開關管間屏蔽,這對EMC有很大的作用,很多靠濾波器無效的采用該方法一般很有效果。

第二:變壓器初次級屏蔽,一般設計變壓器若有空間加上屏蔽。

第三:散熱器的位置能很好充當屏蔽,合理布板利用,散熱器接地選擇也很重要。

第四:判斷輻射源頭位置,一般有幾個簡單的方法,不一定完全準確,可以參考,輸入線套磁環若對EMC有好處,一般是原邊MOS管,輸出線套磁環若對EMC有效果,一般是副邊輸出整流管,尤其是大于100M的高頻。可以考慮在輸出加電容或者共模電感。

當然還有很多其他的細節技巧,尤其是布板環路方面的,后面對LAYOUT會單獨講解。

問題六

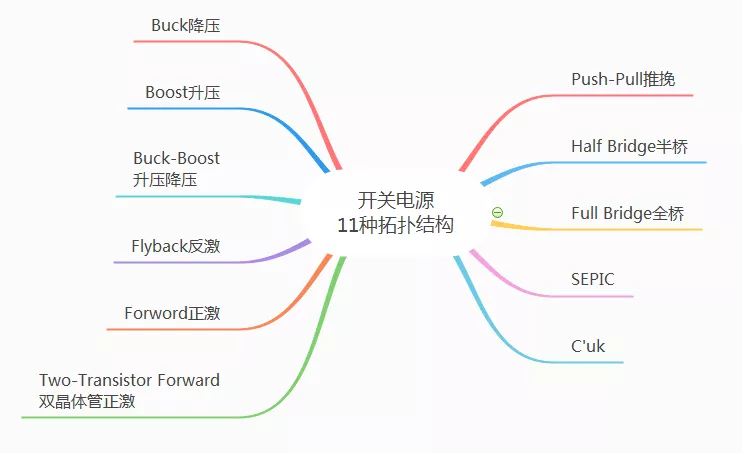

我們選擇拓撲時需要考慮哪些方面的因素?各種拓撲使用環境及優缺點?

設計電源的步不知道大家會想到什么呢?我是這么想,細致研究客戶的技術指標要求,轉換為電源的規格書,與客戶溝通指標,不同的指標意味著設計難度和成本,也是對我提出的問題有很大的影響,選擇拓撲時根據我們的電源指標結合成本來考慮的,哪常用的幾種拓撲特點在哪呢 ?

這里主要談隔離式,非隔離式應用有限,當然也是成本的。

反激特點:

適用在小于150W,理論這么說,實際大于75W就很少用,不談很特殊的情況。反激的有點成本低,調試容易(相對于半橋,全橋),主要是磁芯單向勵磁,功率由局限性,效率也不高,主要是硬開關,漏感大等等原因。全電壓范圍(85V-264V)效率一般在80%以下,單電壓達到80%很容易。

正激特點:

功率適中,可做中小功率,功率一般在200W以下,當然可以做很大功率,只是不常常這么做,原因是正激和反激一樣單向勵磁,做大功率磁芯體積要求大,當然采用2個變壓器串并聯的也有,注意只談一般情形,不誤導新人。

正激有點,成本適中,當然比反激高,優點效率比反激高,尤其采用有源箝位做原邊吸收,將漏感能量重新利用。

半橋:

目前比較火的是LLC諧振半橋,中小功率,大功率通吃型。(一般大于100W小于3KW)。

特點成本比反激正激高,因為多用了1個MOS管(雙向勵磁)和1個整流管,控制IC也貴,環路設計業復雜(一般采用運放,尤其還要做電流環)。優點:采用軟開關,EMC好,效率極高,比正激高,我做過960W LLC,效率可達96%以上(全電壓)(當然PFC是采用無橋方式)。

其它半橋我不推薦,至少我不會去用,比較老的不對稱橋,很難做到軟開關,LLC成熟以前用的多,現在很少用,至少艾默生等大公司都傾向于LLC,跟著主流走一般都不會錯。

全橋:

一般用在大于2KW以上,首推移相全橋,特點,雙向勵磁,MOS管應力小,比LLC應力小一半,大功率尤其輸入電壓較高時,一般用移相全橋,輸入電壓低用LLC。

成本特別高,比LLC還多用2個MOS。這還不是首要的,主要是驅動復雜,一般的IC驅動能力都達不到,要將驅動放大,采用隔離變壓器驅動,這里才是成本高的另一方面。

推挽:

應用在大功率,尤其是輸入電壓低的大功率場合,特點電壓應力高,當然電流應力小,大功率用全橋還是推挽一般看輸入電壓。

變壓器多一個繞組,管子應力要求高,當然常提到的磁偏磁也需要克服。這個我真沒用過,沒涉及電力電源,很難用到它的時候。

問題七

考慮電源成本時,我們要從哪里下手呢?

設計電源,成本評估必不可少,目前客戶將電源的成本壓得很低,各大競爭對手無不都在打價格戰,大家都能做出電源來,就看誰做得更便宜,才能贏得訂單,從哪些方面入手有利于我們陳本呢:

第一:技術指標。電源技術指標越高,成本越高,如果你的電源成本高了,那你可以打你的性能指標賣點,多了性能要求,電路增多了成本自然高。也是和客戶談話的資本。

第二:物料采購成本,為什么大公司電源利潤高?無非是他們有著優越的采購平臺,采購量大,物料成本低,當然成本更低。如果不考慮采購,作為工程師必須弄清楚不同物料對應的成本,比如能用貼片,少用插件,(比如插件電阻比貼片成本高),能用國產,不用臺資,能用臺資不用日系,這里的價格差異不菲。(比如日系電容比國產電容價格高幾倍不止!!!當然質量也有差異;)

第三:影響成本的重要器件:變壓器,電感,MOS管,電容,光耦,二極管及其他半導體器件,IC等。不同的變壓器廠家繞出來的變壓器價格差異很大,MOS管應力,熱阻選擇夠用就行,IC方案的成本等等

其它方面導致成本問題:器件散熱器,大小合適,多了就是浪費錢。PCB布板,能用單面板用成雙面板就是浪費錢,PCB布板工藝,選擇合理的工藝加工成本低,生產效率高。

問題八

電源的環路設計,電源哪些部分影響電源的環路?好的環路有哪些指標決定?

電源的環路設計一直是一個難點,為什么這么說,因為主要影響的因素太多,理論計算很難做到準確,仿真也是基于理想化模型,在這里只談關于環路設計的一些影響因素,從定性的角度去理解環路以及怎么去做環路補償。

環路是基于輸入輸出波動時,需要通過反饋,環路相應告知控制IC去調節,維持輸出的穩定。電源環路一般都是串聯負反饋,有的是電壓串聯負反饋(CC模式下),有的是電流串聯負反饋(CV模式下)。

那有哪些地方會影響環路呢?電路中的零點以及極點。零點一般會導致增益上升,引起90度相移(右半平面零點會引起-90度相移)。極點一般會導致增益下降,引起-90度相移,左半平面極點會引起系統震蕩。所以我們需要借助零點極點補償手段去合理調控我們的環路。對于低頻部分,為了滿足足夠增益一般引入零點補償,對于高頻干擾一般引入極點補償去抵消,減少高頻干擾。

環路穩定的原則是:

1.在穿越頻率處(即增益為零dB時的頻率),系統的相位余量大于45度。

2.在相位達到-180度時增益的余量大于-12dB.3.避免過快的進入穿越頻率,在進入穿越頻率附近的曲線斜率為-1.

針對一般反激電路:

1.產生零點的有輸出濾波電容 :可以使環路增益上升。(一般在中頻4K左右,對增益有好處,無需補償)

2.若工作在CCM模式下還會產生右半平面零點。在高頻段,可采用極點補償。這個一般很難補償,盡量避免,讓穿越頻率小于右半平面零點頻率(15K左右,隨負載變化會變化),選取3.負載會產生低頻極點。采用低頻零點去補償。4.LC濾波器會產生低頻極點,需要采用零點補償。在心中要清楚哪些零極點是利是弊,針對性補償。

補償的電路,針對電源環路來說比較簡單,一般采用對運放采用2型補償,也有的會采用3型補償很少用。

問題九

對各種拓撲的軟開關形式有哪些?軟開關是如何實現的?

軟開關目前使用很頻繁,一來可以提升次效率,二來可以利于EMC。很多拓撲都開始利用軟開關了,就連反激如果為了做高效率也引入了準諧振來實現軟開關,這個在前面問題已講過。LLC的軟開關在前面問題也提過實現條件,具體實現過程沒有細講。這里就分享下我對軟開關的理解。

實現條件及過程:利用軟開關需要二個元素,一個是C一個是L來實現諧振(當然也可以多諧振形式),諧振會產生正弦波,正弦波就能實現過零。如果是串聯諧振屬于電壓諧振,并聯諧振屬于電流諧振。

其次軟開關和硬開關的差異是:硬開關過程中電壓電流有重疊,軟開關要么電流為零(ZCS)要么電壓為零(ZVS)。MOS管的軟開關可以利用結電容或者并電容,然后串電感實現串聯ZVS,例如準諧振反激,有源箝位吸收電路,移向全橋的軟開關。

也有LC并聯ZCS,不過用的很少,因為MOS管ZVS的損耗小于ZCS。LLC屬于串并聯式,不過我們利用的是ZVS區。(在死區的時候諧振電流過零,上管軟開通前,先給下管結電容充電,上管實現軟開通)

問題十

什么樣的變壓器才算是完美適用的?變壓器決定了什么,影響了什么?

設計變壓器是各種拓撲的點之一,變壓器設計的好壞,影響電源的方方面面,有的無法工作,有的效率不高,有的EMC難做,有的溫升高,有的極限情況會飽和,有的安規過不了,需要綜合各方面的因素來設計變壓器。

設計變壓器從哪里入手呢?一般來說根據功率來選擇磁芯大小,有經驗的可參考自己設計過的,沒經驗的只能按照AP算法去算,當然還要留有一定的余量,實驗去檢驗設計的好壞。

一般小功率反激推薦的用的比較多EE型,EF型,EI型,ER型,中大功率PQ的用的比較多,這里面也有每個人的習慣以及不同公司的平臺差異,功率很大的,沒有適合的磁芯,可以二個變壓器原邊串副邊并的方式來做。

不同拓撲對變壓器的要求也不一樣,比如反激,需要考慮的是需要工作在什么模式下,感量如何調節適中。尤其是多路輸出一定要注意負載調整率滿足需求,耦合的效果要好,比如采用并繞,均勻繞制,以及副邊匝數盡可能增多。

MOS管耐壓決定匝比,怎么選取合適的占空比,選取多大的Bmax(一般小于0.35,當然0.3更好,即時短路也不會飽和太嚴重)有的還需要增加屏蔽來整改EMC,原副邊屏蔽一般加2層,外屏蔽1層就好。

大功率變壓器一般更多的是關注損耗,需要銅損和磁損達到平衡,還要考慮到風冷自然冷,電流密度多大合適,功率稍大(大于150W)的一般電流密度相對取小些(3.5-4.5),功率小的(5.0-7.0)。

還要清楚電源過的什么安規,擋墻是不是足夠,層間膠帶是否設置合理也是不可以忽視的,一旦要做去改變壓器也是影響進度的。

問題十一

我們真的需要到迷戀設計工具,依賴仿真的地步嗎?

電源的設計工具主要用在以下幾個方面:1.選擇磁芯及設計變壓器 2.環路仿真設計 3.主功率拓撲仿真4.模擬電路仿真 5.熱仿真(針對大功率)6.計算工具(計算書) 等等。

對于新人來說,我給的建議少用工具,多計算,自己把握設計的過程,因為工具是人做的,不同人的設計習慣差異,不能用一個固定的設計模式來設計不同的電源。

有些仿真可以與設計相結合:比如環路設計好后是很難直接滿足設計需求的,仿真可以在試驗前很好驗證,但仿真也不是完全和試驗一樣,至少不會差太遠。

熟練運用Mathcad和Saber也是必要的,只是很多我們需要弄清原理的層面,把工具只需要當做計算器來使用,更快速方便更高效來滿足我們設計就好,想純依賴工具來設計電源,無疑是走入極大誤區。

問題十二

評判一塊電源板LAYOUT好壞有哪些地方能一陣見血發現?

什么樣的PCB是一塊好的PCB,至少要滿足以下一個方面:

1.電性能方面干擾小,關鍵信號線及底線走的合理,各方面性能穩定(前提是電路無缺陷)。

2.利于EMC,輻射低,環路走的合理。

3.滿足安規,安規距離滿足要求。4.滿足工藝,量產可生產性,以及減小生產成本。5.美觀,布局規則有序(器件不東倒西歪),走線漂亮美觀,不七彎八繞的。

如何才能做到以上幾點,分享我的布板經驗:

1.布局前

了解清楚電源的規格書,電源的規格,有無特殊要求,以及要過的安規標準。

結構輸入條件是不是準確,以及風道的確認,輸入輸出端口的確認,以及主功率流向。

工藝路線選取,根據器件的密度,以及有無特殊器件,選擇相對應工藝路線。

2.布局中

注意合理的布局,保證四大環路盡可能小,提前預判后續走線是否好走。變壓器的擺放基本決定了整體的布局,一定要慎重,放到位置。

EMI部分的布局流向清晰,與其它主功率部分有清晰的隔離帶。減少受到主功率開關器件的干擾。各吸收回路的面積盡可能小,散熱器的長度以及位置要合理,不擋風道。

3.走線部分

輸入EMI電路的走線是否滿足安規,原副邊距離,輸入輸出對大地的距離都要滿足安規。

走線的粗細是否滿足足夠的電流大小,關鍵信號(例如驅動信號,采樣信號,地線是否合理),驅動信號不要干擾敏感信號(高頻信號);采樣信號是否采樣準確,是否會受到干擾;地線是否拉得合理(有時需要單點接地,有時需要多點接地跟實際需要有關),主功率地和信號地嚴格區分開,原邊芯片地從采樣電阻取,不要從大電解取(尤其是采樣電阻和大電解地距離遠時),VCC的地前級地回大電解,二級電容地接芯片,反饋信號也單點接IC,地單點接IC。

散熱器的地必須接主功率地,不能接信號地等等很多的細節要求。

問題十三

電源的元器件你懂多少?MOS管結電容多大,對哪些有影響?RDS跟溫度是什么關系?肖特基反向恢復電流影響什么?電容的ESR會帶來哪些影響?

電源中的設計的器件類型很多,主要有半導體器件如:MOS管,三極管,IC,運放,二極管,光耦等;磁性器件:電感,變壓器,磁珠等;電容:Y電容,X電容,瓷片電容,電解電容,貼片電容等;每種器件都有其規格,極限參數。

常規的參數在我們選型很容易把握,例如選取MOS管,耐壓參數肯定會考慮,額定電流也會考慮,導通電阻我們會考慮,但還有一些寄生參數以及一些隨溫度變化特 性的參數卻很少去注意,或者只有在發現問題的時候才會去找。

導通電阻Rds(on)隨溫度升高其阻值是變大的,設計MOS管損耗時要考慮到其工作的環境溫 度。結電容影響到我們的開通損耗,也會影響到EMC。

肖特基二極管耐壓,額定電流一般很好注意,有些參數例如導通壓降在溫度升高時會減小,反向恢復時間短,不過漏電流大(尤其是考慮到高溫時漏電流影響就更大了),寄生電感會引起關斷尖峰很高。

電容一個重要參數ESR,在計算紋波時通常會考慮,ESR一般與C的關聯是很大的,不過不同廠家的品質因素影響也是很巨大,一定要具體分清楚。

一般估算公司可參考:ESR=10/(C的0.73次方),電容在高溫時壽命會縮短,低溫時容量會減小,漏電流也會增加等等;

當然器件在特殊情形表現出來的特性差異是值得我們思考的問題,請大家多多思量,對于我們解決特殊情況下的問題非常有幫助。

問題十四

你對磁性材料了解多少,磁環和磁芯有哪些差異?低磁環和高磁環用在什么情況?

磁性器件對開關電源的重要性不言而喻,可以說是電源的心臟部位。磁性材料的種類也繁多,常用來做變壓器的一般是鐵氧體材料,主要是價格便宜,開關頻率 能做到1000K,夠一般情況下使用了。

鐵氧體磁芯既可以做主變壓器也可以做電感,如PFC電感(一般鐵硅鋁材質居多,性價比高),儲能電感也可以。當然在要求高的情況下,尤其是大功率一般用磁環,主要是感量可以做大,不易飽和,相對鐵氧體磁芯來說,不過缺點是價格貴,尤其是大電流,繞制工藝較困難。

磁環也分高U值和低U值,主要也是磁環的材料不同照成,高U環磁環外觀是綠色,一般EMI電路的共模電感選用,感量會相對較大濾低頻,顏色偏灰的是低U環,感量很低,濾高頻。一般為了EMC都是搭配使用效果一般都比較好!

問題十五

電源損耗是怎么分布的?MOS管損耗?變壓器損耗?變壓器除了直流損耗,還有交流損耗怎么算的?

電源損耗一般集中在以下一些方面:

1.MOS管的開通損耗及導通損耗;

2.變壓器的銅損和鐵損;

3.副邊整流管的損耗;

4.橋式整流的損耗;

5.采樣電阻損耗;

6.吸收電路的損耗;

7.其它損耗:PFC電感損耗,LLC的諧振電感損耗,同步整流的MOS管損耗等等……

針對這些損耗,適當的減小可以提升效率:

1.針對MOS管可選用開關速度快的,導通電阻低的,電路上課采用軟開關;

2.針對變壓器:選擇合適大小的磁芯,磁 芯太小損耗會大,很難做到銅損和鐵損平衡。

尤其是銅損不僅有直流損耗還有交流損耗,交流損耗一般比直流損耗還大2倍,因為銅線在高頻下的交流阻抗比直流阻 抗大的多,計算時一定要充分估算進去。

問題十六

電源中的熱設計,散熱器是怎么選擇的?散熱器設計需要考慮什么?

散熱器的設計是開關電源的一個重點,散熱器主要是針對我們的發熱器件溫升過高,需要采用散熱器來降低熱阻來達到降低溫升的作用!

主要發熱器件:整流橋,MOS管,整流二極管,變壓器,電感等等。

散熱器的大小選擇一般根據損耗的功率,需要的溫升來計算熱阻,根據熱阻來選擇相應面積的散熱器 。

當然也需要一些輔助的方式,比如在器件和散熱片間涂散熱膏,有會有些效果。比較小的空間可采用型材散熱,體積小,散熱面積大。

特殊器件有特殊的處理:如變壓器可將變壓器底下的PCB板挖空散熱,也可以在變壓器上用導熱泥貼散熱片的方式。電感也可以加銅環散熱等等……

問題十七

LLC的輸出濾波電容怎么決定的?受哪些因素影響?

輸出濾波電容對輸出紋波至關重要,選擇合適的濾波電容需要從成本及紋波需求考慮,當然對每種拓撲濾波電容的選取都是按照輸出紋波需求,紋波電流所對應的 ESR值來選取對應的電容,當然電容的容量與ESR的關系跟電容的品質也有著很重要的關系,之前已經討論過其關系式。

紋波電壓時我們的需求,一般按照 50mv的需求的話,設計留有余量一般選擇10mv。(考慮到PCB板濾波效果,電容低溫容值降低),紋波電流計算式如下:

問題十八

移相全橋的驅動是什么實現的?何為移相?移相帶來什么?

移相全橋目前在中大功率使用中,也是用的很火,受歡迎程度僅次于LLC諧振半橋。之前已經比較過不同拓撲的使用情況,這里就專門介紹下移相全橋的特點。

移相全橋特點一:

驅動比較復雜,導致控制電路復雜,成本很高,原因是移相全橋一般有4個MOS,對驅動能力要求很高,一般IC很難做到,需要對驅動能力通過外置MOS管放大使用,又為了加強可靠性一般采用隔離變壓器來驅動MOS管。

移相全橋特點二:

移相,為什么要移相,移相帶來什么,跟普通全橋有什么區別。移相針對的是同一組的MOS管,讓2個MOS管依次導通,可以降低開關損耗。超 前臂橋實現ZVS同時,副邊處于續流,原邊電流被二極管分擔,MOS管電流也很小,近似零電流導通,滯后臂橋可以零電壓導通。

移相全橋特點三:

工作過程復雜,二個輸出功率狀態(靠原邊提供能量),二個續流狀態(靠副邊電感及電容提供供能量),四個死區(來分別實現每個MOS管軟開通I)

只是為了給新手了解移相全橋,作為開關電源比較重要的拓撲一部分,它的重點和難點在哪里。

問題十九

大功率若追求效率,無橋PFC是怎么實現的?原理是什么?

很多人都聽說過無橋PFC,不過真正使用起來并不很常見,原因是無橋PFC相比普通有橋PFC效率上固然有提升,一般也就在1-2%,若不是追求高效,一般都不會使用,成本太高。

根據無橋PFC的特點,其實整流橋并沒有真正省去不用,只是當做交流輸入正負半軸的隔離使用,簡單來說相當于普通二個PFC,交流 正負半軸各一個,相應的PFC電感也會增加一個,MOS管也會增加一個,驅動IC也會復雜一些,對于大功率為了做高效,檢測電阻用變壓器繞組來做,可以減小損耗。

之前接觸過一個960W用無橋PFC+LLC效率達到96.5%,不過終因為客戶要求輸入電壓交流和直流都能滿足,這時候無橋PFC就不能在直 流下發揮很好的作用就否決了。

問題二十

電力電源中為什么用到三相電?三相三電平是怎么實現,三電平帶來了什么?

三相電在電力電源中使用比較多,一般在大功率1KW以上或者上萬W的場合。

三相電一般采用三相四線,其中一根是零線,四根線相當于能夠傳輸普通二相電三倍的功率,傳輸功率更大是其優勢;其次三相電易于產生,目前常見的三相異步電機,能簡單方便產生。

三相三電平是怎么回事呢,因為三相電不能直接給某些用電設備供電,需要轉變成普通的二相電。

一般過程,采用三相PFC轉換為直流電,直流電然后逆變成二相交 流電。這里面就牽涉到三電平技術,三相電PFC整流出來不是普通正負DC,而是三電平,也就是正DC,零,負DC。

從這里也可以看出來采用三電平器件的應 力降低,諧波含量低,開關管損耗也低,這樣在高壓大功率場合優勢就非常突出了。

問題二十一

電源中有很多保護電路,你多能說幾種保護?怎么去實現?

電源的可靠性離不開保護電路,通常有哪些保護電路呢?

1.輸入欠壓過壓很常用,對交流信號采樣。

2.輸出過壓保護,一旦電源開關能鎖機對電源可靠性也有幫助。

3.過流保護,有的是采用恒流做過流,有的采用限功率來做過流,當然也可以鎖機來做,目的一個可靠性,方法很多種。可靠的保護一定是鎖死而不是打嗝!

4.過溫保護,采用熱敏對變壓器或者是環境溫度等方式檢測,來反饋給到IC鎖機或者打嗝。

5.短路保護,短路可以打嗝,同樣也可以鎖機。

這些是一般電源常用的,有的可以說是必備的保護電路。所以看好規格書選擇合適的IC來做保護功能更方便的保護電路。我用過一款LD7522做反激,這些功能就能很好,可以簡單全部的做出來。

問題二十二

一般的LDO和高PSRR的LDO有甚么分別?

這個問題問得非常典型,其實一般的LDO是起到穩定電壓的作用,它對溫波造成的控制抑制基本集中在10K以下,在典型的 LDO數據手冊里面,在10K或是100K以下的 PSR通常是在40DB以下,因為此時的LDO誤差放大器基本上已經失去了放大能力。

對于實際的需求來說,很多DCDC電源它的溫波頻率是在幾百 K甚至上兆,如果是一個普通的 LDO,對于這樣的噪聲抑制沒有任何能力,它只對聲頻范圍有抑制能力,對于需要射頻應用的場合,LDO通常是無能為力的,而高PSR的 LDO則能提供這方面的抑制,所以這也是一個根本上的完全不同的區別。

問題二十三

搞電源不懂市場?你搞的電源何去何從?開發出了沒用?替老板賺到錢才有用。

終于到了一個問題,電源市場問題一般工程師可能關注的少,注重研發是錯誤。項目成功不是做出來,而是賺到少的錢。

舉個例子:你一年做了三個項目累死累活,賺了100萬,另一個人一年就做了一個項目,比做三個項目輕松多了,一年賺了1000萬,老板喜歡哪個?

有的人說項目又不是我們選擇,怎么知道賺不賺錢,但是賺錢項目的特點我們要熟悉啊,什么樣的電源市場上比較火啊,你清楚嗎?

按照自己公司現有的模式來開發, 有沒有和大公司的設計差距啊。不是說項目能不能做出來,而是能不能的做出來,其實站在研發角度也就是如何選擇拓撲,做省方案。

-

電源

+關注

關注

184文章

17606瀏覽量

249564 -

電源研發

+關注

關注

0文章

6瀏覽量

1285

原文標題:電源大牛多年研發經驗匯總:設計不止于技巧

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

BQ2404x、BQ2405x和BQ2409x常見問題解答

OMAPL138/C6748 ROM引導加載程序資源和常見問題解答

常見的電源研發問題及解答

常見的電源研發問題及解答

評論