AXI4讀操作

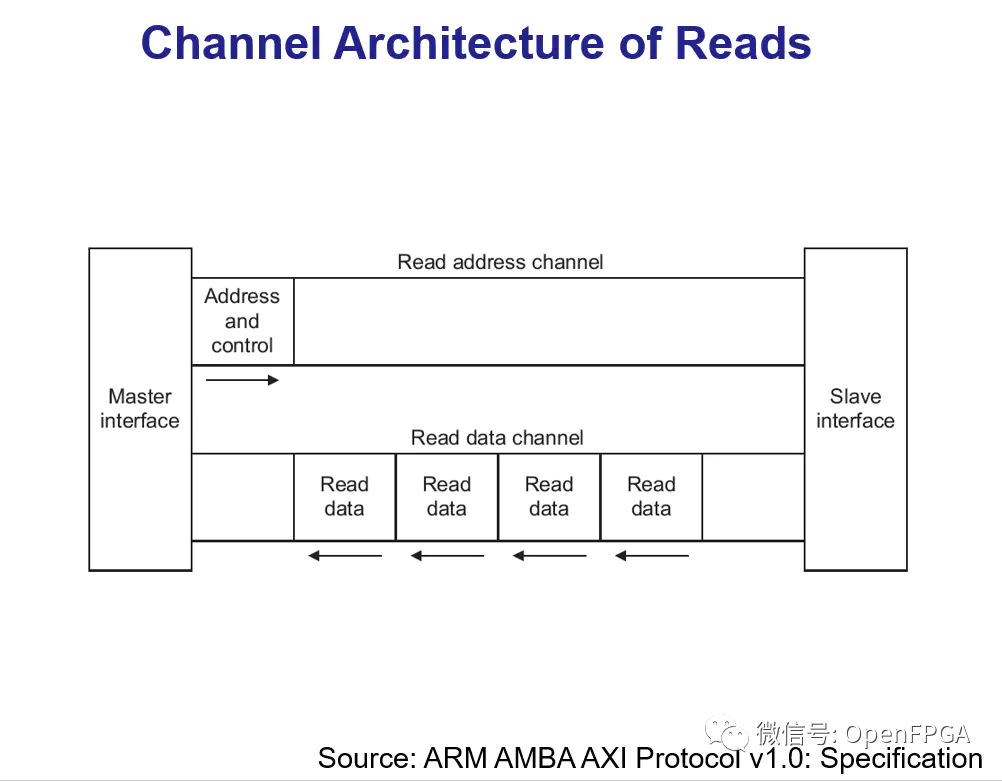

圖 4?15 讀通道架構

如上圖所示,主設備向從設備通過讀地址通道指定讀數據地址及控制信號,從設備通過讀數據通道將指定地址上的數據傳輸給主設備。

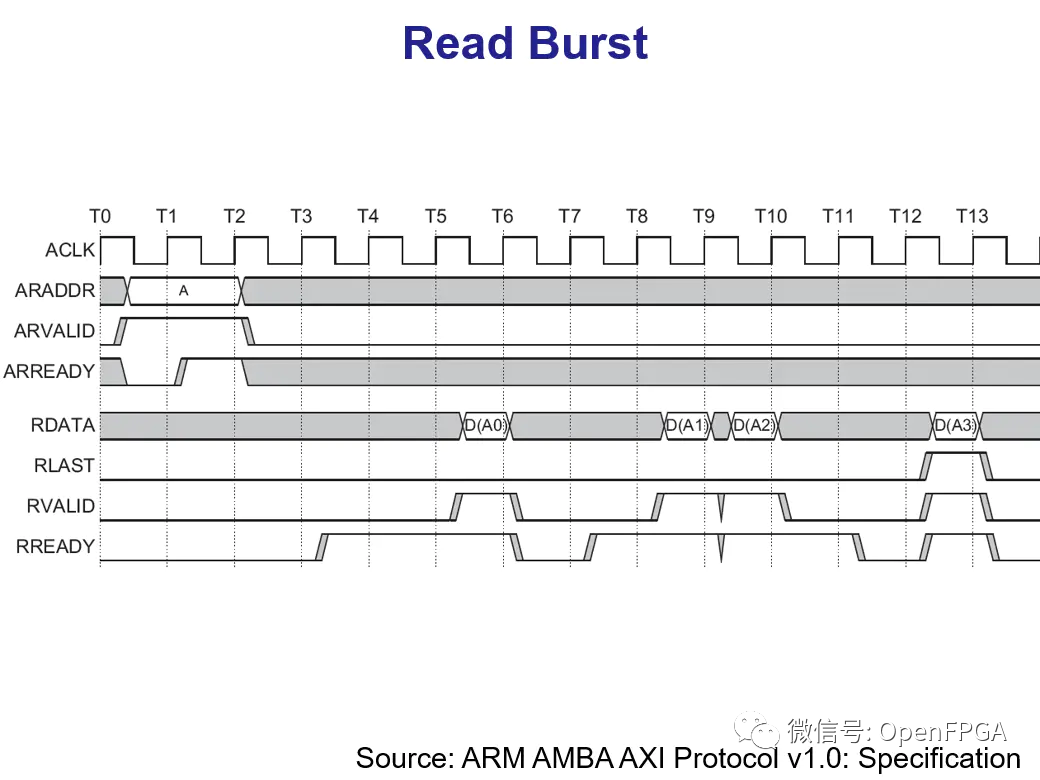

1、當狀態機的當前狀態為WAIT_START時,master將ARVALID拉高。

2、slave收到ARVALID信號后,將ARREADY拉高,持續到一次burst_len傳完為止。master收到ARREADY拉高的信號后,將ARVALID拉低。

3、ARADDR在ARVALID為高時給定對應地址。

4、RREADY信號在收到RVALID信號為高時拉高,保持一個周期,讀取出數據。

5、RVALID信號由slave控制,具體控制模式參考slave模塊的設計。

6、當一次讀取的最后一個數據包讀取時將RLAST拉高,表示一次Burst讀取完畢。

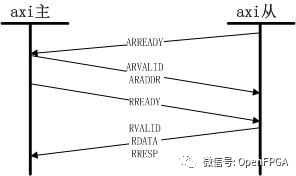

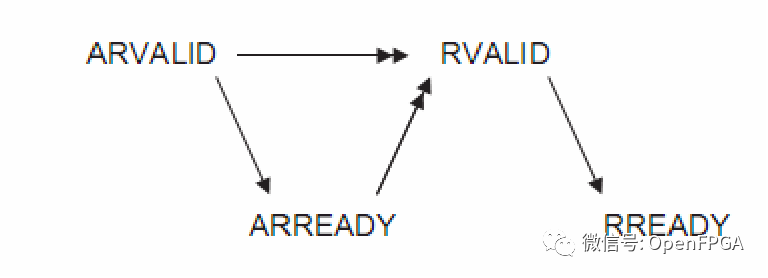

圖4?17 讀操作信號依賴

如圖可知,讀操作的兩個channel之間存在如下的依賴關系:必須等到ARVALID和ARREADY同時為High后,RVALID才能拉高。

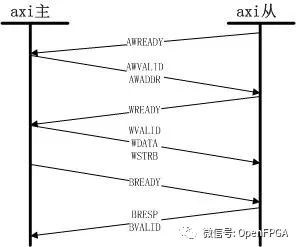

AXI4寫操作:

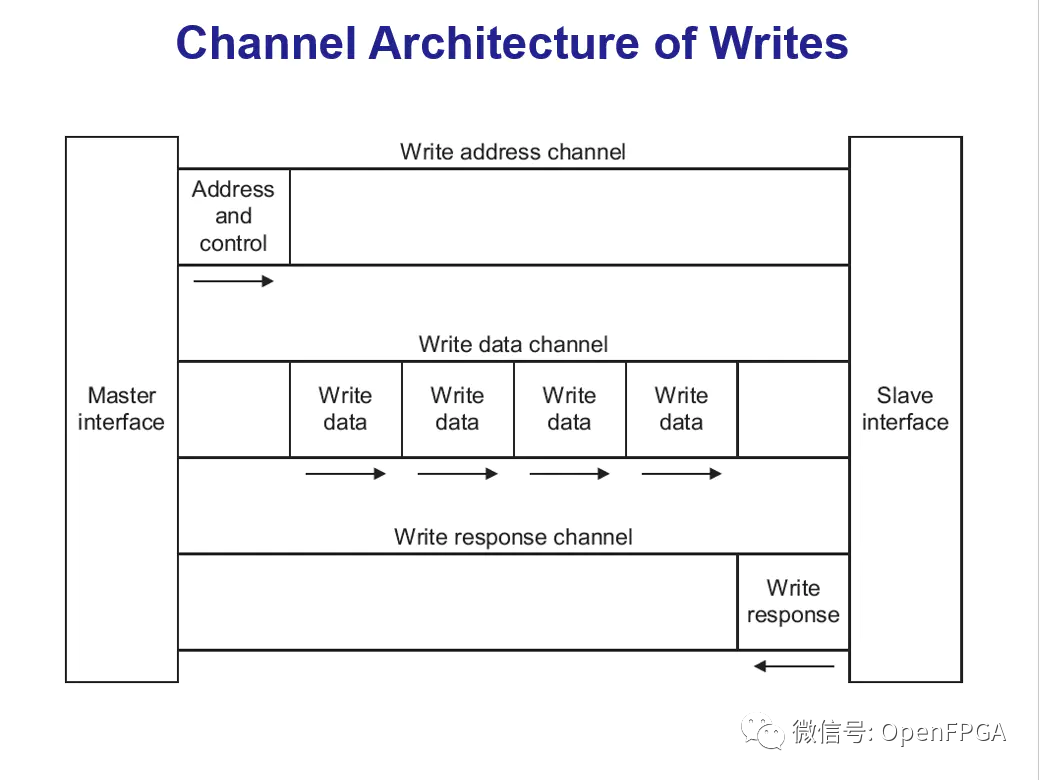

圖4?18 寫通道架構

如上圖所示,主設備向從設備通過寫地址通道指定寫數據地址及控制信號,從設備通過寫數據通道將指定數據寫到從設備的指定地址上。待數據寫入完成后,從設備通過寫響應通道向主設備傳遞寫響應信號,表明寫入完成。

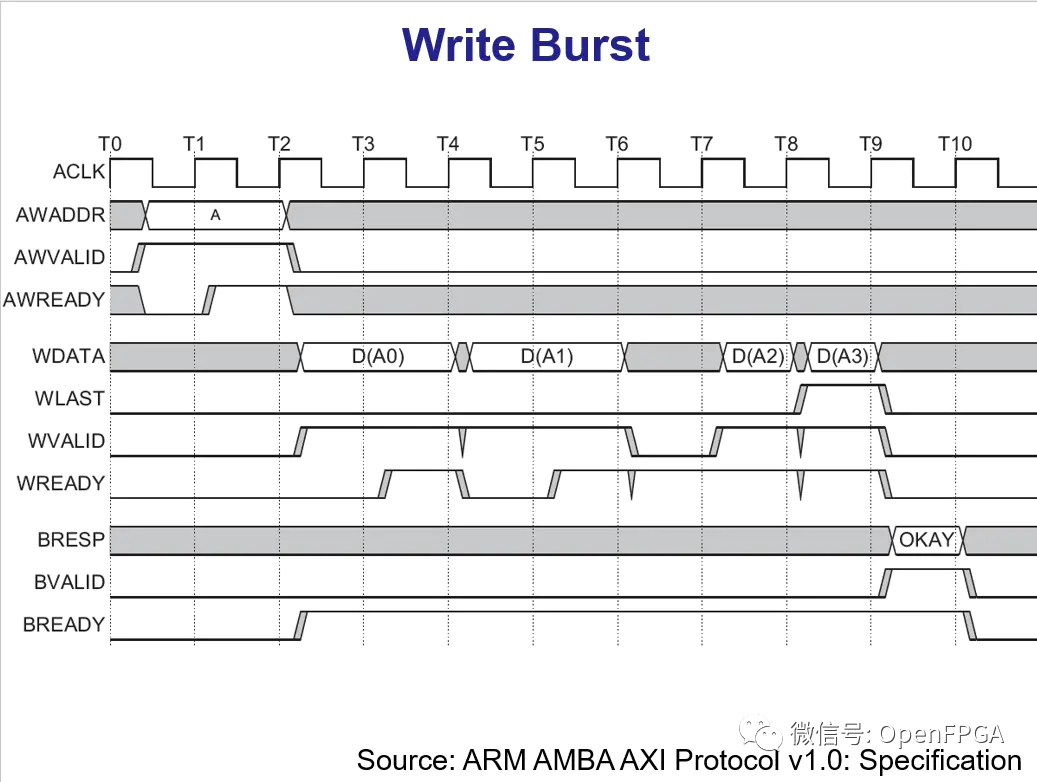

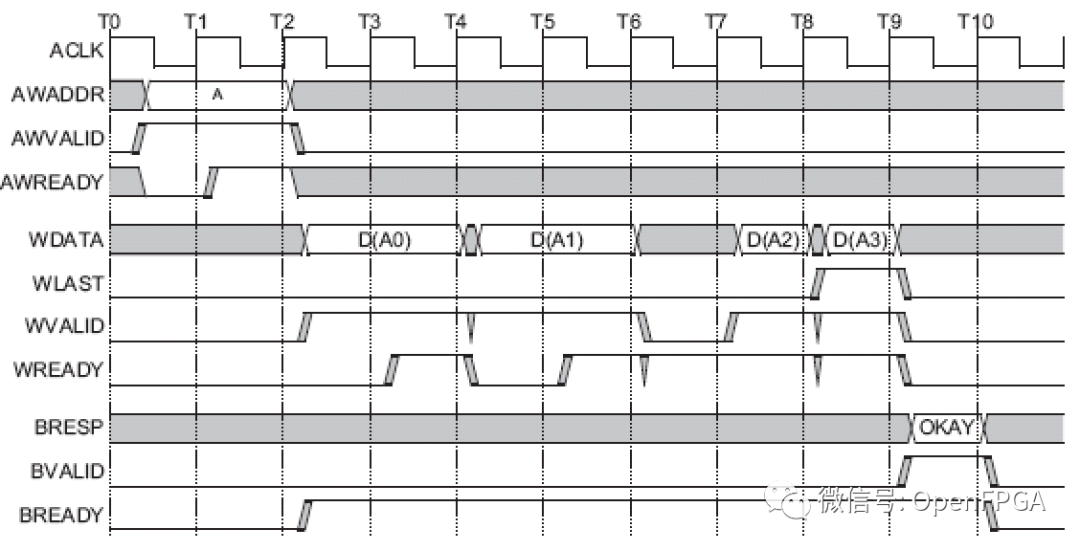

圖4?19 Write Burst 流程

1、當狀態機的當前狀態為WAIT_START時,master將AWVALID拉高。

2、slave收到AWVALID信號后,將AWREADY拉高,持續到一次burst_len寫完為止.master收到AWREADY拉高的信號后,將AWVALID拉低。

3、AWADDR在AWVALID為高時給定對應地址。

4、WREADY信號在收到WVALID信號為高時拉高,保持一個周期,寫入數據。

5、WVALID信號由slave控制,具體控制模式參考slave模塊說明。

6、當一次寫入的最后一個數據包讀取時將WLAST拉高,表示一次寫入完畢。

7、BRESP和BVALID都由slave控制,當收到WLAST信號時,BVALID拉高。

8、BREADY可以一直拉高,也可以在AWREADY信號拉高后保持拉高。直到BVALID信號拉高時將其拉低即可。

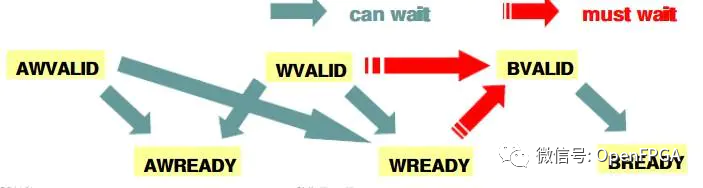

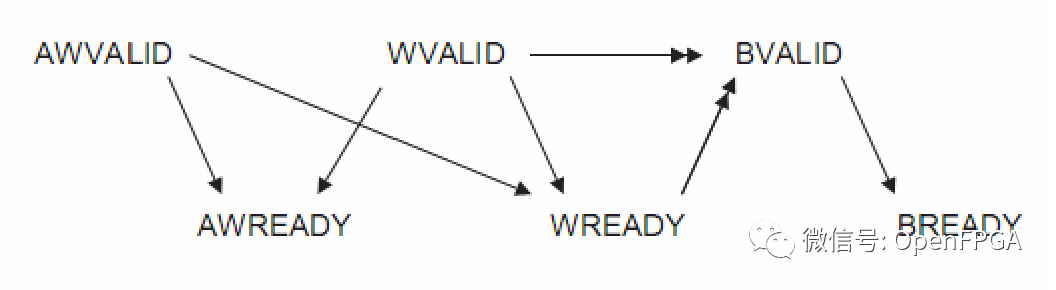

其中寫操作的信號依賴關系如下:

圖4?20 寫操作依賴

如圖可知,ADDR和DATA兩個channel之間不存在依賴關系,需要滿足的是必須等到WVALID和WREADY同時為High,且最后一次傳輸完成后,BVALID才能拉高,表明寫操作結束。

通道握手信號之間的依賴關系

為了對VALID和READY之間的關系有更深刻理解,下面在展開說明一下。

為了防止發生死鎖,必須重視握手信號之間的依賴關系。

任何交易中:

l一個 AXI 模塊的VALID 信號不能依賴于另一個模塊的READY 信號

lREADY 信號可以等待VALID 信號使能

-------------------注意---------------------------------------------

可以在使能 VALID 信號之后使能READY,也可以在使能VALID 信號之前將

READY 信號使能為默認值,這樣設計更高效。.

--------------------------------------------------------------------

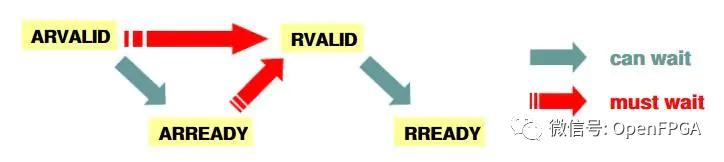

圖4?21和圖4?22為各握手信號之間的依賴關系圖。單箭頭指向的信號可以在指向它的信號未使能或使能后,它再使能;雙箭頭向的信號,必須在指向它的信號全都使能后,它再使能。

圖4?21中所示,在一次讀交易中:

l從設備使能ARREADY 信號之前,可以在等待 ARVALID 信號被使能。

l從設備必須等待ARVALID 和ARREADY信號都有效后,再去使能RVALID 信號以返回讀數據

圖4?21 讀交易中握手信號的依賴關系

圖4?22中所示,在一次寫交易中:

l主設備必須等待從設備使能AWVALID 、WVALID信號之后,主設備再去使能AWREADY 、WREADY信號。

l從設備可以等待使能AWREADY、WVALID信號或者同時使能倆個信號后,再去使能AWREADY。

l從設備可以等待使能AWREADY、WVALID信號或者同時使能倆個信號后,再去使能AWREADY。

l從設備可以等待使能AWREADY、WVALID信號或者同時使能倆個信號后,再去使能AWREADY。

圖4?22 寫交易握手信號依賴關系

注意:

在一次寫交易中,主設備不必等AWREADY 有效之后去發送WVALID ,這一點是很重要的。如果主設備在發送WVALID 信號之前,必定不會等待使能AWREADY 信號,反過來如果從設備在等待使能WVALID 信號,再去使能AWREADY則這樣就會造成死鎖狀況。

AXI協議中的基本交易

本部分給出基于 AXI協議的基本交易的示例。每個示例都使用了VALID 和READY握手機制。地址信息及數據的傳輸都是在VALID 和READY 信號同時為高的時候傳輸。示例下面幾部分介紹:

?讀猝發示例

?連續的讀猝發示例

?寫猝發示例

本部分也介紹了交易順序。

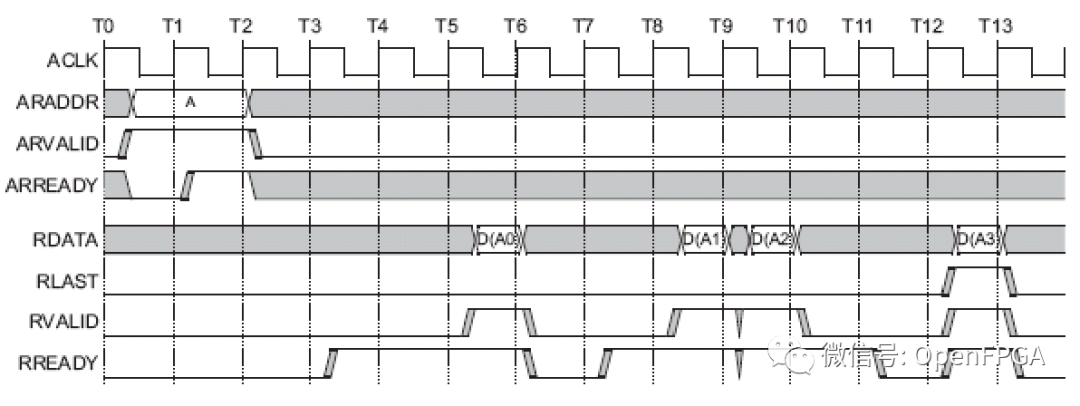

讀猝發示例

圖4?23為一個4 拍的讀猝發 交易的時序圖。在這個例子中,主設備發送地址,一個周期后從設備接收。

主設備在發送地址的同時也發送了一些控制信息,用于記錄猝發的類型和長度,為了保持圖的清晰性,在此省略這些信號。

地址總線上出現地址之后,在讀數據通道上發生數據的傳輸。從設備一直保持

VALID 信號為低,直到讀數據準備好。從設備發送RLAST 信號標志著此次猝發交易中這是最后一個數據的傳輸。

圖4?23 讀猝發交易

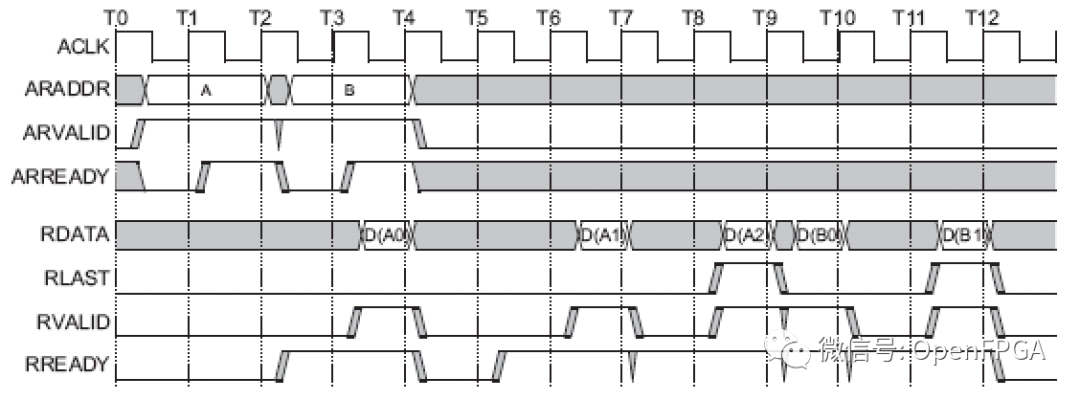

交疊讀猝發示例

圖4?24為主設備在從設備接收第一個猝發交易的地址后發送另一個猝發交易的地址的時序圖。這樣可以保證一個從設備在完成第一個猝發交易的同時可以開始處理第二個猝發 交易的數據。

圖4?24 交疊讀猝發交易

寫猝發示例

圖4?25為一次寫交易的時序圖。當主設備發送地址和控制信息到寫地址通道之后,交易過程開始。然后主設備通過寫數據通道發送每一個寫數據,當為最后一個需要發送的數據時,主設備將WLAST 信號置高。當從設備接收完所有的數據時,從設備返回給主設備一個寫響應信號標志本次寫交易的結束。

圖4?25 寫猝發交易

信號描述

定義了AXI協議中使用的信號。雖然總線寬度和交易ID的寬度都是需要具體說明的,但在本章的表中先顯示32位的數據總線,一個4位的寫入數據選通,和4位的ID域。本章包含以下幾個部分:

l全局信號

l寫地址通道信號

l寫數據通道信號

l寫響應通道信號

l讀地址通道信號

l讀數據通道信號

l低功耗接口信號

全局信號

表4?12 AXI全局信號

| 信號名 | AXI4 | AXI4-Lit |

| ACLK | 全局時鐘。所有的信號在全局時鐘的上升沿采樣 | |

| ARESETN | 全局復位,低有效。 |

寫地址通道信號

表4?13 寫地址通道信號

| 信號名 | 源 | AXI4 | AXI4-Lit |

| AWID | 主 | 寫地址ID。這個信號用于寫地址信號組的標記。 | 不支持 |

| AWADDR | 主 | 寫地址。寫地址給出突發數據傳輸的第一個傳輸地址。 | |

| AWLEN | 主 | 突發長度。給出突發傳輸中準確的傳輸個數。支持INCR和WRAP傳輸模式。 | 不支持 |

| AWSIZE | 主 | 突發大小。這個信號用于確定突發傳輸中每個傳輸的大小。 | 不支持 |

| AWBURST | 主 | 突發類型。該信息與突發大小信息一起,表示在突發過程中,地址如何應用于每個傳輸。支持INCR和WRAP傳輸模式。 | 不支持 |

| AWLOCK | 主 | 鎖類型。該信號提供了關于傳輸原子特性的額外信息(普通或互斥訪問)。 | 不支持 |

| AWCACHE | 主 | 緩存類型,建議值為0011。 | |

| AWPROT | 主 | 保護類型,建議值為000。 | |

| AWQOS | 主 | QoS標識符,xilinx AXI4不支持。 | 不支持 |

| AWREGION | 主 | 用于每個寫操作的地址通道上的域標識符。 | 不支持 |

| AWUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| AWVALID | 主 | 寫地址有效信號。為高指示地址有效。 | |

| AWREADY | 從 | 寫地址準備信號。為高表示從設備空閑,準備接收地址;為低表示從設備忙。 |

寫數據通道信號

表4?14 寫數據通道信號

| 信號名 | 源 | AXI4 | AXI-Lite |

| WDATA | 主 | 寫數據,32位到1024位寬 | 只支持32位寬 |

| WSTRB | 主 | 寫字節選通,用于表示更新存儲器的字節通道,對于數據總線的每8位數據有一位寫選通信號。 | 從設備端可選擇忽略。 |

| WLAST | 主 | 寫最后一個數據指示信號。表示突發傳輸中的最后一個數據。 | 不支持 |

| WUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| WVALID | 主 | 寫有效。為高指示數據有效。 | |

| WREADY | 從 | 寫準備。為高表示從設備空閑,準備接收數據;為低表示從設備忙。 |

寫響應通道信號

表4?15 寫響應通道信號

| 信號名 | 源 | AXI4 | AXI-Lite |

| BID | 從 | 響應ID。寫響應識別標記,BID值必須匹配AWID值。 | 不支持 |

| BRESP | 從 | 寫響應。該信號表示寫狀態,可允許相應的表示為OKAYEXOKAYSLVERRDECERR。 | EXOKAY狀態不支持 |

| BUSER | 從 | xilinx AXI4不支持。 | 不支持 |

| BVALID | 從 | 寫響應有效。為高指示響應數據有效。 | |

| BREADY | 主 | 寫響應準備。為高表示主設備空閑,準備接收寫響應;為低表示主設備忙。 |

讀地址通道信號

表4?16 讀地址通道信號

| 信號名 | 源 | AXI4 | AXI-Lite |

| ARID | 主 | 讀地址ID。這個信號用于讀地址信號組的標記。 | 不支持 |

| ARADDR | 主 | 讀地址。讀地址給出突發數據傳輸的第一個傳輸地址。 | |

| ARLEN | 主 | 突發長度。給出突發傳輸中準確的傳輸個數。支持INCR和WRAP傳輸模式。 | 不支持 |

| ARSIZE | 主 | 突發大小。這個信號用于確定突發傳輸中每個傳輸的大小。 | 不支持 |

| ARBURST | 主 | 突發類型。該信息與突發大小信息一起,表示在突發過程中,地址如何應用于每個傳輸。支持INCR和WRAP傳輸模式。 | 不支持 |

| ARLOCK | 主 | 鎖類型。該信號提供了關于傳輸原子特性的額外信息(普通或互斥訪問)。 | 不支持 |

| ARCACHE | 主 | 緩存類型,建議值為0011。 | |

| ARPROT | 主 | 保護類型,建議值為000。 | |

| ARQOS | 主 | QoS標識符,xilinx AXI4不支持。 | 不支持 |

| ARREGION | 主 | 用于每個讀操作的地址通道上的域標識符。 | 不支持 |

| ARUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| ARVALID | 主 | 讀地址有效信號。為高指示地址有效。 | |

| ARREADY | 從 | 讀地址準備信號。為高表示從設備空閑,準備接收地址;為低表示從設備忙。 |

讀數據通道信號

表4?17 讀數據通道信號

| 信號名 | 源 | AXI4 | AXI-Lite |

| RID | 從 | 讀ID標記,該信號是讀數據信號組標記,由從設備產生RID,RID必須和讀交易中的ARID匹配。 | 不支持 |

| RDATA | 從 | 讀數據。32位到1024位寬 | 只支持32位寬 |

| RRESP | 從 | 讀響應。該信號表示讀狀態,可允許相應的表示為OKAYEXOKAYSLVERRDECERR。 | EXOKAY狀態不支持 |

| RLAST | 從 | 讀最后一個數據指示信號。表示突發傳輸中的最后一個數據。 | 不支持 |

| RUSER | 從 | xilinx AXI4不支持。 | 不支持 |

| RVALID | 從 | 讀有效。為高指示數據有效。 | |

| RREADY | 主 | 讀準備。為高表示主設備空閑,準備接收數據;為低表示主設備忙。 |

AXI4-Stream信號

| 信號名 | 源 | 默認值 | 功能 |

| TVALID | No | N/A | Stream讀寫數據有效。為高指示數據有效。 |

| TREADY | Yes | 1 | Stream讀寫讀準備。為高表示對端設備空閑,準備接收數據;為低表示對端設備忙。 |

| TDATA | Yes | 0 | Stream讀寫數據,8到4096位寬。 |

| TSTRB | Yes | 同TKEEP,否則為1 | 字節選通信號。用于表示更新存儲器的字節通道,對于數據總線的每8位數據有一位選通信號。 |

| TKEEP | Yes | 1 | 字節選通信號。TKEEP未被確認的那些相關的字節是空字節,可以從數據流中去除。 |

| TLAST | Yes | 0 | 表明包的邊界。 |

| TID | Yes | 0 | 數據流標識符。 |

| TDEST | Yes | 0 | 數據流路由信息。 |

| TUSER | Yes | 0 | 用戶定義的邊帶信息,這些信息能伴隨數據流進行發送。 |

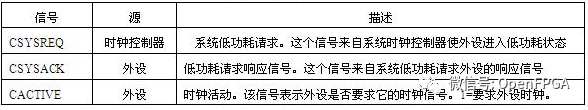

低功耗接口信號

表4?18 低功耗接口信號

AXI4猝發地址及選擇

地址選擇

主要描述AXI猝發類型、在一次猝發過程中如何計算地址以及字節傳輸的通道。包含章節如下:

●關于地址選擇

●猝發長度

●猝發大小

●猝發類型

●猝發地址

關于地址選擇

AXI協議是基于猝發方式,主設備開始每次的猝發,是通過發送傳輸所需的控制信息和傳輸過程中所需的首字節地址的方式,隨著猝發交易進行,從設備負責計算接下來的傳輸所需要的地址。

猝發數不能超過4KB臨界值,這是為了防止猝發長度在從設備之間出現交叉現象,同時也限制了從設備需要地址增量的大小。

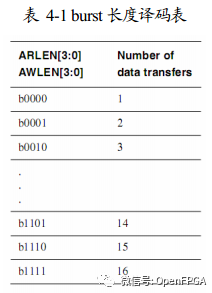

猝發長度

AWLEN 或ARLEN信號說明每次猝發傳輸開始時,數據傳輸的個數,如下圖所示,每猝發可以傳輸長1-16個數據。

圖4?26 每猝發可以傳輸長1-16個數據

對于循回猝發方式來講,猝發的長度必須是2,4,8,或16。

每次交易進行時,必須通過設置AWLEN 或ARLEN信號來確定傳輸長度,任何器件都不能通過盡早地終止猝發的方式去減少數據傳輸個數。在一次寫猝發的過程中,主設備通過禁止寫選通信號的方式終止進一步的寫操作,但是它必須完成本次猝發中剩下數據傳輸。在一次讀猝發過程中,主設備能丟棄進一步的讀到數據,但是它必須完成在本次猝發中剩下的數據傳輸。

-------------------注意---------------------------------------------

當訪問一個讀敏感設備例如FIFO時,拋棄不需要的讀數據會導致丟失數據。主設備不會來訪問這樣一種設備,它使用的猝發長度比自身需要的還長。--------------------------------------------------------------------

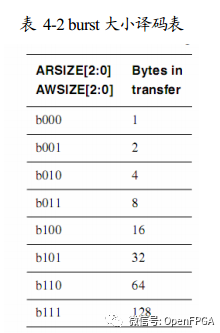

猝發大小

下圖中顯示, 通過ARSIZE 或AWSIZE信號設定了,在一次猝發中,每一時鐘節拍內傳輸數據字節的最大字節數,或數據傳輸的最大字節數。

圖4?27 burst大小譯碼表

AXI協議通過傳輸地址來決定使用哪一個數據總線上的字節通道進行傳輸。

對于地址遞增或地址循回的猝發,并且要求傳輸數據的寬度比數據總線上的要窄,這中猝發過程中,每次數據傳輸,使用不同的字節通道,這些通道對應于猝發中每一個時鐘節拍。一個固定格式的猝發,其地址保持不變,每拍數據傳輸都使用相同的字節通道。

任何數據傳輸的寬度都不能超過交易中期間的數據總線寬度。

猝發類型

AXI 協議定義了三種猝發類型:

●地址固定的猝發

●地址遞增的猝發

●地址循回的猝發

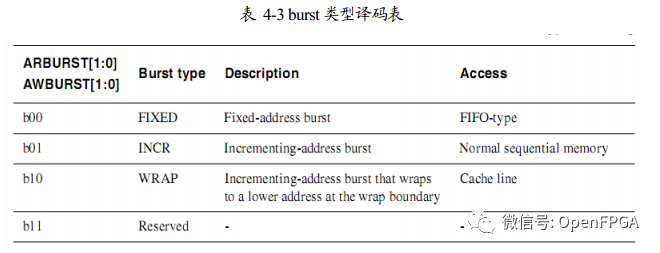

下圖顯示了如何通過ARBURST 或 AWBURST信號選擇猝發類型。

圖4?28 burst類型譯碼表

地址固定的猝發

在固定猝發類型中,猝發過程中,每次傳輸地址保持一樣。如當加載或者清空一個FIFO外設時,使用這種類型可以重復訪問同一個位置。

地址遞增的猝發

在地址遞增的猝發類型中,猝發中每次傳輸所需的地址是通過增加前一個傳輸地址來得到。增加的值取決于傳輸量的大小。例如:一次猝發中,每次傳輸所需的地址為四個字節,那么這個地址就是有前一個地址值加四得到的。

地址循回的猝發

地址循回的猝發類型類似于地址遞增猝發類型,在地址遞增猝發類型中,每次傳輸所需的地址值是前一次傳輸地址的遞增,而在地址循回猝發類型中,當到達循回的邊界時,地址再次回到低地址。循回的邊界是指,每次猝發的大小乘以該猝發過程的傳輸總量。

對于地址循回的猝發有兩個限制:

●起始地址必須與數據的大小對齊

●猝發的長度必須為 2,4,8 或16

猝發地址

這一節提供一些簡單的公式,在猝發過程中,用于確定地址和傳輸字節通道。公式中使用到的變量如下:

Start_Address 主設備發起的起始地址

Number_Bytes 每次數據傳輸中允許的最大的字節數

Data_Bus_Bytes 數據總線上的字節通道數

Aligned_Address 與起始地址對齊的類型

Burst_Length 一次猝發中數據傳輸的總量

Address_N 猝發中傳輸N的地址,N是2-16之間的一個整數。

Wrap_Boundary 一次循回猝發中的最低地址

Lower_Byte_Lane 一次傳輸中最低地址對應的字節通道

Upper_Byte_Lane 一次傳輸中最高地址對應的字節通道

INT(x) x四舍五入后的值

使用如下公式確定猝發過程中的傳輸地址 :

● Start_Address = ADDR

● Number_Bytes=2SIZE

● Burst_Length= LEN+1

●Aligned_Address=(INT(Start_Address / Number_Bytes))x Number_Bytes

使用如下公式確定猝發中首次傳輸所需的地址

●Address_1 = Start_Address .

使用如下公式確定猝發中首次傳輸后任何傳輸所需的地址

●Address_N = Aligned_Address+(N–1) x Number_Bytes.

對于循回猝發方式,Wrap_Boundary這個變量用于記錄循回的邊界:

●Wrap_Boundary =(INT (Start_Address /( Number_Bytesx Burst_Length)))

x(Number_Bytesx Burst_Length).

如果Address_N = Wrap_Boundary +(Number_Bytesx Burst_Length),使用以下公式:

●Address_N = Wrap_Boundary .

計算完循回邊界后使用如下公式:

●Address_N = Start_Address +((N–1)x Number_Bytes) - ( Number_Bytesx Burst_Length).

通過使用以下方程可以確定一次猝發中,哪個字節通道用于首次傳輸

●Lower_Byte_Lane=Start_Address-(INT(Start_Address/ Data_Bus_Bytes))

x Data_Bus_Bytes

●Upper_Byte_Lane=Aligned_Address+(Number_Bytes-1)-(INT ( Start_Address / Data_Bus_Bytes)) x Data_Bus_Bytes.

使用如下公式可以確定一次猝發中,首次傳輸之后,所有傳輸都使用了哪些字節通道

●Lower_Byte_Lane= Address_N –(INT ( Address_N / Data_Bus_Bytes)) x Data_Bus_Bytes

●Upper_Byte_Lane= Lower_Byte_Lane+ Number_Bytes–1.

傳輸的數據公式如下:

●DATA[(8xUpper_Byte_Lane)+7:(8xLower_Byte_Lane)].

-

AXI4

+關注

關注

0文章

20瀏覽量

8880 -

axi協議

+關注

關注

0文章

8瀏覽量

2125

原文標題:?AXI總線詳解-AXI4讀寫操作時序及AXI4猝發地址及選擇

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

看看在SpinalHDL中AXI4總線互聯IP的設計

看看Axi4寫通道decoder的設計

一文詳解ZYNQ中的DMA與AXI4總線

ZYNQ中DMA與AXI4總線

深入AXI4總線一握手機制

AXI4 、 AXI4-Lite 、AXI4-Stream接口

使用AXI4總線實現視頻輸入輸出

AXI3與AXI4寫響應的依賴區別?

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協議的基本介紹

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

AMBA AXI4接口協議概述

AXI4讀寫操作時序及AXI4猝發地址及選擇

AXI4讀寫操作時序及AXI4猝發地址及選擇

評論