在每屆的全國大學(xué)生電子設(shè)計(jì)競賽中,DDS作為信號源、以及通信里面本振、波形合成的基本方式,幾乎成了必考的技能,雖然考察的角度不同,但核心都是一個(gè) - 通過數(shù)字的方式得到你需要的某種頻率的某種幅度的某種波形。

在測試測量領(lǐng)域有另一個(gè)概念 - AWG(任意波形發(fā)生器)是跟DDS緊密相關(guān)的,波形發(fā)生器未必一定采用DDS的方式,但“任意”波形的產(chǎn)生就離不開DDS了。

DDS可以生成任意波形 - 比如心狀波形

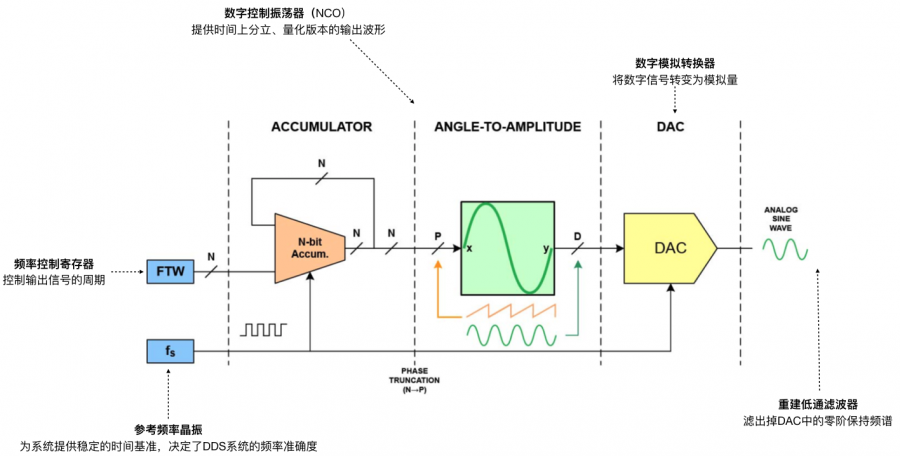

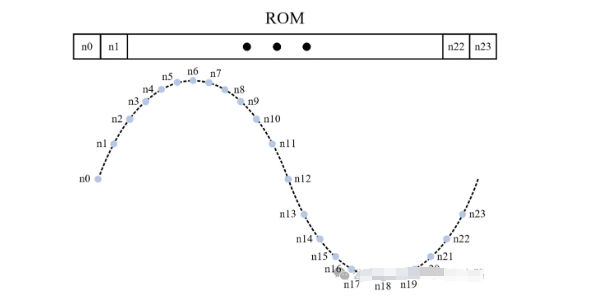

DDS的基本原理如下面的框圖,主要由以下幾個(gè)部分構(gòu)成:

相位累加器 - 改變累加器的步進(jìn)值,也就可以改變輸出信號的頻率;

存儲的波形表 - 決定了你要產(chǎn)生的波形的形狀,其深度和位數(shù)影響了輸出信號的性能;

高速DAC -將數(shù)字的波形轉(zhuǎn)換為模擬的電信號,其分辨率位數(shù)和轉(zhuǎn)換率影響了能夠產(chǎn)生的電信號的最高頻率和信噪比、SFDR等參數(shù)

在DAC后面還有模擬調(diào)理電路 - 對生成的信號進(jìn)行幅度調(diào)節(jié)和頻率分量的篩選

DDS的構(gòu)成

ADI公司有多種針對不同應(yīng)用的DDS器件,其性能指標(biāo)也不一樣,由MCU通過SPI端口對DDS芯片進(jìn)行編程即可得到你需要的波形、頻率、幅度等。經(jīng)典的器件AD9850、AD9833/37、AD9102等。

在具體的使用中僅一顆器件是不夠的,也還是要需要設(shè)計(jì)專門的PCB來完成系統(tǒng)的功能- MCU + DDS +模擬鏈路+電源,一套下來,無論從制作成本還是調(diào)試的時(shí)間上都不見得是比較經(jīng)濟(jì)的方式,使用現(xiàn)成芯片也只能在其能力范圍內(nèi),靈活性不高,用一顆器件應(yīng)對不同可能的考題,是很難的。

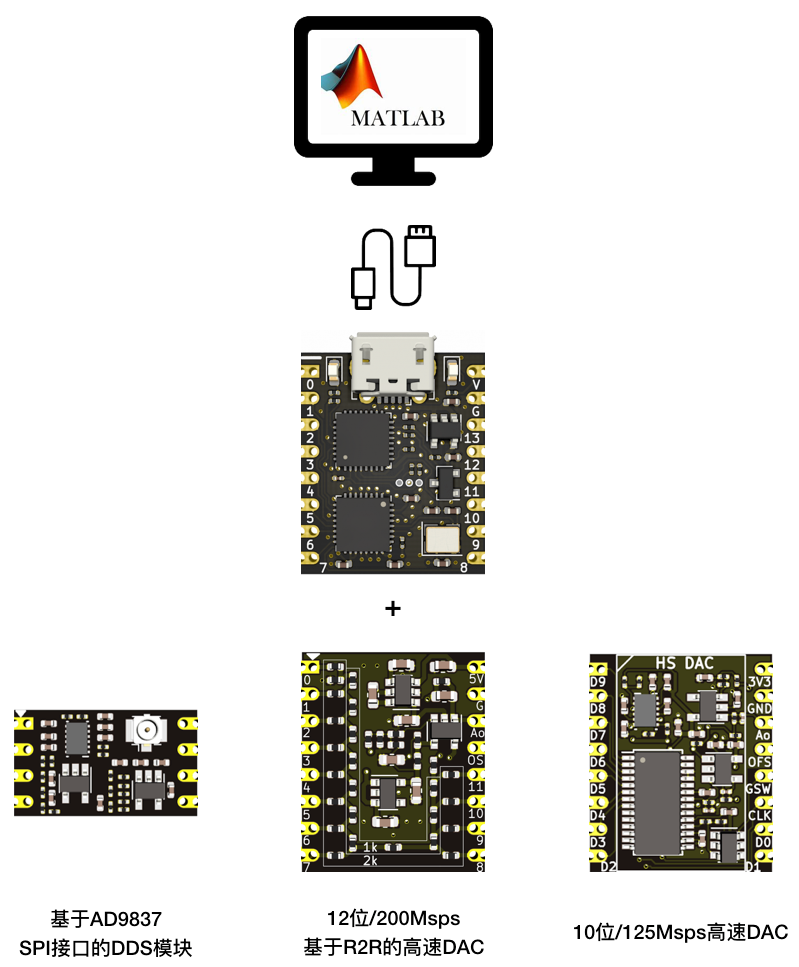

最佳的方式自然是使用FPGA + DAC + 模擬鏈路的方式來實(shí)現(xiàn)。

用FPGA來實(shí)現(xiàn)所有的數(shù)字邏輯和存儲功能

注:除了上圖中的功能,按鍵輸入控制和參數(shù)的輸出顯示乃至菜單,也都可以通過FPGA來實(shí)現(xiàn)

只要你了解FPGA的使用,理解了DDS的工作原理,通過非常簡單的Verilog編程,就可以靈活地實(shí)現(xiàn)各種你需要的功能和性能。

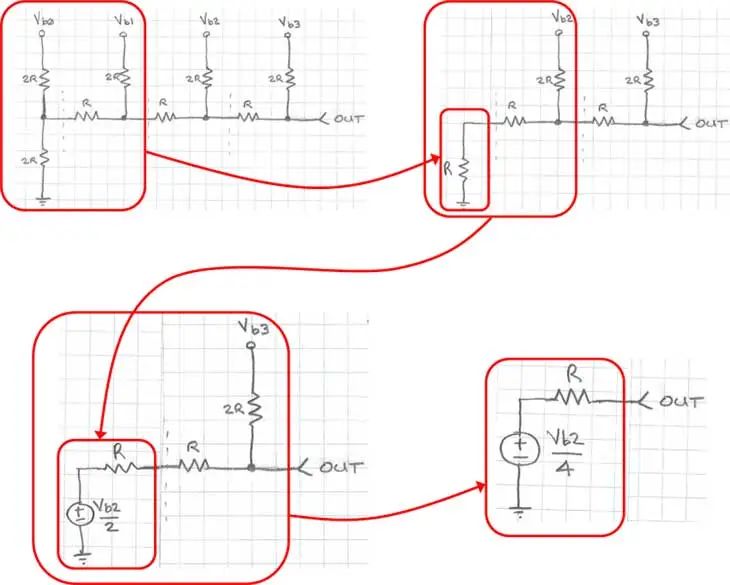

能夠?qū)崿F(xiàn)DDS功能,對于FPGA內(nèi)部資源的要求其實(shí)很小,只需要非常少的邏輯資源和有限的內(nèi)部存儲器就可以實(shí)現(xiàn),一顆十幾塊RMB的FPGA只需要其不到1/5的資源就能夠?qū)崿F(xiàn),而高速的DAC也非常便宜,尤其是采用R-2R的構(gòu)成方式,20個(gè)電阻就可以構(gòu)成10位/200Msps的高速DAC,這種方式生成的波形性能雖然相比商用的高速DAC(比如AD9740)有一定的降低,但足以滿足電賽的需求。

R-2R DAC的工作原理

隨著國產(chǎn)化器件的高速發(fā)展,使用國產(chǎn)的價(jià)廉物美的高速DAC也可以用來做DDS信號發(fā)生器。比如我們硬禾學(xué)堂剛剛驗(yàn)證過的3Peak公司的3PD5651,就是跟AD9740兼容的10位/125Msps的高速DAC,我們用它做成的高速DAC模塊,實(shí)測轉(zhuǎn)換率能夠高達(dá)200Msps無壓力。

當(dāng)然,無論你使用FPGA + R2R還是FPGA + DAC,都需要你來設(shè)計(jì)PCB才能實(shí)現(xiàn),如果實(shí)現(xiàn)高達(dá)100Msps的轉(zhuǎn)換率,對PCB的設(shè)計(jì)能力也是有要求的。為了方便參加電賽的同學(xué)們在不需要制作PCB的情況下也能方便使用DDS,我們硬禾學(xué)堂專門制作了半成品的16管腳的模塊 - FPGA最小系統(tǒng)模塊、R2R高速DAC模塊、基于AD9740的200Msps的高速DAC模塊以及基于3PD5651的125Msps的模塊。只要將FPGA模塊和DAC模塊簡單地連接在一起,就可以方便地實(shí)現(xiàn)DDS的功能。

通過DDS生成的47KHz的正弦波

如果你嫌兩個(gè)模塊焊接都覺得麻煩,也可以使用下面的一體化的模塊,可以通過USB端口對其供電和編程、UART通信,通過邏輯控制其中的參數(shù),或由上位機(jī)通過UART對FPGA的邏輯進(jìn)行參數(shù)配置。

用FPGA + R2R DAC構(gòu)成的高速DDS AWG系統(tǒng)

是不是很方便?

下面我簡單講一下DDS的實(shí)現(xiàn)邏輯:

1 首先將你要實(shí)現(xiàn)的波形的一個(gè)周期的量化數(shù)據(jù)存放在FPGA內(nèi)部的邏輯寄存器或塊狀RAM中,下面的代碼就是存放一個(gè)64個(gè)10位數(shù)據(jù)來表征1/4周期正弦波的代碼,由于正弦波4個(gè)象限的對稱性,只需要1/4周期的數(shù)據(jù)即可,這樣可以只使用1/4的邏輯或存儲資源。

module lookup_tables(phase, sin_out);input [7:0] phase;output [9:0] sin_out; wire [9:0] sin_out; reg [5:0] address;wire [1:0] sel;wire [8:0] sine_table_out; reg [9:0] sine_onecycle_amp; //assign sin_out = {4'b0, sine_onecycle_amp[9:4]} + 9'hff; // 可以調(diào)節(jié)輸出信號的幅度assign sin_out = sine_onecycle_amp[9:0]; assign sel = phase[7:6]; sin_table u_sin_table(address,sine_table_out); always @(sel or sine_table_out)begin case(sel) 2'b00: begin sine_onecycle_amp = 9'h1ff + sine_table_out[8:0]; address = phase[5:0]; end 2'b01: begin sine_onecycle_amp = 9'h1ff + sine_table_out[8:0]; address = ~phase[5:0]; end 2'b10: begin sine_onecycle_amp = 9'h1ff - sine_table_out[8:0]; address = phase[5:0]; end 2'b11: begin sine_onecycle_amp = 9'h1ff - sine_table_out[8:0]; address = ~ phase[5:0]; end endcaseend endmodule 1/4周期正弦波的波表代碼: module sin_table(address,sin);output [8:0] sin; //實(shí)際波形表為9位分辨率(1/4周期)input [5:0] address; //64個(gè)點(diǎn)來生成1/4個(gè)周期的波形,完整的一個(gè)周期為256個(gè)點(diǎn) reg [8:0] sin; always @(address) begin case(address) 6'h0: sin=9'h0; 6'h1: sin=9'hC; 6'h2: sin=9'h19; 6'h3: sin=9'h25; 6'h4: sin=9'h32; 6'h5: sin=9'h3E; 6'h6: sin=9'h4B; 6'h7: sin=9'h57; 6'h8: sin=9'h63; 6'h9: sin=9'h70; 6'ha: sin=9'h7C; 6'hb: sin=9'h88; 6'hc: sin=9'h94; 6'hd: sin=9'hA0; 6'he: sin=9'hAC; 6'hf: sin=9'hB8; 6'h10: sin=9'hC3; 6'h11: sin=9'hCF; 6'h12: sin=9'hDA; 6'h13: sin=9'hE6; 6'h14: sin=9'hF1; 6'h15: sin=9'hFC; 6'h16: sin=9'h107; 6'h17: sin=9'h111; 6'h18: sin=9'h11C; 6'h19: sin=9'h126; 6'h1a: sin=9'h130; 6'h1b: sin=9'h13A; 6'h1c: sin=9'h144; 6'h1d: sin=9'h14E; 6'h1e: sin=9'h157; 6'h1f: sin=9'h161; 6'h20: sin=9'h16A; 6'h21: sin=9'h172; 6'h22: sin=9'h17B; 6'h23: sin=9'h183; 6'h24: sin=9'h18B; 6'h25: sin=9'h193; 6'h26: sin=9'h19B; 6'h27: sin=9'h1A2; 6'h28: sin=9'h1A9; 6'h29: sin=9'h1B0; 6'h2a: sin=9'h1B7; 6'h2b: sin=9'h1BD; 6'h2c: sin=9'h1C3; 6'h2d: sin=9'h1C9; 6'h2e: sin=9'h1CE; 6'h2f: sin=9'h1D4; 6'h30: sin=9'h1D9; 6'h31: sin=9'h1DD; 6'h32: sin=9'h1E2; 6'h33: sin=9'h1E6; 6'h34: sin=9'h1E9; 6'h35: sin=9'h1ED; 6'h36: sin=9'h1F0; 6'h37: sin=9'h1F3; 6'h38: sin=9'h1F6; 6'h39: sin=9'h1F8; 6'h3a: sin=9'h1FA; 6'h3b: sin=9'h1FC; 6'h3c: sin=9'h1FD; 6'h3d: sin=9'h1FE; 6'h3e: sin=9'h1FF; 6'h3f: sin=9'h1FF; endcase endendmodule

2 用查找表的方式尋址一個(gè)波形的整個(gè)周期, phase(相位)即為波表的256個(gè)地址,sin_out為10位的數(shù)據(jù)輸出:

module lookup_tables(phase, sin_out);input [7:0] phase;output [9:0] sin_out; wire [9:0] sin_out; reg [5:0] address;wire [1:0] sel;wire [8:0] sine_table_out; reg [9:0] sine_onecycle_amp; //assign sin_out = {4'b0, sine_onecycle_amp[9:4]} + 9'hff; // 可以調(diào)節(jié)輸出信號的幅度assign sin_out = sine_onecycle_amp[9:0]; assign sel = phase[7:6]; sin_table u_sin_table(address,sine_table_out); always @(sel or sine_table_out)begin case(sel) 2'b00: begin sine_onecycle_amp = 9'h1ff + sine_table_out[8:0]; address = phase[5:0]; end 2'b01: begin sine_onecycle_amp = 9'h1ff + sine_table_out[8:0]; address = ~phase[5:0]; end 2'b10: begin sine_onecycle_amp = 9'h1ff - sine_table_out[8:0]; address = phase[5:0]; end 2'b11: begin sine_onecycle_amp = 9'h1ff - sine_table_out[8:0]; address = ~ phase[5:0]; end endcaseend endmodule

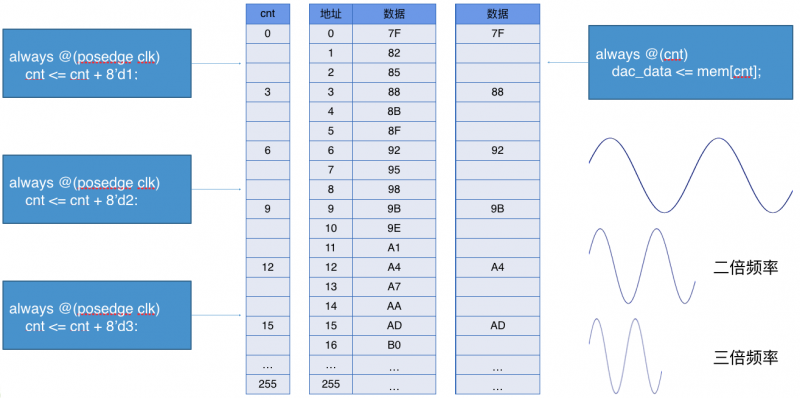

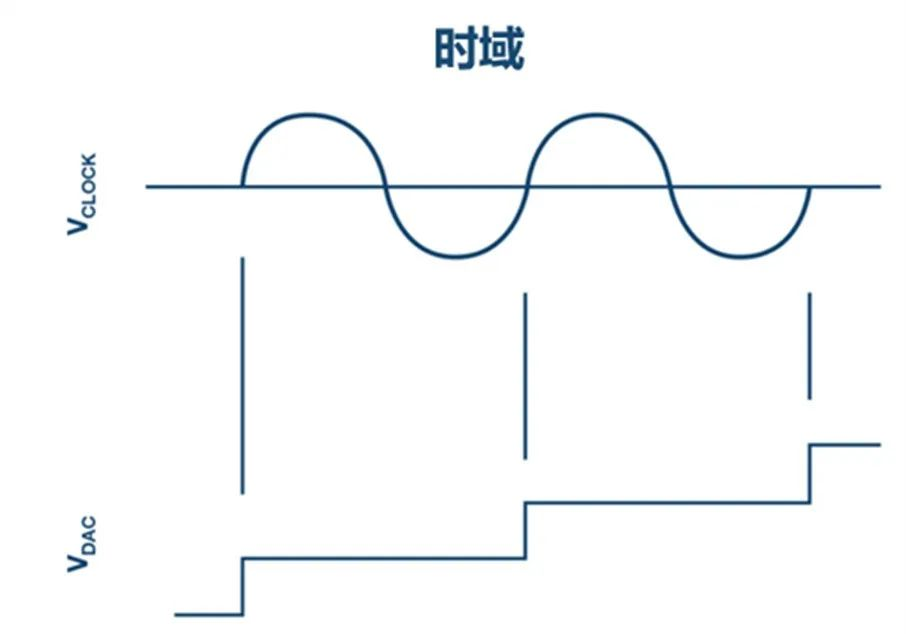

如果使用計(jì)數(shù)器作為地址輸出,逐個(gè)地址的數(shù)據(jù)讀出送給DAC,就可以得到頻率為主時(shí)鐘頻率1/256的正弦波形。要改變輸出頻率,只有改變主時(shí)鐘頻率,這種方法得到“任意”頻率是不可能的,另外對模擬鏈路的輸出濾波器的設(shè)計(jì)也帶來了巨大挑戰(zhàn)。因此這就要下面的一步:

3 通過相位累加器來實(shí)現(xiàn)任意頻率

比如下面的代碼就能夠通過一個(gè)24位的相位累加器,得到頻率最小調(diào)節(jié)精度達(dá)到主時(shí)鐘/2^24~ 主時(shí)鐘/16M,比如主時(shí)鐘為12MHz,則頻率最小調(diào)節(jié)精度可以達(dá)到0.75Hz,相位累加器的值取27962就可以得到頻率為20KHz的正弦波信號。

reg [23:0] phase_acc; // 24位相位累加器always @(posedge clk) phase_acc <= phase_acc + 27962; //在12MHz的主時(shí)鐘時(shí)輸出20KHz頻率的波形lookup_tables u_lookup_table(.phase(phase_acc[23:16]), .sin_out(dac_data));

4 利用內(nèi)部鎖相環(huán)PLL得到高頻率的內(nèi)部時(shí)鐘

無論是MCU還是FPGA,外部的時(shí)鐘源提供的頻率都不會太高,比如我們常用的12MHz的時(shí)鐘,根據(jù)奈奎斯特定律,以及低通濾波器的頻響特性得到的DDS輸出的頻率最高為12MHz * 40%~4.8MHz,如果想得到更高的輸出頻率,比如20MHz的正弦波形,那就需要DDS的主時(shí)鐘高達(dá)50MHz,乃至更高,這樣使得一個(gè)周期內(nèi)的點(diǎn)數(shù)更多,比較理想的狀態(tài)是一個(gè)周期的波形由10個(gè)以上的點(diǎn)構(gòu)成,也就是20MHz的正弦波最好使用200MHz的主時(shí)鐘。那就需要用到PLL,由輸入的低頻時(shí)鐘得到內(nèi)部的高頻時(shí)鐘用于DDS的邏輯和DAC的轉(zhuǎn)換時(shí)鐘。

在我們的系統(tǒng)中,選用了12MHz的輸入頻率,可以通過內(nèi)部PLL得到192MHz(12MHz*16)的內(nèi)部時(shí)鐘頻率,生成20MHz的正弦波毫無壓力。

下面是PLL + 相位累加器的代碼,PLL通過調(diào)用FPGA內(nèi)部的IP核來實(shí)現(xiàn):

wire clk_120m; //內(nèi)部高倍時(shí)鐘的名字cll_120m clk_pll u_clk_pll(.CLKI(clk), .CLKOP(clk_120m)); // 以Lattice的IPCore為例產(chǎn)生高速內(nèi)部時(shí)鐘 // 從12MHz產(chǎn)生120MHz,用以內(nèi)部的邏輯以及DAC轉(zhuǎn)換reg [23:0] phase_acc; // 24位相位累加器 always @(posedge clk_120m) phase_acc <= phase_acc + 2796; //在120MHz的主時(shí)鐘時(shí)輸出20KHz頻率的波形lookup_tables u_lookup_table(.phase(phase_acc[23:16]), .sin_out(dac_data));

有細(xì)心的朋友會問,蘇老師,您的模塊上看不到常規(guī)使用的LC濾波器的影子啊?沒有LPC濾波器如何濾除20MHz以上的混疊、非線性、雜散信號?

其實(shí)我們巧妙地利用了運(yùn)算放大器的GBW和壓擺率的指標(biāo),通過合理選擇運(yùn)算放大器,該放大器自身就能夠?qū)崿F(xiàn)對20MHz以內(nèi)的信號進(jìn)行線性放大,對20MHz以上的信號進(jìn)行衰減的功能。

放大器的選用以及相關(guān)阻、容的值的選擇可以根據(jù)具體的電路拓?fù)漭o之以模擬仿真來實(shí)現(xiàn),由于篇幅限制,這個(gè)在這里不再細(xì)說了。

原文標(biāo)題:高效實(shí)戰(zhàn)及電賽訓(xùn)練(6)- 如何快速制作DDS信號源?

文章出處:【微信公眾號:FPGA入門到精通】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

信號源

+關(guān)注

關(guān)注

5文章

464瀏覽量

44337 -

DDS

+關(guān)注

關(guān)注

21文章

631瀏覽量

152541

原文標(biāo)題:高效實(shí)戰(zhàn)及電賽訓(xùn)練(6)- 如何快速制作DDS信號源?

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

請問DAC38J84內(nèi)部NCO和基帶信號確定性相位關(guān)系如何配置?

dds數(shù)字頻率是怎么合成的 DDS數(shù)字頻率信號發(fā)生器的設(shè)計(jì)

dds輸出頻率與時(shí)鐘的關(guān)系

DAC2902雙通道、高速數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC2900高速數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC904高速數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC908高速數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC900高速數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DDS的基本原理 :相位累加器、存儲的波形表、高速DAC

DDS的基本原理 :相位累加器、存儲的波形表、高速DAC

評論