在很多場合,我們都會看到一個現象:集成芯片的電源端接了一個或多個電容到地。

這種電容叫做退耦電容,也可以叫做濾波電容,這個沒有嚴格的區分。作用是為了去除電源端的的干擾和電源噪聲,很多芯片對電源的要求是很高的,如果你電源端都是不穩定的或者帶來了額外的噪聲,那芯片的功能務必會受到很大的影響。

那我們在設計電路的時候該怎么選取濾波電容呢?

原理

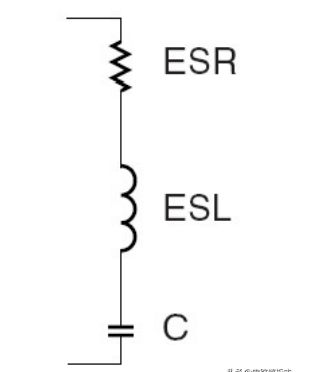

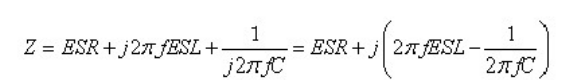

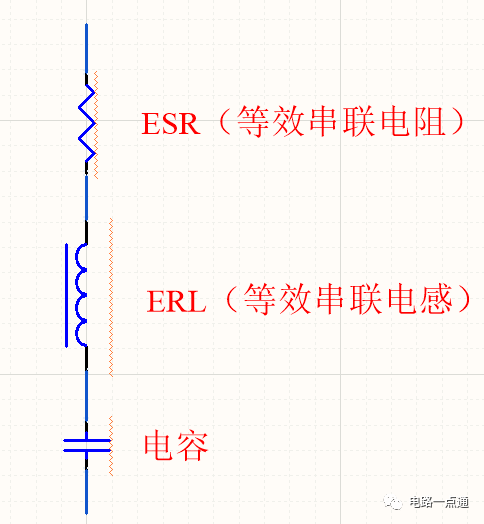

我們實際用的電容并不是理想的電容,我們用到的電容可以用上圖的模型來代替:電阻(ESR)、電感(ESL)和電容C串聯的電路形式。這樣我們就可以得出一個電容的實際阻抗表達式:

Z(阻抗):Z=R(電阻)+jX(電抗)

X=wL-1/wC

XL=JwL

XC=1/jwC

下面,我們分兩種情況來討論下這個看上去比較復雜的表達式

1.高頻(w很大)時,容抗(1/jwC)就趨近于0,但是感抗jwL會很大,這就導致了電容在高頻的時候不再是電容了,它相當于一個電阻和一個很大的電感的串聯,這樣就會產生很大的阻抗Z,會對我們的高頻信號產生很大的阻擋,高頻信號就會被阻擋在外面過不去。

這時候我們得想個辦法,如何能讓高頻信號過去呢?我們仔細看我們的Z阻抗表達式,我們發現高頻信號過不去最主要的原因就是電感這個哥們太調皮了,竟敢一個人擋著我們的去路。所以,我們得叫一個幫手來幫助我們抵抗電感。我們將感抗(1/jwC)增大,因為它與感抗是一個減法關系(死對頭)。感抗一增大,(jwL-j/wC)就會減小,Z就會減小。我們的高頻信號就可以比較輕松的通過了。我們如何來增大感抗?減小C,j/wC就會增大。這樣,我們就可以得出一個結論:小電容可以讓我們的高頻信號更輕松的通過!所以,在電源濾波中,小電容是用來濾除高頻信號的。為什么說是濾除?因為高頻信號都從電容上流向大地了,這樣高頻信號就不會對我的電源造成干擾,就可以成功地讓電源保持穩定。

2.低頻時(w較小時),感抗(jwL)就會變得很小,此時1/jwC就會變得很大,同樣,它也造成了我們的阻抗Z變得很大,我們的低頻信號就被阻擋了。分析方法同1是類似的,我們的目的就是減小阻抗,盡量讓Z=ESR。這里與上面稍微有點不同,看感抗的表達式(XL=jwL),我們不能對它做什么,L是與工藝有關的,是一個固定的值。所以此時,我們就要去減小容(j/wC)。增大C,C就是你電容的值,它是可以改變的。所以,我們得出結論:大電容可以讓低頻信號更輕松地通過!所以,大電容濾除低頻。

由于我們的電源是直流電(w=0),由于容抗j/wC會變得無窮大,所以直流電就通過不了電容,就可以穩穩當當地供給我們的芯片了。在實際應用中,為了由更好的頻率范圍,我們會用一個大電容和小電容并聯的組合(兩者之間的數量級一般至少是100以上)。

電容取值

每種電容都有自己的V型曲線(不同的濾波范圍),有興趣的朋友可以去看一下V型曲線。

下圖是電容取值的參考值:

我剛開始的時候,也不懂為什么電容要這么取,我問過很多人,他們多說這是經驗,你多試試,達不到你要求,你就換電容嘛!我想說的是,實踐才是檢驗真理的唯一標準!

-

濾波電容

+關注

關注

8文章

457瀏覽量

39987 -

設計電路

+關注

關注

1文章

13瀏覽量

4093

發布評論請先 登錄

相關推薦

關于電路中旁路電容的濾波選取

詳細解析電源濾波電容的選取與計算

濾波電容的選取選用原則

電源濾波電容選取詳解

電源濾波電容如何選取資料下載

設計電路時怎么選取濾波電容?

設計電路時怎么選取濾波電容?

評論