過去幾十年,在摩爾定律的指導下,芯片中的晶體管數量大約每兩年翻一番。晶體管的微縮技術革新增加了晶體管的密度。摩爾定律在20世紀60年代首次被發現,并一直延續到2010年代,至此以后,晶體管密度的發展開始放緩。如今,主流芯片包含了數十億個晶體管,但如果摩爾定律能夠繼續按照當時的速度發展下去,它們的晶體管數量將是現在的15倍。

每一代晶體管密度的增加,被稱為“節點”。每個節點對應于晶體管的大小(以長度表示),允許晶體管密度相對于前一個節點增加一倍。晶圓廠在2019年開始“風險生產”,即進行最新的5納米節點(“nm”)的實驗生產,預計在2020年實現量產,之前領先的節點是7納米和10納米。

伴隨著摩爾定律衍生出來的是,由于較小的晶體管通常比較大的晶體管消耗更少的功率,所以隨著晶體管密度的增加,單位芯片面積的功耗保持恒定。但是,晶體管的功耗降低速度在2007年左右有所放緩。

效率和速度的改進

遵循著摩爾定律的發展,自1960年代以來,CPU速度已大大提高。較大的晶體管密度主要通過“頻率縮放”來提高速度,即,晶體管在1和0之間切換更快,以允許給定執行單元在每秒內進行更多計算。由于較小的晶體管比較大的晶體管消耗的功率少,因此可以在不增加總功耗的情況下,提高晶體管的開關速度。自1979年以來晶體管在密度,速度和效率方面的提高。

從1978年到1986年,頻率變化每年使速度增加22%。然后,從1986年到2003年,由于頻率擴展和設計的改進,使得并行計算得以實現,此時,計算速度以每年52%的速度增長。但隨著頻率擴展變慢,多核設計支持的并行性在2003年到2011年之間只能提供23%的年加速。利用可用CPU并行度的最后剩余部分,在2011年到2015年之間帶來了12%的年提速,之后CPU速度的增長速度放緩至每年僅增加3%。

效率也大大提高了由于晶體管尺寸的減小降低了每個晶體管的功耗,在2000年之前,芯片峰值使用期間的整體CPU效率每1.57年翻一番。從那以后,由于晶體管功率降低的速度減慢,效率每2.6年才提高一倍,相當于每年僅提高30%的效率。

隨著晶體管的縮小和密度的增加,使得新的芯片設計成為可能,同時,也進一步提高了效率和速度。首先,CPU可以針對不同功能,優化的更多不同類型的執行單元。其次,更多的片內存儲器可以減少對訪問較慢的片外存儲器的需要。諸如DRAM芯片之類的存儲芯片同樣可以集成更多的內存。第三,與串行計算的體系架構相比,CPU可以為實現并行計算提供更多的空間。同時,如果增加晶體管密度可以使CPU更小,那么一個設備當中就可以包含多個CPU(也稱為多個“核”),而每個CPU可以同時運行不同的計算。

在20世紀90年代,因為芯片設計公司很難通過快速增加晶體管的可用性來開發設計可能性,因而,設計改進往往落后于晶體管密度的改進。為了克服這一瓶頸,設計公司相對更關注相對落后的節點,將大量芯片設計的制造工作外包給國外的低薪工程師,重復使用以前設計的部分(“IP核心”),并使用EDA軟件將高級抽象設計轉化為具體的晶體管級設計。

晶體管設計已達到基本尺寸限制

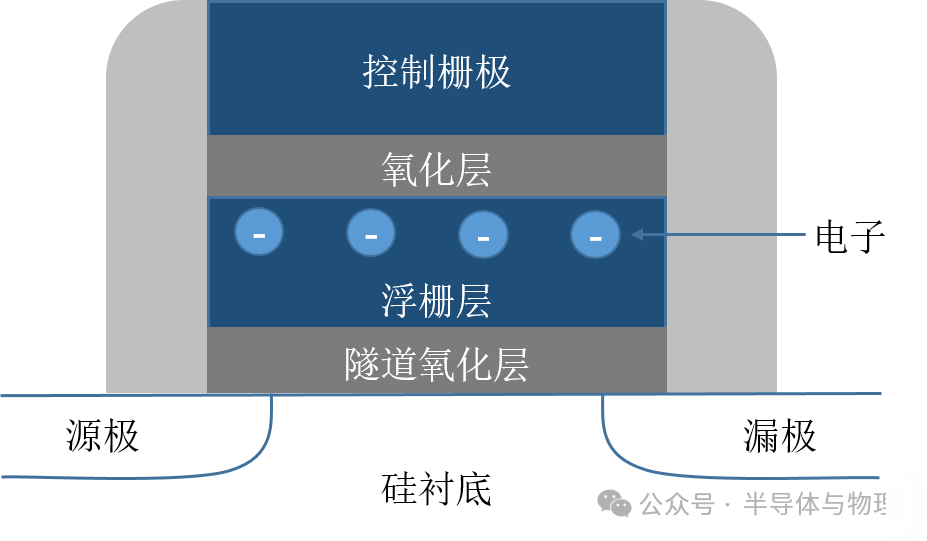

晶體管微縮到只有幾個原子厚的尺寸,它們正迅速接近物理極限。適用于小尺寸的物理問題也使得晶體管在進行進一步的收縮時更具挑戰性。第一個重大變化出現在21世紀初,當時晶體管的絕緣層變得非常薄,以至于電流開始從絕緣層上漏出。對此,工程師使用了更多的新型絕緣材料,即使其他組件繼續收縮,絕緣層也不再收縮。

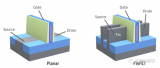

而后,晶體管又進行了更劇烈的結構變化。從20世紀60年代到2011年,晶體管都是一層一層疊放在一起制造的。然而,即使是更絕緣的材料也不能防止漏電。因此,工程師將更復雜的三維結構代替了這種平面布置。從2011年發布的22nm節點到當前的5 nm節點,這種新結構一直占據主導地位。但是,由5nm繼續向下發展時,即使這種結構也會出現漏電的情況。因此,工程師為未來的3nm節點開發了一種全新的結構。它是由幾個原子組成的,進一步減小了晶體管的厚度,使得先進工藝向3nm發展成為了可能。

今天,CPU的不斷進步和領先于專用芯片的趨勢正在走向終結。技術難題正在以比半導體市場增長更快的速度增加摩爾定律改進的成本。最終,這些經濟和技術因素表明,實際晶體管密度將進一步落后于摩爾定律所預測的水平,并且我們可能會面臨晶體管密度沒有進一步得到顯著改善的挑戰。

晶體管開關速度的不斷提高和晶體管功耗的降低使CPU優于專用芯片。在通用芯片占主導地位的時代,專用芯片無法產生足夠的銷售量來彌補高昂的設計成本。專用芯片的成本高昂,是因為專用芯片從設計上就是在針對CPU的特定任務進行改進。當快速的頻率縮放仍可帶來巨大的速度和效率優勢時,專用CPU的運算能力很快就被下一代CPU所抵消,下一代CPU的成本分散在數百萬個芯片的銷售中。如今,摩爾定律的放慢意味著CPU不能再像以前那樣進行迅速迭代。在這種情況下,專用芯片的使用壽命得以延長,使其更具經濟效益。

成本的增長速度快于半導體市場

在細節上的技術困難不斷增加,推高了整個供應鏈的高端半導體研發成本。半導體行業的不同行業基于各自的優勢,在不同的地區進行實現了本地化。

價值最高的行業,尤其是SEM、晶圓廠和芯片設計行業,其成本增長和整合的速度特別快。半導體制造設備成本(11%)和每個芯片的設計成本(24%)的年增長率都高于半導體市場(7%)。而半導體研發人員的數量則又以每年7%的速度增長。

自本世紀初以來,半導體制造成本(包括晶圓廠和SEM)的年增長率一直保持在11%。固定成本的增長速度快于可變成本,這造成了更高的壁壘,擠壓了晶圓廠的利潤,并導致致力于先進節點的晶圓廠代工廠數量的正在減少。圖2顯示臺積電(TSMC)在晶圓廠的建造上投入的成本增加最大。目前,在5納米節點上只有兩家芯片制造商:臺灣的臺積電(TSMC)和韓國的三星(Samsung)。英特爾緊隨其后,計劃推出7和5納米節點;GlobalFoundries和中芯國際(SMIC)則推出了14納米。

***是眾多半導體設備當中最昂貴和最復雜的部分,其成本已從1979年的45萬美元/件上升到2019年的1.23億美元/件。目前只有荷蘭的ASML光刻公司能夠制造最小5納米晶體管的光刻設備。除此之外,尼康在日本是唯一可生產大量的***的企業,其出售的設備使用于≤90納米的制程工藝上。最終,在先進節點上增加光刻設備和晶圓廠的研發成本的企業,可以從緩慢增長的全球半導體市場收回成本。

同時,多項估計表明芯片設計成本呈指數級上升。當與臺積電的節點引入日期相匹配時,根據國際商業策略(IBS),每個節點的設計成本每年增加24%。由于它們的通用用途,CPU具有規模經濟優勢,使美國公司Intel和AMD能夠在服務器和臺式機和筆記本電腦等個人電腦(PC)的CPU設計方面保持長達數十年的雙寡頭壟斷地位。

隨著半導體復雜性的增加,對高端人才的需求推動了設計和制造成本的超支。通過將半導體研發支出除以高技能工人的工資來衡量,研究人員的有效人數從1971年到2015年增長了18倍。換言之,摩爾定律要求2015年的人類研究工作量是1971年的18倍,每年增長7%。

每個晶體管的總體設計和制造成本可能是衡量晶體管密度改進是否經濟的最佳指標。這個成本在歷史上每年下降了20-30%左右。一些分析師稱,這種下降已經超過了2011年引入的28nm節點,而其他人則不同意。

半導體市場的增長速度已經超過了世界經濟的3%。目前,半導體行業占全球經濟產出的0.5%。部分由于美國和中國之間的貿易戰爭,半導體市場在2019年縮水,然而,它典型地呈現出逐年鋸齒狀的增長軌跡,因此多年的放緩更能表明長期增長的放緩。

每個節點的芯片生產

鑒于芯片生產的技術和經濟挑戰,新節點的引入比過去更慢。摩爾定律的標準承擔者英特爾確實減慢了節點的引入。臺積電在其前任產品推出兩年后推出了32和22 nm節點,這與摩爾定律保持一致,但在22 nm推出三年后又推出了14 nm,而14 nm節點芯片之后又推出了10 nm。然而,領先的代工服務供應商臺積電(TSMC)并沒有放緩節點的推出。

領先的節點芯片銷量的趨勢并不意味著新節點的采用會大幅放緩。從2002年到2016年,臺積電的領先節點穩定地代表了其約20%的收入。2016年和2018年分別引入的臺積電10nm和7nm節點也分別達到了25%和35%,如圖4所示。

臺積電新節點的穩定銷售率(盡管比2000年代初期要慢)可能掩蓋了整個代工服務市場正在減緩采用這一事實。在過去的十年中,臺積電控制了全球約一半的晶圓代工市場份額。生產成本的上升正在減少領先節點的公司數量。例如,在此期間,Global Foundries因無法前進到14 nm以上而退出。如果這種趨勢伴隨著當前領先節點的晶圓廠產能低于以前領先節點的晶圓廠產能,則表明摩爾定律正在放緩。

出于幾個原因,晶圓廠仍然在舊節點上制造芯片。晶圓廠在建造領先晶圓廠或將舊晶圓廠升級為在較新節點制造晶片時,會產生巨大成本,因此不可能立即將世界晶圓廠產能轉移至領先節點。相反,工廠繼續以較低的價格出售舊節點,特別是向以購買成本為主要標準的客戶出售舊節點。其中許多客戶可能不太關心效率,因為他們的應用程序不是計算密集型的。類似地,它們的應用程序可能不需要很快的速度,或者在舊芯片上以足夠快的速度完成計算。此外,一些專門的低容量產品(如模擬芯片)需要后續節點來保持成本效益。

摩爾定律變慢時芯片的改進

隨著摩爾定律(Moore’s Law)的放緩,芯片在兩方面繼續改進:一是更小晶體管的效率和速度的提高,二是利用更小晶體管尺寸所支持的更大數量晶體管的先進芯片設計的效率和速度的提高。這些先進的設計包括在一個芯片上封裝更專業的核心的能力。

幸運的是,一些速度和效率的改進仍然是可用的,但是有相當大的技術挑戰。大約在2004年,當達到65nm節點時,晶體管密度的改善在降低晶體管功耗和提高晶體管開關速度(頻率縮放)方面變慢。盡管如此,晶圓廠報告稱,晶體管級別的創新,而非設計級別的創新,將繼續提供節點與節點之間一致(盡管速度較慢)的改進。

臺積電和三星聲稱,他們的5nm節點芯片在功率保持不變的情況下,其7nm節點芯片的晶體管速度分別提高了15%和10%,而在晶體管速度保持不變的情況下,其功耗降低了30%和20%。臺積電所聲稱的在90nm和5nm之間的恒定效率下的節點到節點晶體管速度改善的下降趨勢,但是在臺積電所聲稱的晶體管功率降低改善的下降趨勢是平緩的。

三星在兩項指標上的數據都在14nm到5nm之間呈下降趨勢,但是我們缺少大于14nm的節點的數據。英特爾發現晶體管的速度略有下降,但從65nm到10nm,節點到節點的晶體管功率降低的改進仍在繼續。英特爾還沒有推出其7nm節點。這些速度和效率的提高既有利于像CPU這樣的通用芯片,也有利于像AI芯片這樣的專用芯片。

芯片設計的改進現在提供了降低CPU效率和速度的改進。按節點合并了CPU和晶體管的速度和效率測量。對于CPU,我們使用圖1中的數據。對于晶體管,我們使用來自圖5和圖6的臺積電和英特爾節點的數據。這些消息來源在速度和效率改進方面大致一致。臺積電和英特爾報告的來自晶體管級創新的改進,通常與來自晶體管級和設計級創新的CPU改進相匹配。粗略的匹配表明,晶體管級的創新在過去15年里一直在CPU效率和速度改進方面發揮著重要作用,至少在經過測量的CPU基準測試中是這樣。然而,高效的設計仍然發揮著作用。

改進的晶體管密度可實現專業化

除了改善晶體管功能外,增加晶體管密度還能使芯片包含更多種類的專用電路,用于執行不同類型的計算。一個芯片可以調用不同的專用電路,這取決于所請求的計算。這些電路可以包括一些優化的AI算法和其他專門針對不同類型的計算。

除了使用這些專用電路外,近年來在通用芯片上增加更多的晶體管幾乎沒有什么好處。從理論上講,更多的晶體管可以使CPU包含更多的電路,從而并行執行更多的計算。然而,并行性的加速通常受到串行計算時間百分比的限制,串行計算一個接一個地執行,因為一個計算的結果需要啟動另一個計算。相反,并行計算是同時進行的。即使只有1%的算法計算時間需要串行計算,也會浪費45%的處理器能量。不幸的是,大多數應用程序至少需要一些串行計算,并且隨著串行化百分比的增加,處理器的能量浪費變得過高。自2000年中期以來,隨著其他設計改進的放緩,擁有越來越多核心的多核設計開始激增。但是多核設計也不能有效地并行化算法,這需要在串行計算上花費大量的時間。

責任編輯:tzh

-

芯片

+關注

關注

454文章

50430瀏覽量

421866 -

cpu

+關注

關注

68文章

10826瀏覽量

211160 -

eda

+關注

關注

71文章

2709瀏覽量

172903 -

晶體管

+關注

關注

77文章

9635瀏覽量

137856

發布評論請先 登錄

相關推薦

3D-NAND浮柵晶體管的結構解析

CMOS晶體管的尺寸規則

NMOS晶體管和PMOS晶體管的區別

CMOS晶體管和MOSFET晶體管的區別

PNP晶體管符號和結構 晶體管測試儀電路圖

晶體管功率繼電器的基本介紹

降壓開關穩壓器如何使用串聯晶體管

什么是達林頓晶體管?達林頓晶體管的基本電路

晶體管Ⅴbe擴散現象是什么?

有什么方法可以提高晶體管的開關速度呢?

晶體管是如何工作的?BJT和MOSFET晶體管區別

晶體管設計已達到基本尺寸限制

晶體管設計已達到基本尺寸限制

評論