Versal? ACAP(自適應(yīng)計(jì)算加速平臺)是高度集成化的多核計(jì)算平臺,可通過靈活的自適應(yīng)能力來滿足不斷變化的動態(tài)算法的需求。VCK190 是賽靈思最早發(fā)布的 Versal AI Core 評估器件之一。

本篇博文將為您詳解如下所述設(shè)計(jì)創(chuàng)建步驟:

1. 在 Vivado 中構(gòu)建基于 Versal 的 IP 集成器 (IP integrator) 設(shè)計(jì)

2. 創(chuàng)建器件鏡像

3. 在 Vitis 中構(gòu)建平臺和系統(tǒng)工程

4. 在 VCK190 評估板上運(yùn)行和調(diào)試應(yīng)用

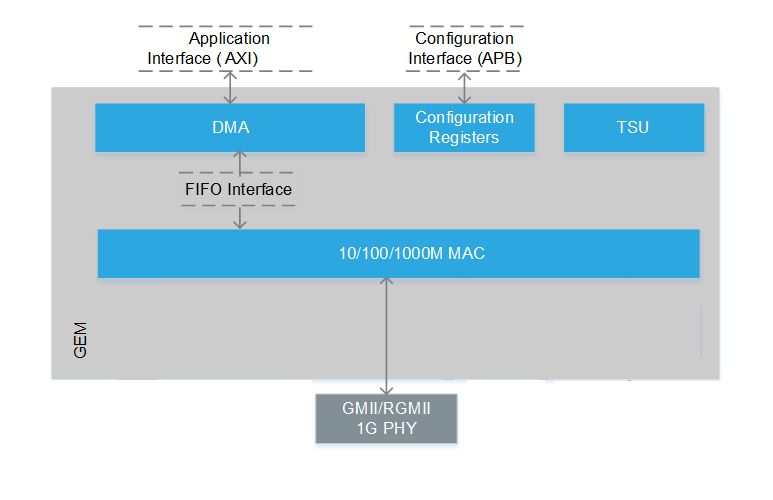

Versal上的PS-GEM

千兆以太網(wǎng) MAC (GEM) 可提供符合 IEEE 802.3-2016 標(biāo)準(zhǔn)的硬核 10/100/1000 Mbps 接口。

在 PS 低功耗域 (LPD) 中有 2 個(gè) GEM 控制器。

每個(gè)控制器均獨(dú)立運(yùn)行,且各含 1 個(gè)管理數(shù)據(jù)輸入/輸出 (MDIO) 接口以供其外部 PHY 配合 RGMII 接口使用。

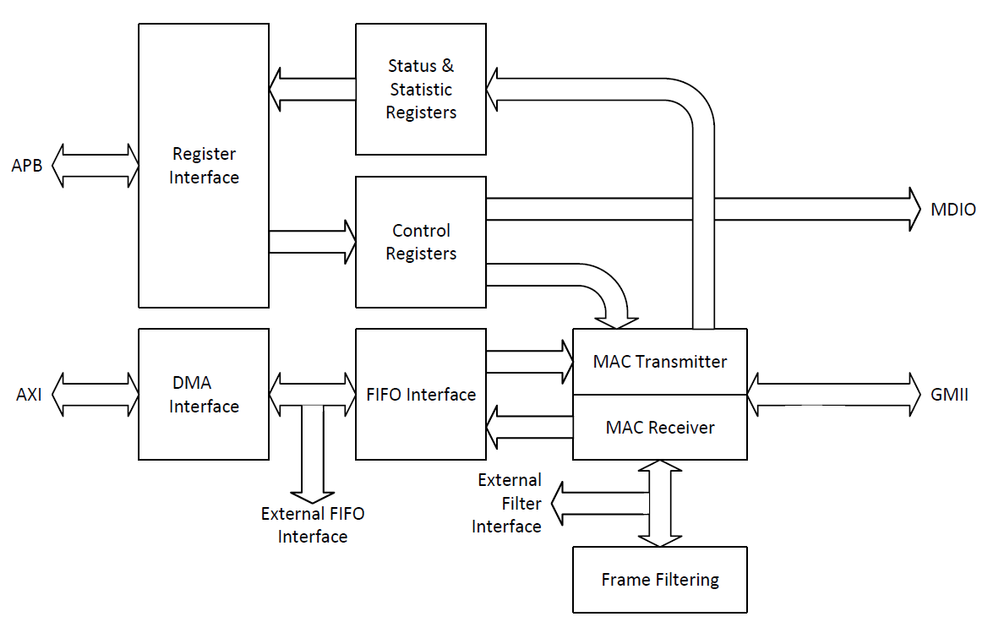

GEM 包含下列組件:

1 個(gè) MAC 用于控制傳輸、接收、地址檢查和環(huán)回

配置寄存器,可提供控制和狀態(tài)寄存器、統(tǒng)計(jì)數(shù)據(jù)寄存器和同步邏輯

1 個(gè)直接內(nèi)存訪問 (Direct Memory Access) 模塊,用于控制 DMA 傳輸和 DMA 接收

1 個(gè)時(shí)間戳單元 (TSU),用于計(jì)算 IEEE 1588 定時(shí)器值,其中包含實(shí)時(shí)時(shí)鐘

在無需 DMA 操作的系統(tǒng)應(yīng)用中,可使用配置選項(xiàng)移除 DMA 模塊,并且可使用外部 FIFO 接口將 GEM 集成到 SoC 環(huán)境中。

GEM 塊包含以下信號接口:

連接到外部 PHY 的 GMII 和 RGMII

1 個(gè)用于外部 PHY 管理的 MDIO 接口

1 個(gè) APB 從接口,用于訪問 GEM 寄存器

1 個(gè)用于內(nèi)存訪問的 AXI4 DMA 主接口

無需 DMA 功能的應(yīng)用內(nèi)包含 1 個(gè)可選 FIFO 接口

1 個(gè)可選時(shí)間戳接口

I/O 選項(xiàng)包括:

布線到 LPD MIO 管腳的 RGMII (v2.0),用于連接到外部 PHY

GMII 和 MII 布線到 PL,以便映射到 GT 或(可選)可借助 PL 邏輯來轉(zhuǎn)換為其它協(xié)議

每個(gè)控制器內(nèi)的診斷內(nèi)部環(huán)回

注:Versal 中不支持內(nèi)部 SERDES 接口 (SGMII)。在 MPSoC 器件中支持此類接口。

在 VCK190 器件上,GEM0 和 GEM1 均硬連線到板上的 2 個(gè)外部 RGMII PHY。

有 2 個(gè) RJ45 端口,分別用于 GEM0 和 GEM1。如要測試 GEM1 RGMII 端口,請確保 GEM0 RGMII 端口同樣通過電纜連接,因?yàn)榇硕丝谑褂霉蚕?MDIO 線(使用 GEM0 MDIO 作為主接口)。

請參閱以下 VCK190 截屏。在右上角有 2 個(gè) RJ45 端口用于 Versal 以太網(wǎng)。

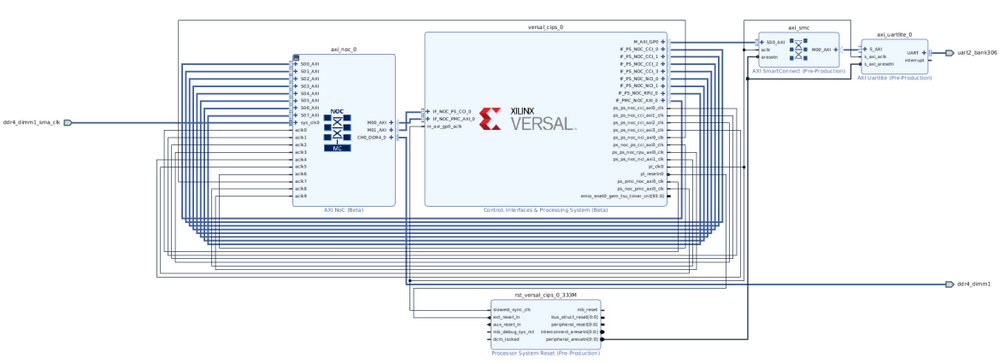

在 Vivado 中創(chuàng)建 IP integrator 設(shè)計(jì)

請下載隨附的 Tcl 文件并遵循以下步驟進(jìn)行操作。

1. 在 Vivado 2019.2 中基于 VCK190 評估板創(chuàng)建工程。

2. 創(chuàng)建塊設(shè)計(jì)。

3. 找到 vck190_1g.tcl。以下是 IP integrator 畫布中的原理圖。

4. 生成 HDL 封裝文件。

5. 單擊“運(yùn)行實(shí)現(xiàn) (Run Implementation)”和“生成器件鏡像 (Generate Device Image)”。

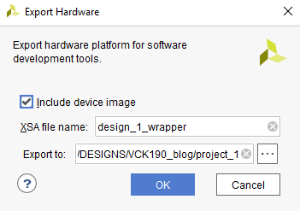

6. 導(dǎo)出包含器件鏡像的硬件設(shè)計(jì)。

注:單獨(dú)使用“運(yùn)行塊自動化設(shè)置功能 (run block automation)”時(shí),CIP 與 NoC 之間部分連接缺失。隨附的 Tcl 文件可用于確保 CIP 和 NoC 中配置設(shè)置正確。

在 Vitis 中構(gòu)建并運(yùn)行 LwIP 應(yīng)用

我們已構(gòu)建了 IP integrator 設(shè)計(jì)并已導(dǎo)出了含器件鏡像的硬件設(shè)計(jì)。現(xiàn)在,我們將在 Vitis 中創(chuàng)建 lwIP 示例,并在 VCK190 評估板上運(yùn)行。

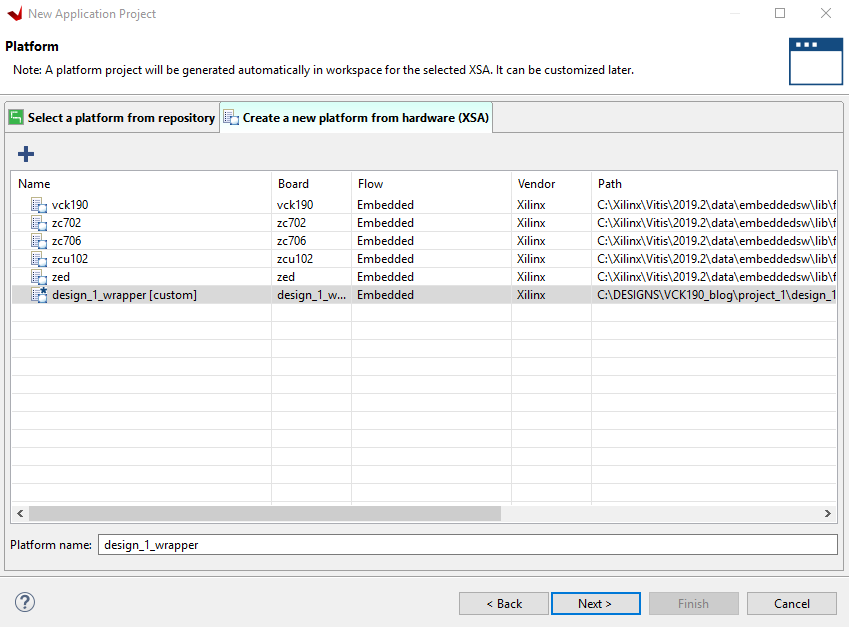

1. 啟動 Vitis。

2. 使用來自以上設(shè)計(jì)的 XSA 文件創(chuàng)建應(yīng)用工程。

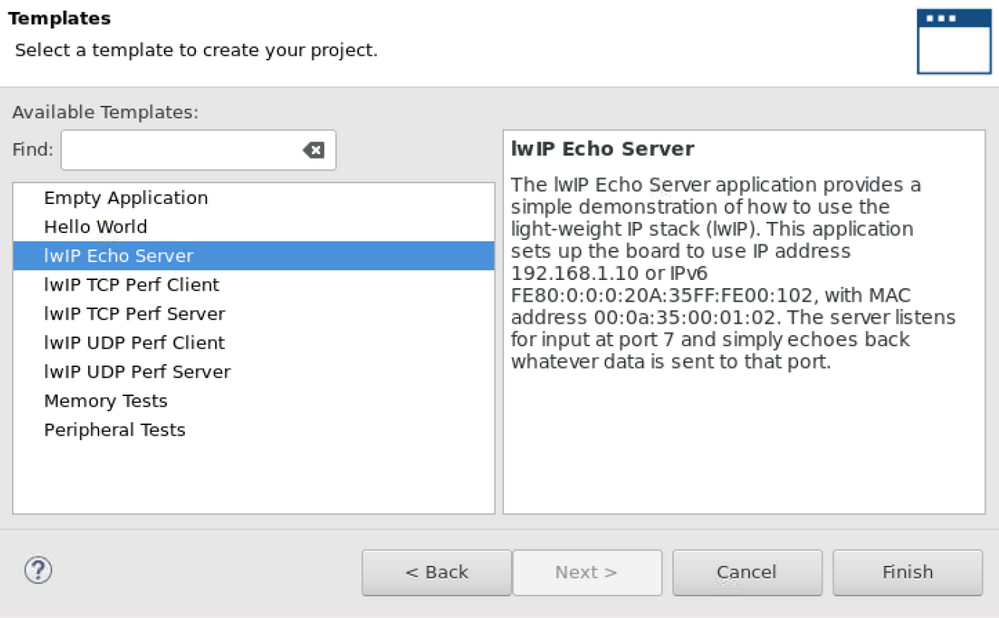

3. 從 SDK 中選擇“l(fā)wIP 響應(yīng)服務(wù)器 (lwIP Echo Server)”。

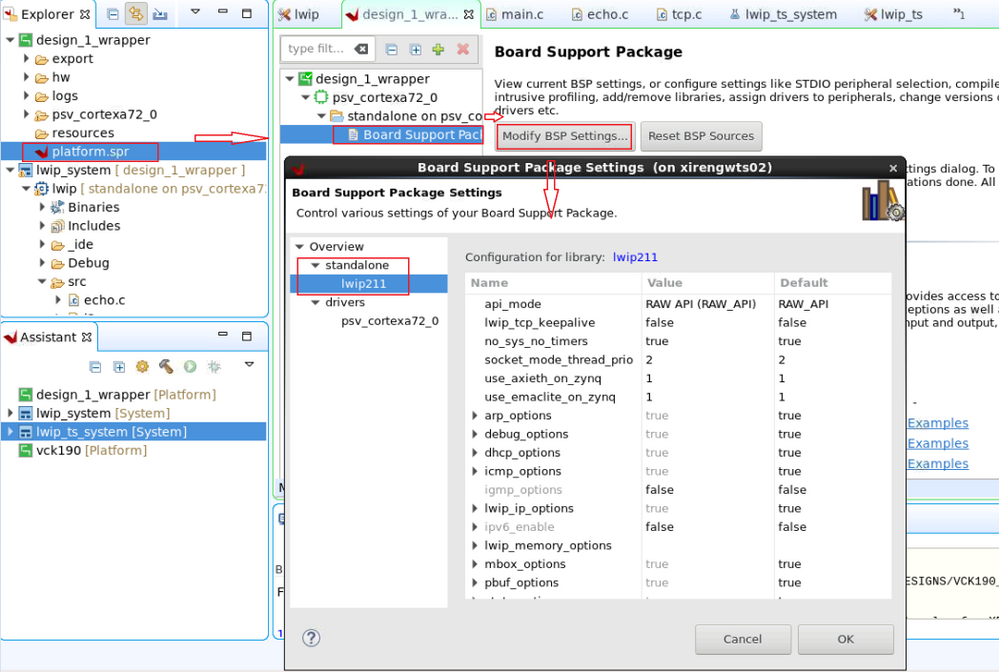

4. 在 SDK 中構(gòu)建平臺和系統(tǒng)工程。選中 lwIP 響應(yīng)服務(wù)器應(yīng)用時(shí),會自動設(shè)置 lwIP 庫的 BSP 設(shè)置。用戶還可以選擇僅創(chuàng)建并構(gòu)建平臺工程,但這樣需手動設(shè)置 BSP 設(shè)置。

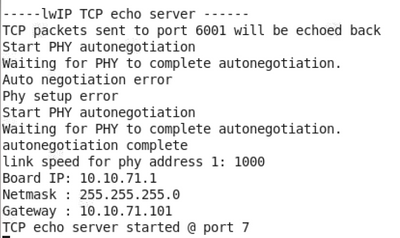

5. 在 VCK190 開發(fā)板上運(yùn)行 lwIP 示例。以下即 UART 控制臺輸出:

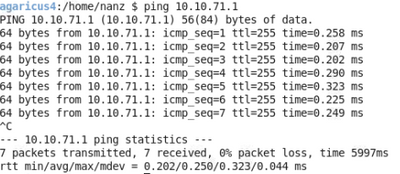

6. 以下是 ping 測試輸出:

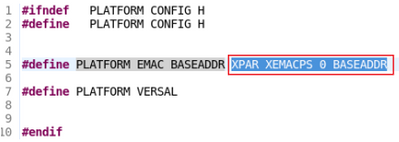

要切換到 GEM1 RJ45 以便進(jìn)行測試,用戶應(yīng)使用 XPAR_XEMACPS_1_BASEADDR 修改 platform_config.h。

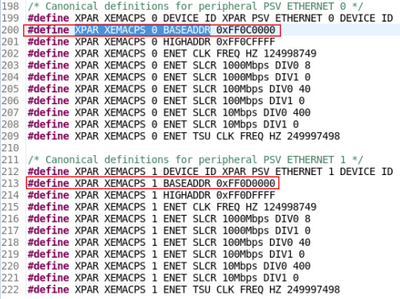

可在 BSP 的 xparameters.h 中找到以太網(wǎng)定義。請參閱以下示例

在 platform_config.h 中,更改以下定義:

將此定義更新為:

#define PLATFORM_EMAC_BASEADDRXPAR_XEMACPS_1_BASEADDR

現(xiàn)在,您可重新構(gòu)建應(yīng)用并重新運(yùn)行測試。

LwIP性能

以下是 lwIP 響應(yīng)服務(wù)器應(yīng)用的 BSP 設(shè)置。

PARAMETER dhcp_does_arp_check = true

PARAMETER lwip_dhcp = true

PARAMETER pbuf_pool_size = 2048

對于 lwIP TCP/UDP 性能服務(wù)器,默認(rèn)將設(shè)置下列參數(shù)。

PARAMETER mem_size = 524288

PARAMETER memp_n_pbuf = 1024

PARAMETER n_tx_descriptors = 512

PARAMETER pbuf_pool_size = 16384

這些 lwIP 參數(shù)對于性能調(diào)優(yōu)至關(guān)重要。

這些參數(shù)可控制所分配和使用的內(nèi)存量以及 Pbuf 和描述符數(shù)量。

如果系統(tǒng)受到限制,無法處理這些包,則 BD 和 Pbuf 將被快速用盡,且無法根據(jù)要求快速清空以供使用。由此導(dǎo)致性能受到影響。

但我們還應(yīng)平衡可使用的內(nèi)存量,以便在用于性能基準(zhǔn)測試的評估板上將這些參數(shù)調(diào)整為適合 1Gbps 的最優(yōu)值。您可以此為參考,根據(jù)自己的要求來對這些參數(shù)進(jìn)行調(diào)優(yōu)。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5250瀏覽量

119179 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

130954 -

算法

+關(guān)注

關(guān)注

23文章

4546瀏覽量

92005 -

Versal

+關(guān)注

關(guān)注

1文章

151瀏覽量

7596

發(fā)布評論請先 登錄

相關(guān)推薦

賽思快訊 | 發(fā)展新質(zhì)生產(chǎn)力問道賽思?賽思如何下好“創(chuàng)新棋”?

安賽思半導(dǎo)體與新加坡三福半導(dǎo)體達(dá)成戰(zhàn)略合作

賽思快訊 | 熱烈歡迎嘉興市政協(xié)一行領(lǐng)導(dǎo)蒞臨賽思總部調(diào)研指導(dǎo)工作!

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺示例設(shè)計(jì)流程

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

AMD收購賽靈思兩周年之際,全新Embedded+進(jìn)一步彰顯協(xié)同效應(yīng)

賽思快訊 | 熱烈歡迎嘉興市人民政府咨詢委員會蒞臨賽思總部調(diào)研!

Versal 自適應(yīng)SoC設(shè)計(jì)指南

易靈思RAM使用--Update3

怎么用eclipse創(chuàng)建web項(xiàng)目

codeblocks怎么創(chuàng)建c文件

基于Vitis AI的ADAS目標(biāo)識別

詳解基于賽靈思的Versal? ACAP設(shè)計(jì)創(chuàng)建步驟

詳解基于賽靈思的Versal? ACAP設(shè)計(jì)創(chuàng)建步驟

評論