對于FPGA開發而言,仿真是開發流程中必不可少的一步,也是非常重要的一步,仿真是將RTL代碼模擬運行,得到module中信號波形,再進行功能分析的過程。強大的功能與速度兼具的modelsim仿真就是你開發過程的最合適的選擇了,下面我以簡單的24進制計數器帶各位熟悉modelsim仿真流程及波形。

一、新建工作庫Library

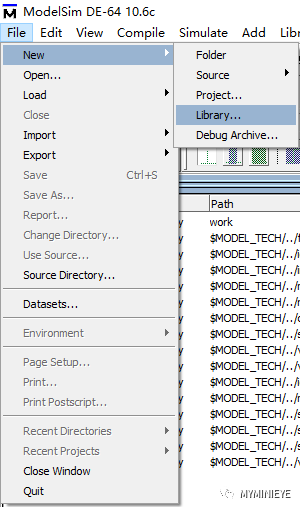

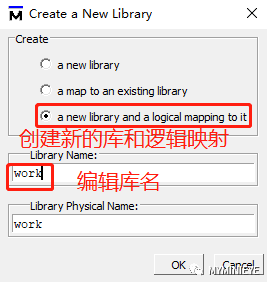

1、點擊File>New>Library

創建新的庫和邏輯映射,編輯庫名,點擊ok確定

如果已經建立過work庫可以跳過該步驟

2、庫的其他功能

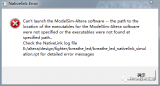

由于modelsim無法識別其他廠商器件的IPcore,所以如果需要用到綜合器對應廠商如Xilinx或Gowin芯片的功能,則需對modelsim添加廠商提供的庫相關文件,并編譯庫,從而達到調用庫的功能,進而對 VIVADO或Gowin軟件進行設置,最后進行聯合仿真。

二、新建工程Project

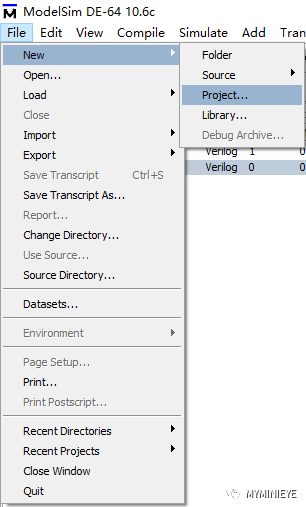

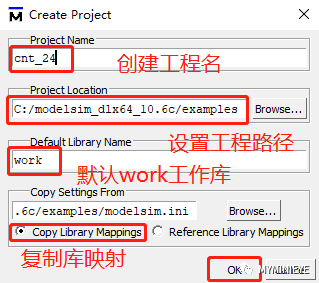

點擊File>New>Project

創建工程名、設置工程路徑、確定默認工作庫

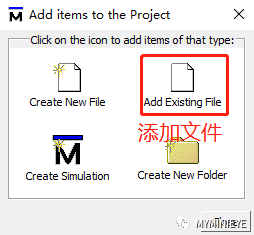

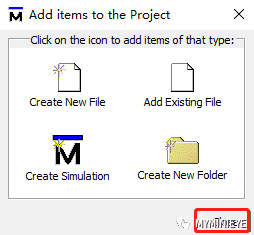

三、添加仿真源文件

仿真源文件包含功能源文件與測試激勵源文件;

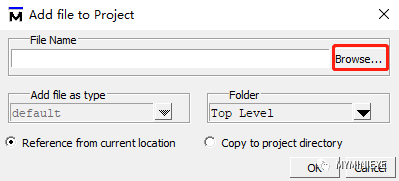

點擊Browse,瀏覽文件

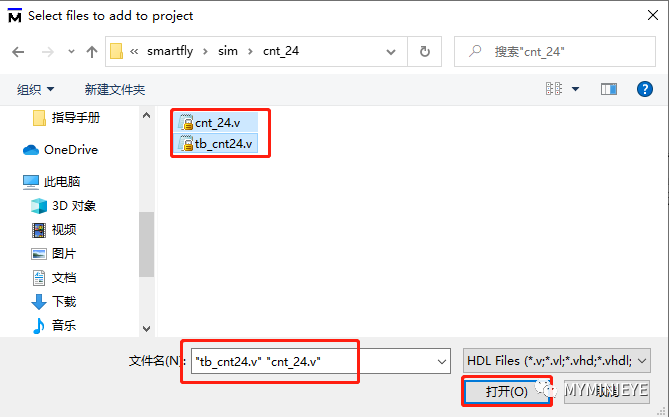

選擇兩個文件并打開

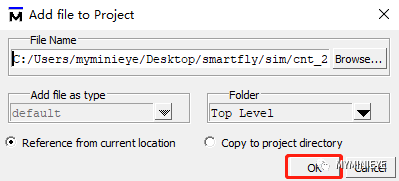

添加文件到工程,點擊OK

點擊close關閉

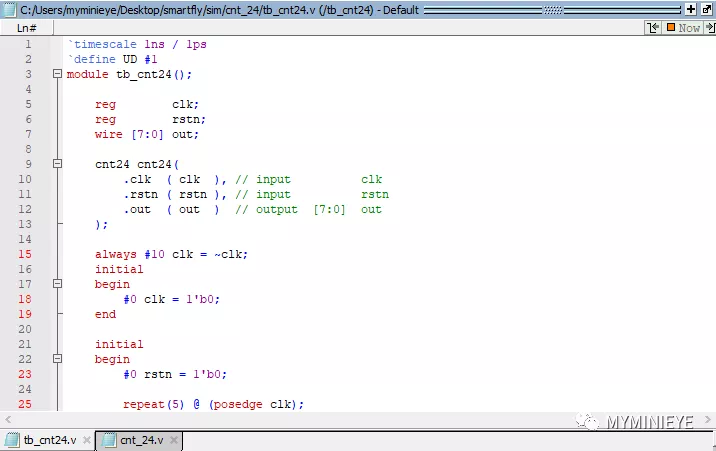

如有不清楚testbench編寫,可以參考myminieye公益課堂系列教程第18集;仿真基礎篇1FPGA_simulation_testbench,

連接:https://www.bilibili.com/video/BV1EE411475Z?p=18

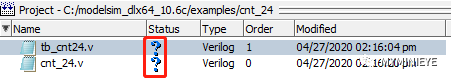

四、仿真源文件編譯

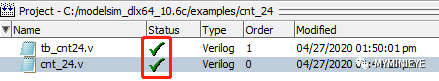

若狀態Status顯示“?”為文件未編譯

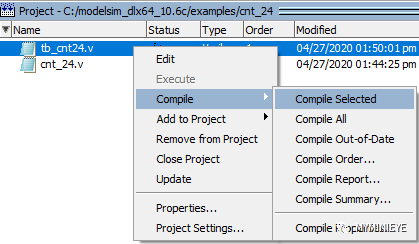

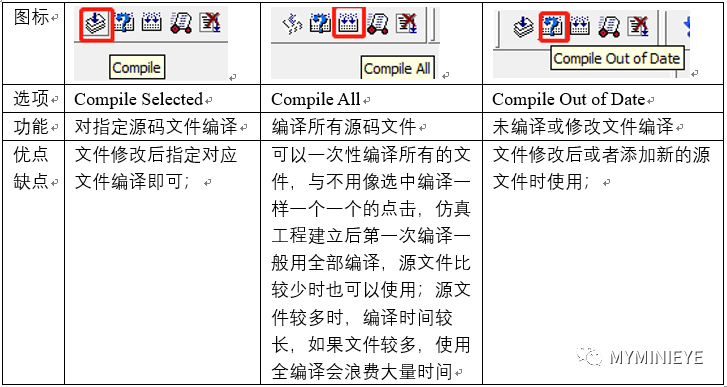

常用有3種編譯方式:編譯選中文件、編譯所有文件、編譯未編譯文件;對應操作方式如下:

菜單欄: 右擊菜單

圖標:

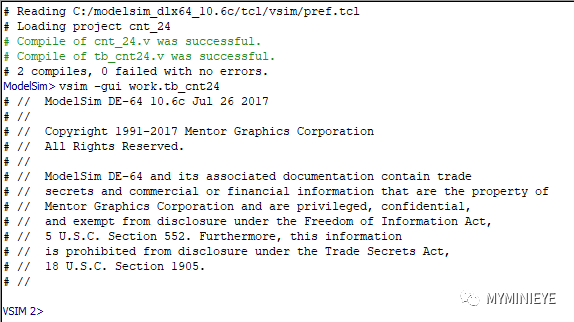

若狀態Status顯示“√”則為編譯成功,也可從下方Transcript看出文件編譯成功

若狀態Status并未顯示“√“,或者下方Transcript顯示編譯不成功,則需修改對應的源文件。

修改后重新編譯,可從Transcript檢查是否有語法錯誤等,直至顯示編譯成功。

五、仿真運行

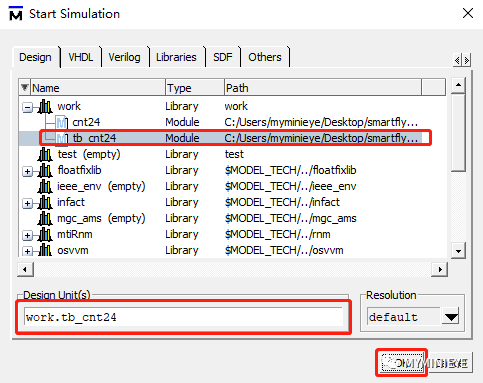

編譯成功后即可運行仿真了;

開始仿真:Simulation>Start Simulation;或者點擊下圖中的小圖標

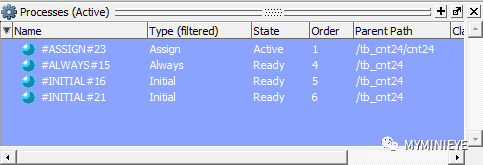

此時記得要選中tb測試激勵文件(testbench文件)進行仿真,點擊ok確定

如果Transcript顯示無報錯則可以進行下一步操作

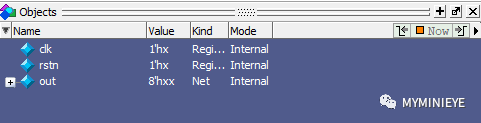

端口類型

激勵類型

2.添加波形文件

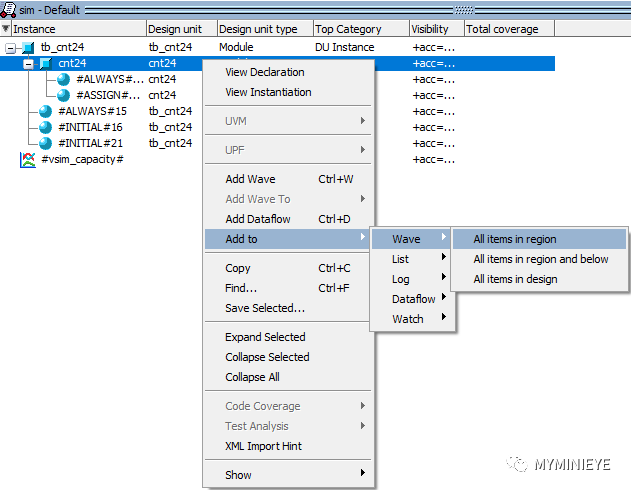

Sim:選擇下圖所示的sim,右鍵點擊選中tb測試文件>addto>wave>all items in region

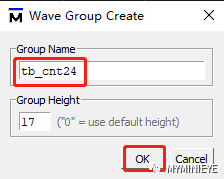

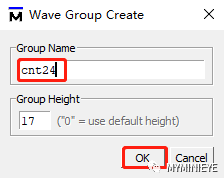

為了便于觀察波形,進行分組并命名,點擊ok確定;

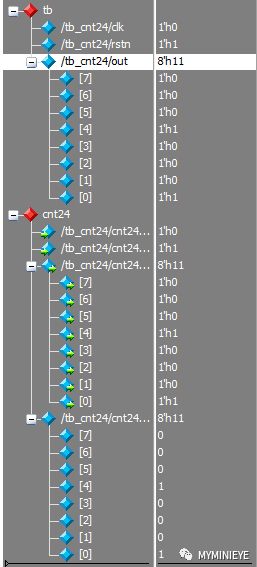

為了與tb測試文件仿真波形進行對比,同理可添加源文件波形;

同樣為了便于觀察波形,進行分組并命名;

信號位置移動方便多個信號同時分析:分組后,可以上下拖拽所需要分析的信號,方便且清晰的上下對比所需波形之間的差異,此時分組的目的就是能與拖拽前后波形信號對比區分,不至于搞混;

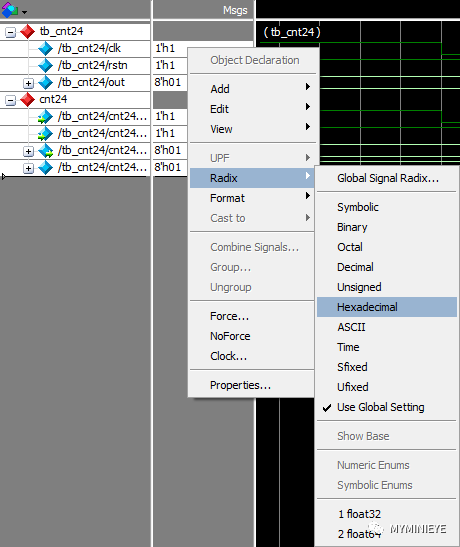

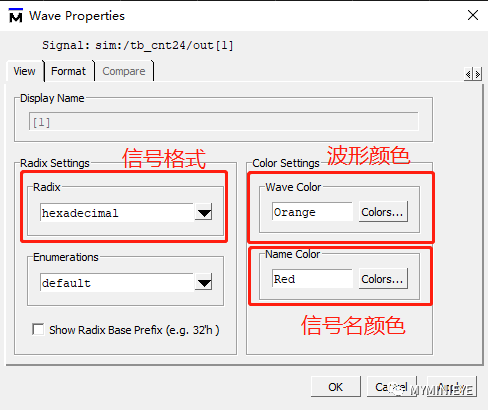

信號顯示屬性設置,選擇合適的顯示方式便于功能分析更好的找到信號并確定結果是否符合預期;

信號顯示進制設置:

例:選擇十六進制的信號格式:選中對應信號右鍵>Radix>hexadecimal

可修改為常用的信號格式:二進制Binary、八進制 Octal、十進制Decimal、無符號型Unsigned、十六進制Hexadecimal等;

也可在屬性Properties中修改信號格式,修改波形顏色,信號名顏色;

也可選擇需要修改的信號波形顏色及信號名顏色,這樣在仿真波形圖中能更容易分辨;

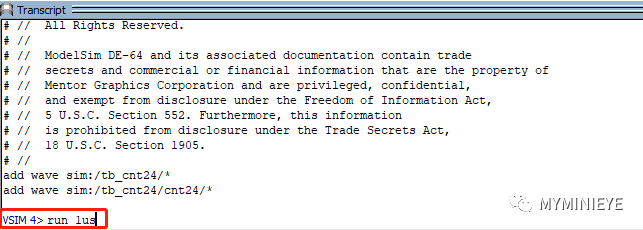

3、 運行仿真工程,并設置運行時間

可在Transcript命令行輸入run 1us命令,運行 1us 時間,也可運行其他時間

也可點擊下圖中輸入需要運行波形的時間,然后點擊圖中的小圖標。

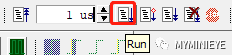

4波形界面調整

下圖為波形界面常用的控制圖標解析;

自此Modelsim將RTL代碼轉化為波形的功能完成,仿真后續內容需要自行根據實際module功能進行波形分析。

編輯:hfy

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

仿真

+關注

關注

50文章

4041瀏覽量

133414 -

波形

+關注

關注

3文章

378瀏覽量

31506 -

ModelSim

+關注

關注

5文章

174瀏覽量

47122

發布評論請先 登錄

相關推薦

FPGA開發:modelsim仿真流程及波形

FPGA開發:modelsim仿真流程及波形

評論