Video Frame Buffer IP 簡(jiǎn)介

Video Frame Buffer Read/Write IP 支持您將視頻數(shù)據(jù)從存儲(chǔ)器域(AXI4 存儲(chǔ)器映射接口)遷移到 AXI4-Stream 接口,或反之亦然。

從更高層次來(lái)看,它的作用與我們?cè)谙惹耙曨l系列(視頻系列 24、視頻系列 25、視頻系列 26 等)中所使用過(guò)的 AXI VDMA IP 并無(wú)差異。

那么為什么要使用 Video Frame Buffer IP 核而不是 AXI VDMA IP 呢?

答案就記錄在(賽靈思答復(fù)記錄 72543)中。究其本質(zhì),AXI VDMA IP 從 AXI4-Stream 接口提取字節(jié),并直接將其移植到存儲(chǔ)器中,無(wú)關(guān)乎視頻數(shù)據(jù)格式。

Video Frame Buffer 必須關(guān)注傳入傳出存儲(chǔ)器的數(shù)據(jù)格式。根據(jù)所選格式,它能以不同方式將數(shù)據(jù)存儲(chǔ)在存儲(chǔ)器中。這對(duì)于 Linux 應(yīng)用非常實(shí)用。

比如,V4L2 格式 YUYV 和 UYVY 都表示 YUV4:2:2 8 位,唯一差別就在于兩者在存儲(chǔ)器中的存儲(chǔ)方式。

因此,建議針對(duì)新設(shè)計(jì)采用 Video Frame Buffer IP。

如需了解有關(guān) Video Frame Buffer Read/Write IP 的詳情,請(qǐng)參閱 (PG278)。

為 Video Frame Buffer IP 生成設(shè)計(jì)示例

注意:下文是基于 2019.2 版本中提供的設(shè)計(jì)示例編寫的。

硬件 (Vivado 2019.2) 設(shè)計(jì)示例

要生成應(yīng)用設(shè)計(jì)示例的硬件部分 (Vivado Design),請(qǐng)遵循 (PG278) 的第 5 章中的步驟進(jìn)行操作。此處設(shè)計(jì)示例可用于 KC705、ZCU102、ZCU104 和 ZCU106 評(píng)估板。即使您沒有上述任意評(píng)估板,我也建議從設(shè)計(jì)示例開始實(shí)踐。這始終都是最佳的起點(diǎn)。

注意:要利用 Vivado WebPack 許可證生成設(shè)計(jì)示例,請(qǐng)使用 ZCU104 評(píng)估板作為起點(diǎn)開始操作。

設(shè)計(jì)示例分為兩種。一種用于 Video Frame Buffer Read IP,另一種用于 Video Frame Buffer Write IP。

我建議使用面向 Video Frame Buffer Write IP 的設(shè)計(jì)示例,因?yàn)?Video Frame Buffer Write IP 和 Video Frame Buffer Read IP 都囊括在其中。

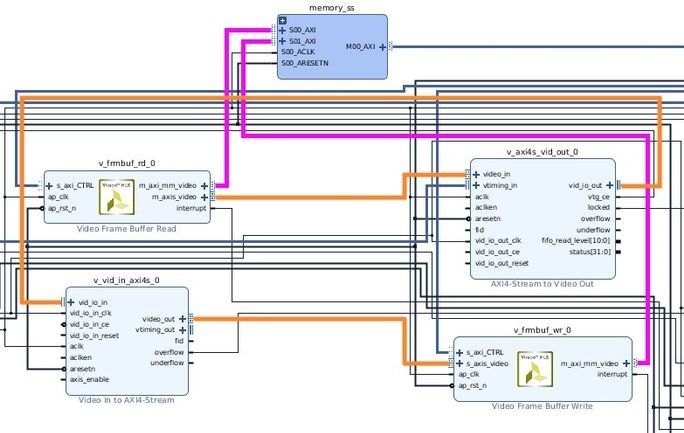

Video Frame Buffer Write IP 設(shè)計(jì)示例的硬件設(shè)計(jì)屬于非常基礎(chǔ)性的設(shè)計(jì)。

它使用 Video Frame Buffer Read IP 將數(shù)據(jù)從存儲(chǔ)器讀取到 AXI4-Stream 接口。

隨后,將其轉(zhuǎn)換為本地視頻,然后再使用 AXI4-Stream to Video Out IP 和 Video in to AXI4-Stream IP 重新轉(zhuǎn)換為 AXI4-Stream。

最后使用 Video Frame Buffer Write IP 將 AXI4-Stream 數(shù)據(jù)重新寫入存儲(chǔ)器。

我認(rèn)為對(duì)于此設(shè)計(jì),有兩個(gè)值得注意的要點(diǎn):

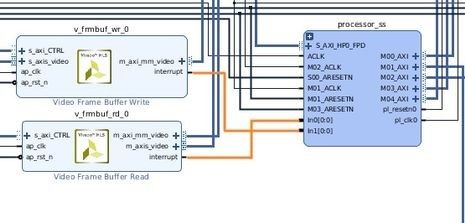

1. 上述兩個(gè) Video Frame Buffer IP(Read 和 Write)各自的中斷輸出都連接到處理器。這是前提條件。Video Frame Buffer 是基于中斷的 IP。

2. 而這兩個(gè) Video Frame Buffer IP 的復(fù)位輸入則連接至 AXI GPIO IP。這一點(diǎn)至關(guān)重要,因?yàn)樗С帜鷱奶幚砥鲌?zhí)行 IP 軟復(fù)位。就像所有 HLS IP 一樣,只要分辨率改變,就需要將 Video Frame Buffer 復(fù)位。

應(yīng)用示例 (Vitis 2019.2)

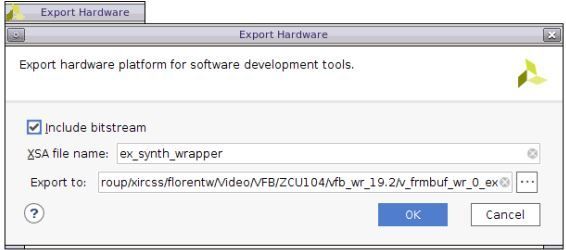

要生成應(yīng)用示例,在 Vivado 中,首先將硬件導(dǎo)出至賽靈思 Vitis(依次單擊 File > Export > Export Hardware …)。

確保在導(dǎo)出的硬件中包含比特流。這將創(chuàng)建一個(gè) XSA 文件。

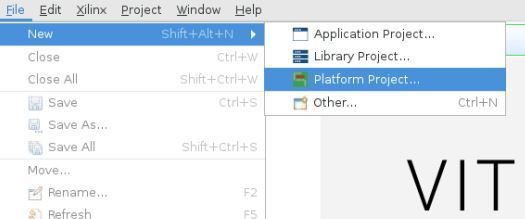

輸入您所選的平臺(tái)名稱(例如,v_frmbuf_zcu104_pfm),然后單擊 Next。

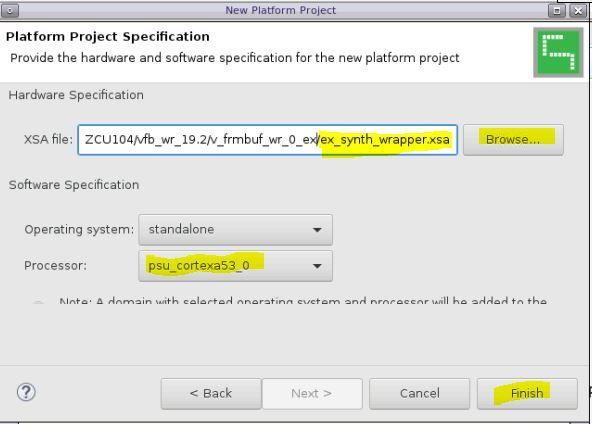

選擇從 Vivado 導(dǎo)出的 XSA 文件,確保已選中 A53 處理器,然后單擊 Finish。

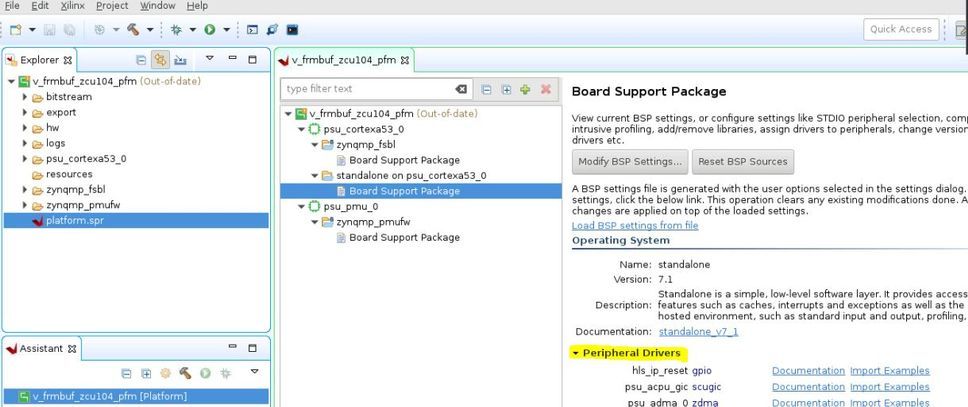

創(chuàng)建平臺(tái)后,單擊 psu_cortexa53_0 > standalone on psu_cortexa53_0 下的 Board Support Package,然后展開 Peripheral Drivers 部分。

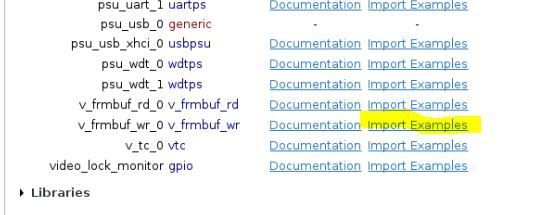

在 Peripheral Drivers 下,查找對(duì)應(yīng)于 Video Frame Buffer Write (v_frmbuf_wr) 的行,然后單擊 Import Examples。

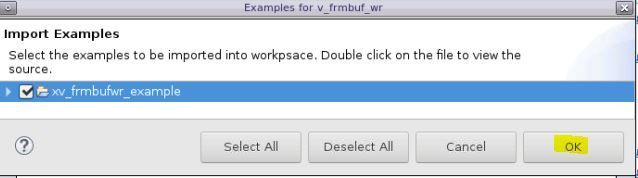

選擇示例 (xv_frmbufwr_example),然后單擊 OK。

運(yùn)行應(yīng)用示例

注意:以下步驟假定評(píng)估板已上電并且已通過(guò) UART 連接,BOOT 模式開關(guān)已設(shè)置為 JTAG 模式和 JTAG,并且已打開 UART 終端(如 Tera Term)供正確的 COM 端口使用。

單擊應(yīng)用并單擊錘子圖標(biāo)以構(gòu)建應(yīng)用:

要在硬件上啟動(dòng)應(yīng)用示例,請(qǐng)右鍵單擊設(shè)計(jì)應(yīng)用示例,并單擊 Run As > Run Configurations…

在 Create, manage, and run configurations 窗口中,右鍵單擊 Single Application Debug,然后單擊 New Configuration。

在配置窗口的 Target Setup 選項(xiàng)卡中,確保已啟用 psu_init(如果在 ZCU102、ZCU104 或 ZCU106 評(píng)估板上運(yùn)行)和 Program FPGA,然后單擊 Run。

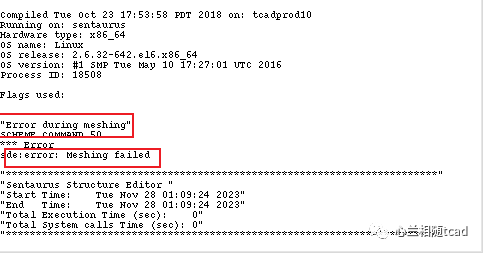

在 UART 終端中,可以看到此應(yīng)用正在嘗試不同的視頻分辨率和色彩空間組合。

在應(yīng)用運(yùn)行結(jié)束時(shí),可能會(huì)顯示部分測(cè)試失敗的原因(主要原因是硬件配置不支持)。

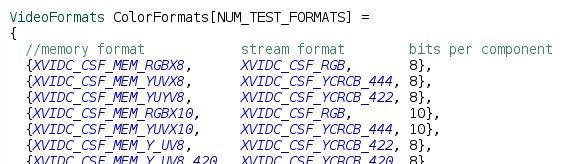

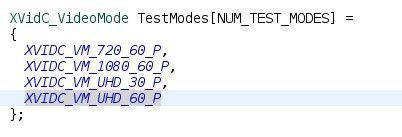

色彩空間和視頻分辨率在應(yīng)用中以 ColorFormats 和 TestModes 結(jié)構(gòu)來(lái)定義。

編輯:hfy

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7365瀏覽量

163081 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

130954 -

Video

+關(guān)注

關(guān)注

0文章

195瀏覽量

45050 -

Vitis

+關(guān)注

關(guān)注

0文章

145瀏覽量

7310

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

我用的是multisim14.0,因?yàn)槭?b class='flag-5'>初學(xué)者,仿真電路的時(shí)候找不到合適的模型,應(yīng)該怎么辦?

適合初學(xué)者的嵌入式項(xiàng)目有哪些?

國(guó)內(nèi)哪家的FPGA適合初學(xué)者

初學(xué)者請(qǐng)問各位大佬

請(qǐng)問初學(xué)者要怎么快速掌握FPGA的學(xué)習(xí)方法?

初學(xué)仿真常見的錯(cuò)誤

FPGA入門怎樣選擇合適的板子?

從入門到精通:學(xué)PLC之路詳解(附各種圖例)

OpenCV初學(xué)者如何提取這些不規(guī)則的ROI區(qū)域

面向CAN總線初學(xué)者的入門教程

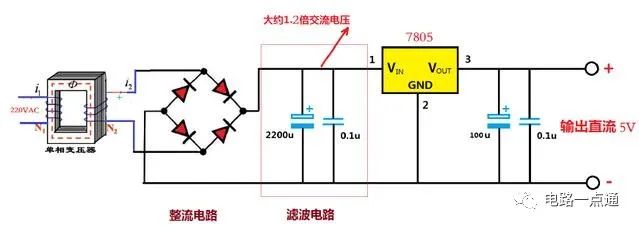

入門設(shè)計(jì)簡(jiǎn)易的5V直流電源

Video Frame Buffer IP初學(xué)者入門案例分析

Video Frame Buffer IP初學(xué)者入門案例分析

評(píng)論